Three-dimensional memory (3D-M) with integrated intermediate circuit chip

An intermediate circuit, three-dimensional storage technology, applied in circuits, electrical solid devices, electrical components, etc., can solve the problems of inability to reduce costs, increase costs, and troublesome intermediate circuit design.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In the present invention, " / " represents the relationship of "and" or "or". For example, a read / write voltage generator means that it can generate only read voltages, or only write voltages, or both read and write voltages; an address / data converter means that it can only convert addresses, or only data, or both Convert address and voltage.

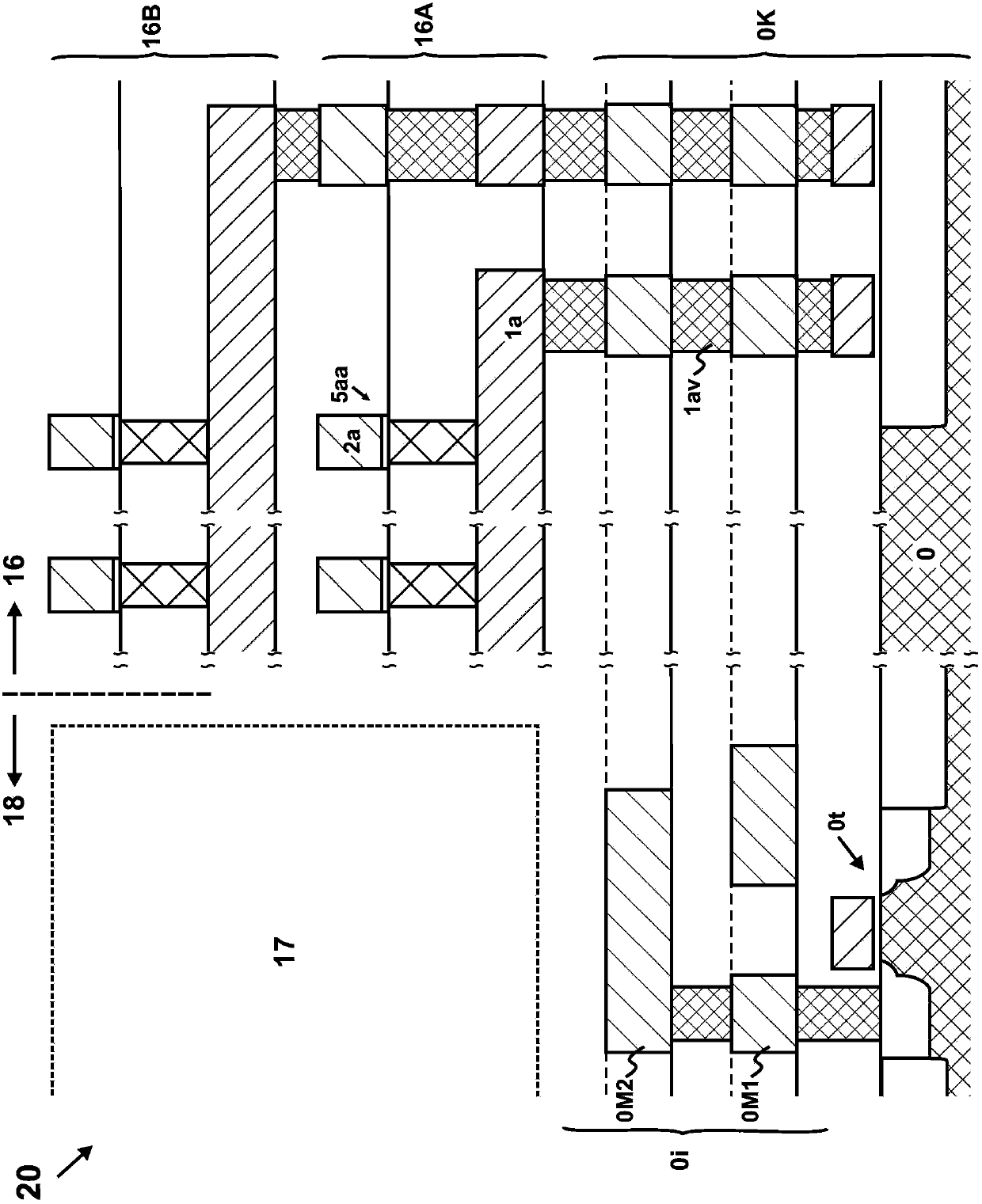

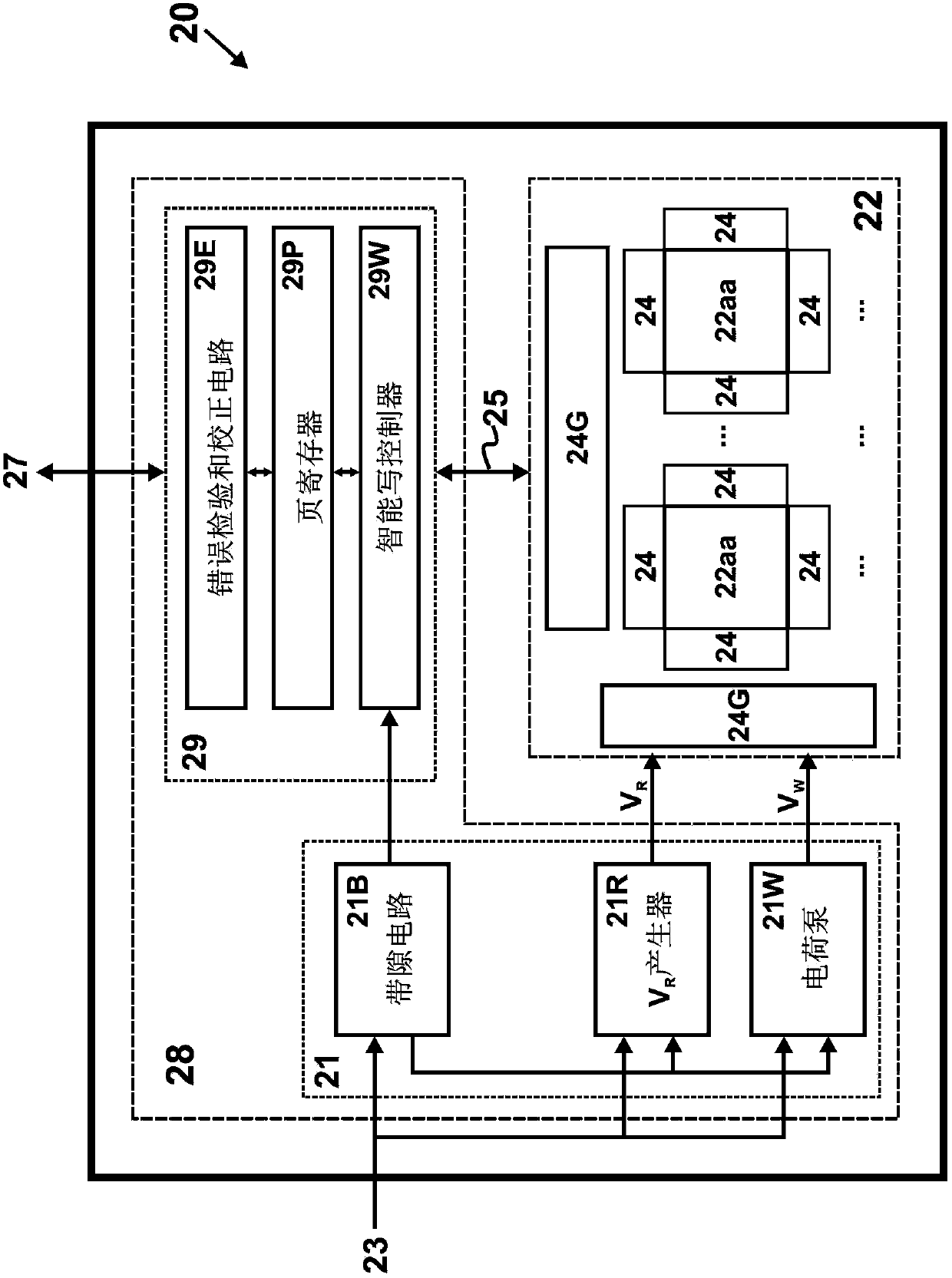

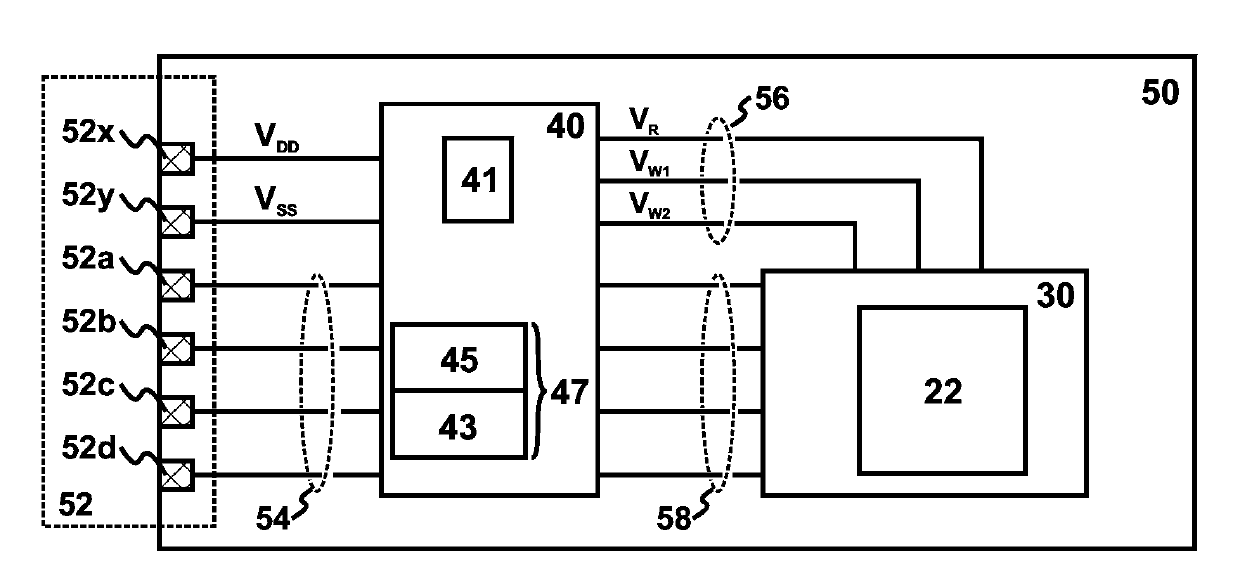

[0028] In the present invention, the intermediate circuit refers to a circuit between the 3D-M core area and the host, which implements voltage, address or / and data conversion between the host and the 3D-M core area. For example, it will come from an external voltage from the host (i.e. supply voltage V DD ), external address (that is, logical address) and external data (that is, logical data) are converted into the internal voltage of the 3D-M core area (that is, the read voltage V R and write voltage V W ), internal address (that is, physical address), and internal data (that is, physical data). Intermediate circuit component...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com