Cutting method of lower layer metal wiring

A technology of metal wiring and cutting method, which is applied in the manufacturing of electrical components, electric solid-state devices, semiconductor/solid-state devices, etc., can solve the problems of difficult removal of metal wire redeposition, inability to accurately observe, and incorrectly cut surrounding metal wires, etc. The effect of speeding up the debugging process and failure analysis, improving the efficiency and success rate of line repair

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

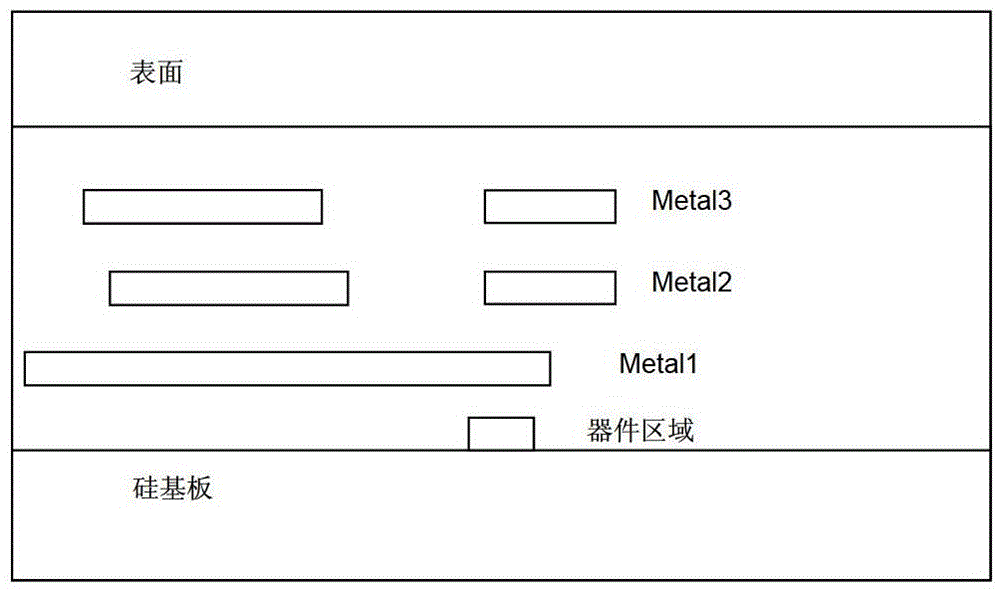

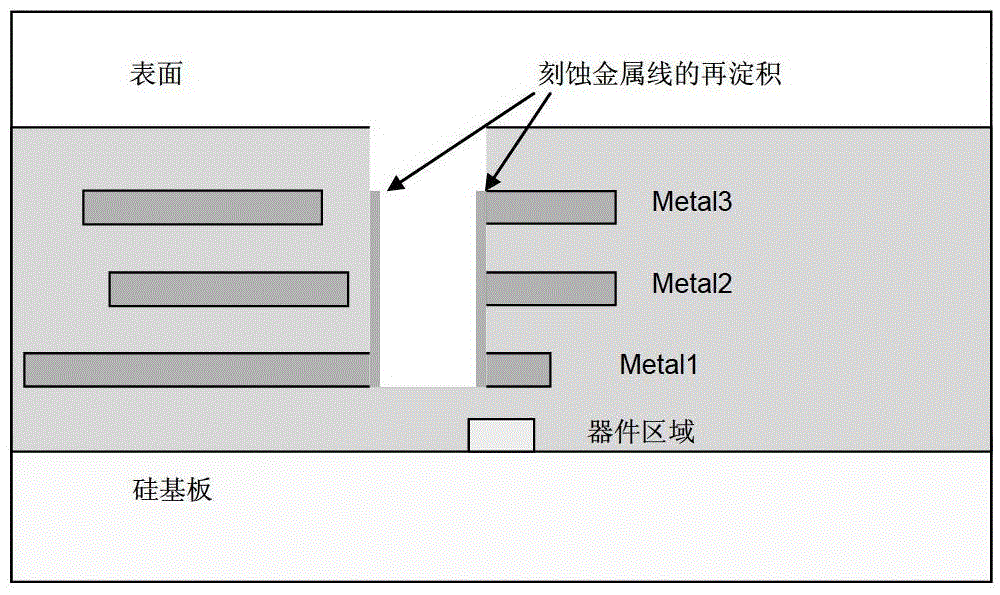

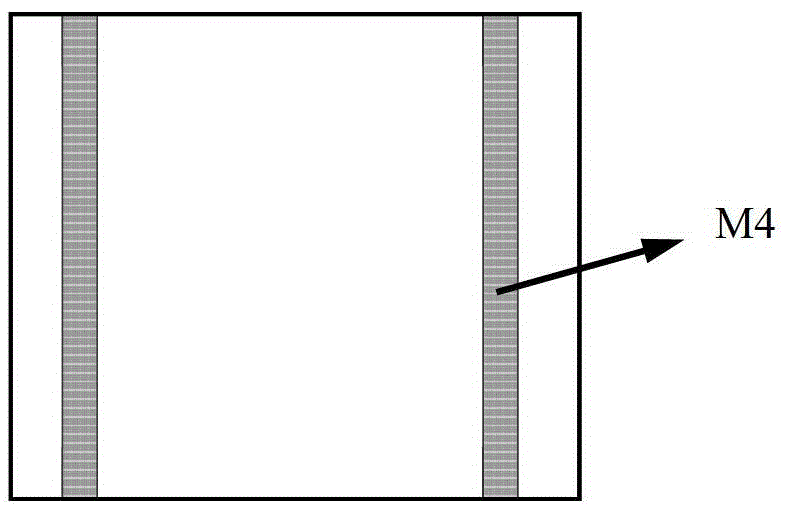

[0024] Focused Ion Beam (FIB): This equipment or technology uses the focused gallium positive ion beam as the incident particle (or primary ion) to hit the surface of the sample, and collects secondary electrons for imaging. Due to the large atomic weight of gallium ions , After acceleration, the kinetic energy is large, so it has a good sputtering etching function, and with a suitable gas system, it can realize auxiliary functions including selective etching and deposition of specific materials. The gas system it is often equipped with is Pt-Dep (platinum metal deposition system), IEE (selective enhanced etching), I-dep (insulating film deposition), etc.; when working, the gas is sprayed on the surface of the sample, and the ion beam bombards When FIB sets the pattern, it not only directly etches the sample surface, but also impacts some gas atoms on the sample surface, and a certain chemical reaction occurs together; by adjusting appropriate parameters, a layer of platinum me...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com