Semiconductor test structure and test method thereof

A test structure, semiconductor technology, applied in the direction of semiconductor/solid-state device testing/measurement, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problem of ineffective detection of double damascene structure defects, double damascene structure is easy to form defects, and affects SRAM Memory stability and other issues, to achieve the effect of simple test method, space saving and high efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

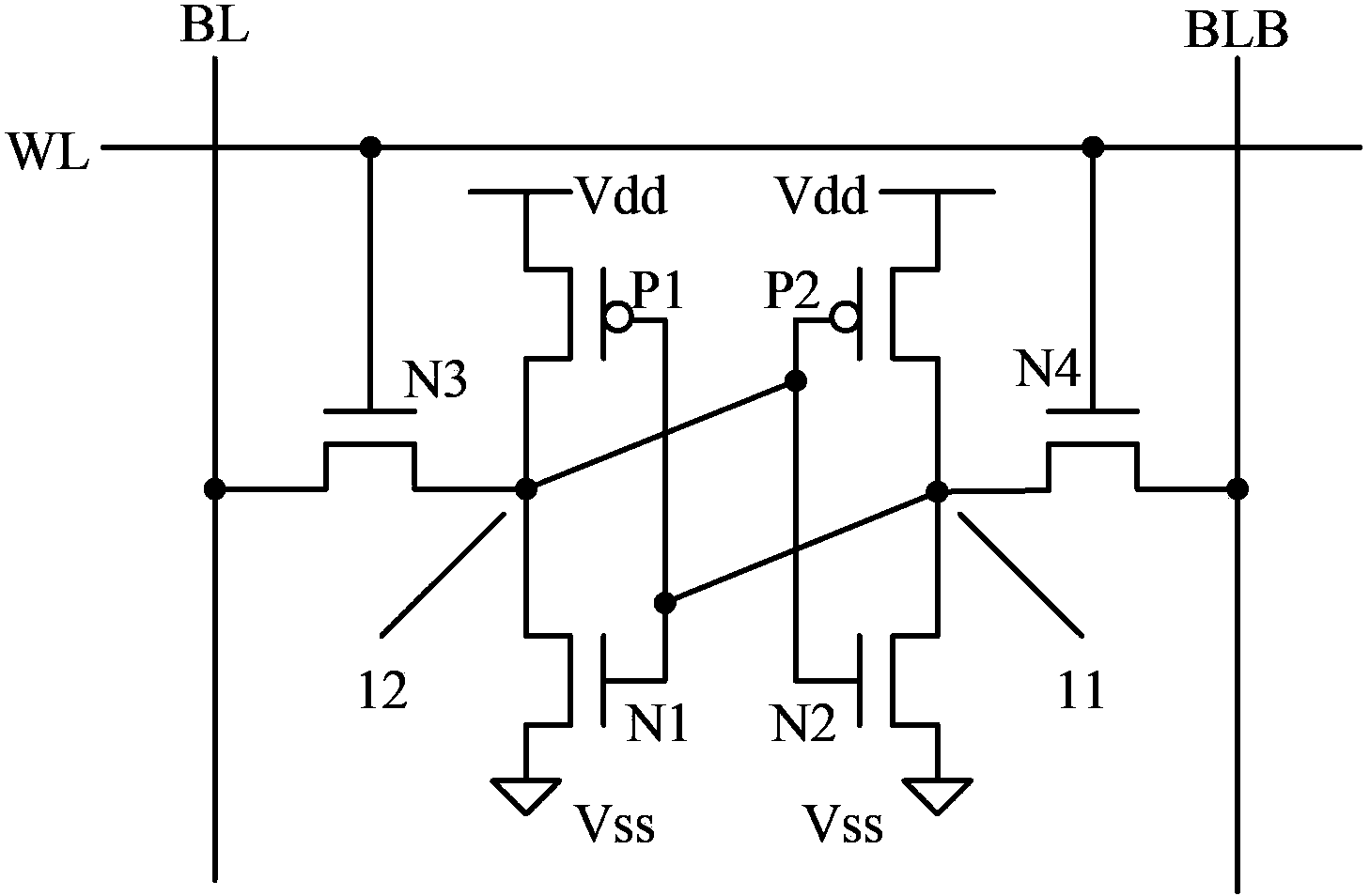

[0038] The inventor found in the existing process of making SRAM memory that the electroplating process is used to form a dual damascene structure for connecting metal interconnection lines, word lines and bit lines with the gate, source or drain of transistors in memory cells. At this time, due to the continuous reduction of feature size, it is easy to form defects such as voids in the dual damascene structure. The existence of defects such as voids will affect the electrical performance of the dual damascene structure, and ultimately affect the stability of the SRAM memory of the formed semiconductor device.

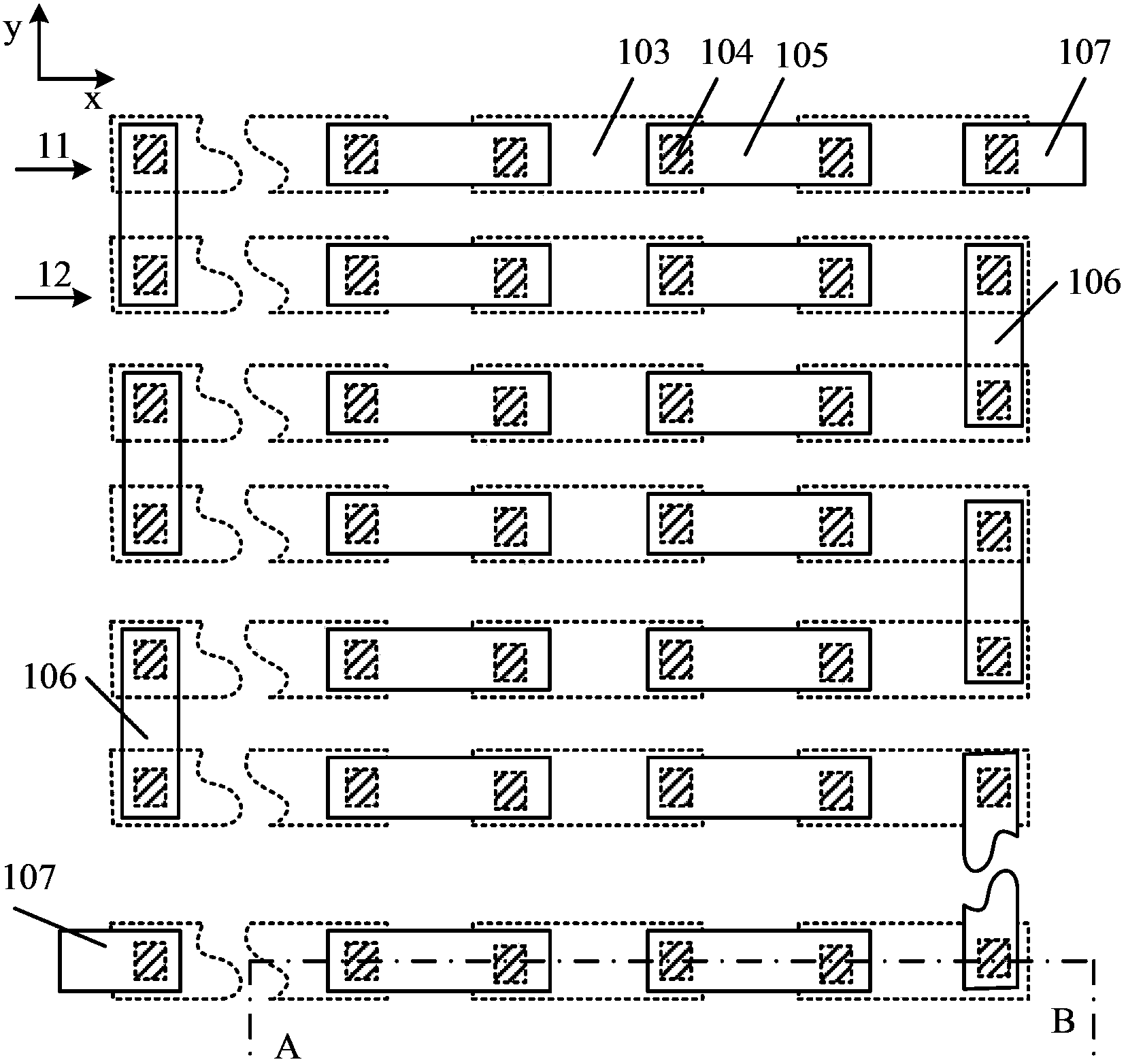

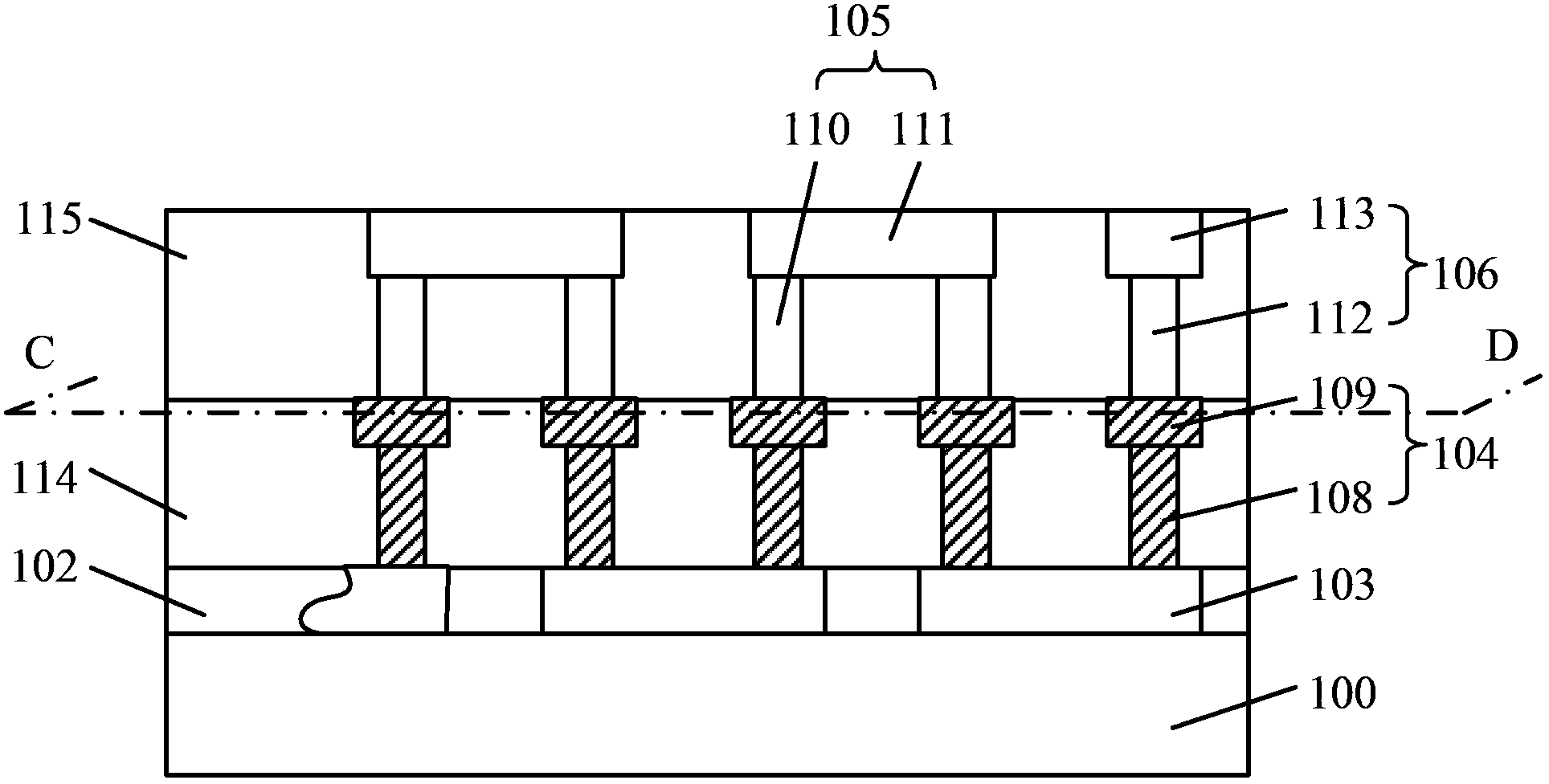

[0039] The inventors have further studied and found that when forming a dual damascene structure, it is necessary to form through holes and grooves connected to the through holes in the dielectric layer, and when filling metal copper in the grooves and through holes, the size and arrangement direction of the grooves, It will have a great impact on the filling performanc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More