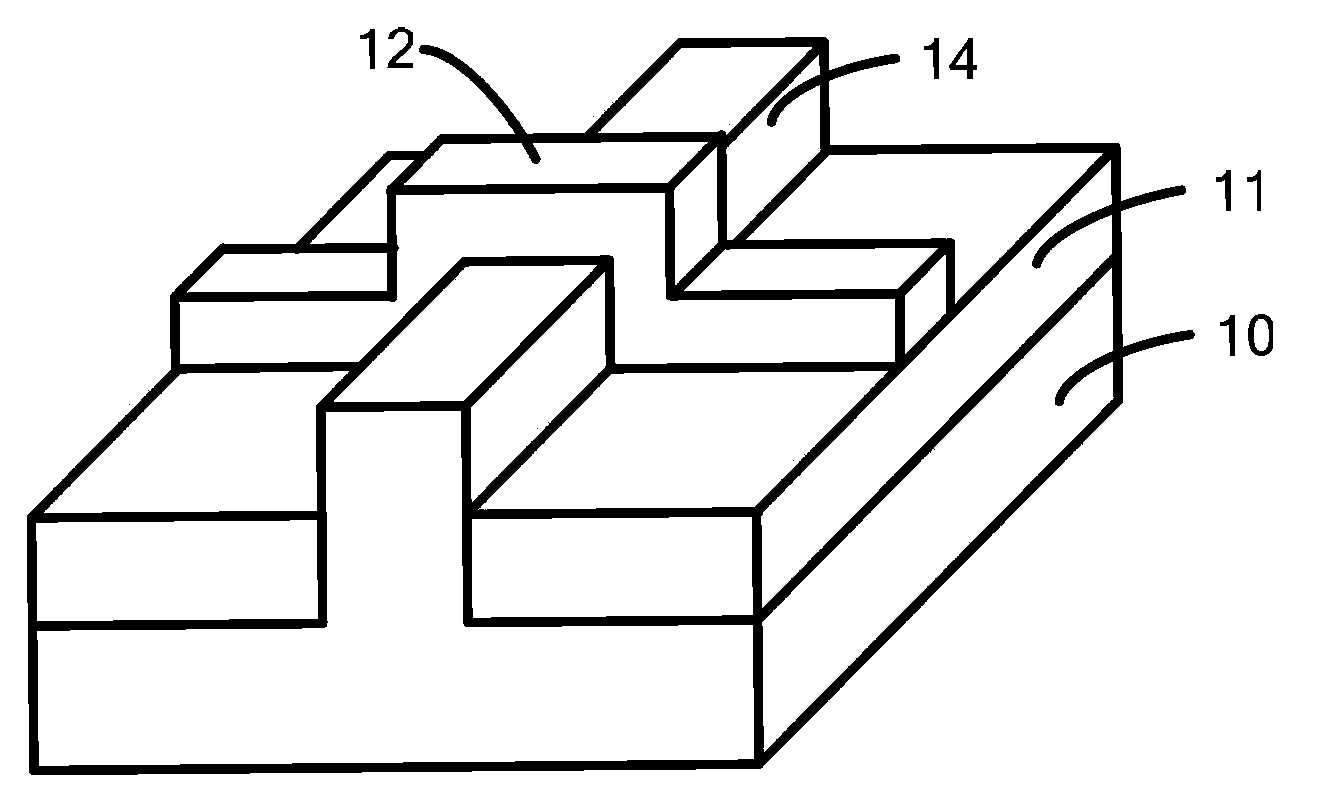

Forming method of fin-type field effect transistor

A fin-type field effect and transistor technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., and can solve problems such as high process costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] As mentioned in the background art, as the feature size of transistors shrinks continuously, the mobility of carriers also decreases, so that the saturation current of transistors decreases. However, the existing technology of using SiGe or SiC as the source and drain requires a large process cost.

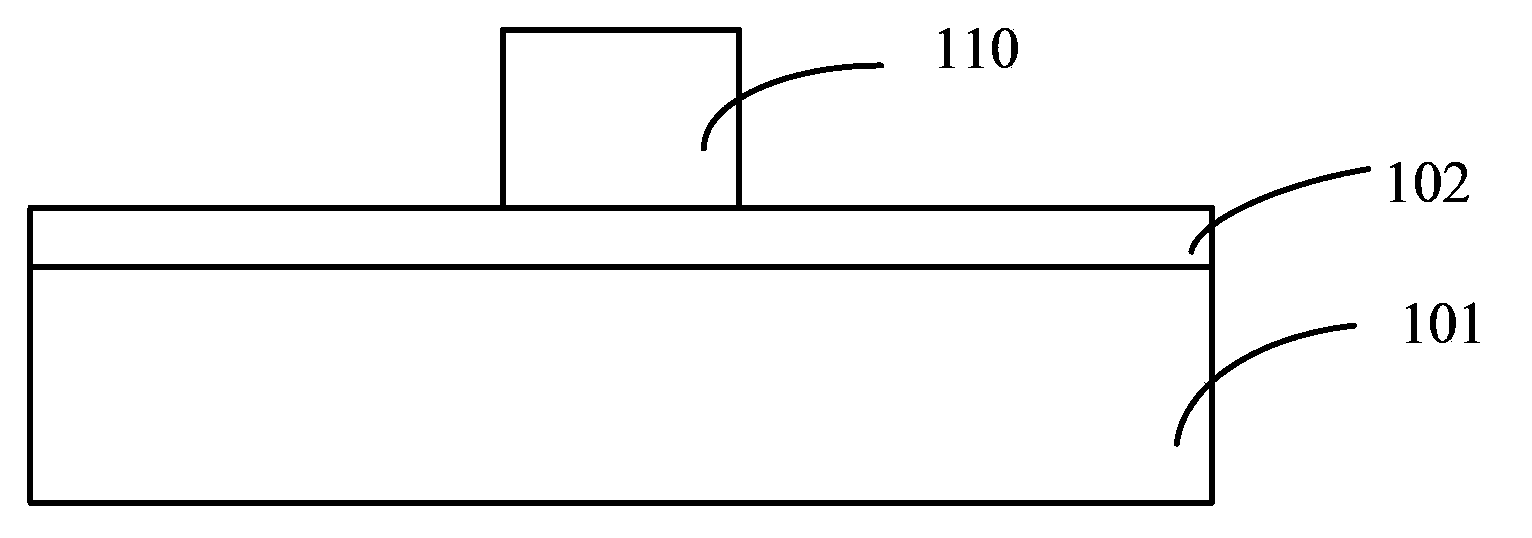

[0028] The forming method of the Fin Field Effect Transistor proposed by the present invention forms a polysilicon layer by annealing after forming an amorphous silicon layer in the source and drain regions, so as to generate tensile stress on the trench region, improve the mobility of electrons in the NMOS channel region, and improve the transistor performance. performance.

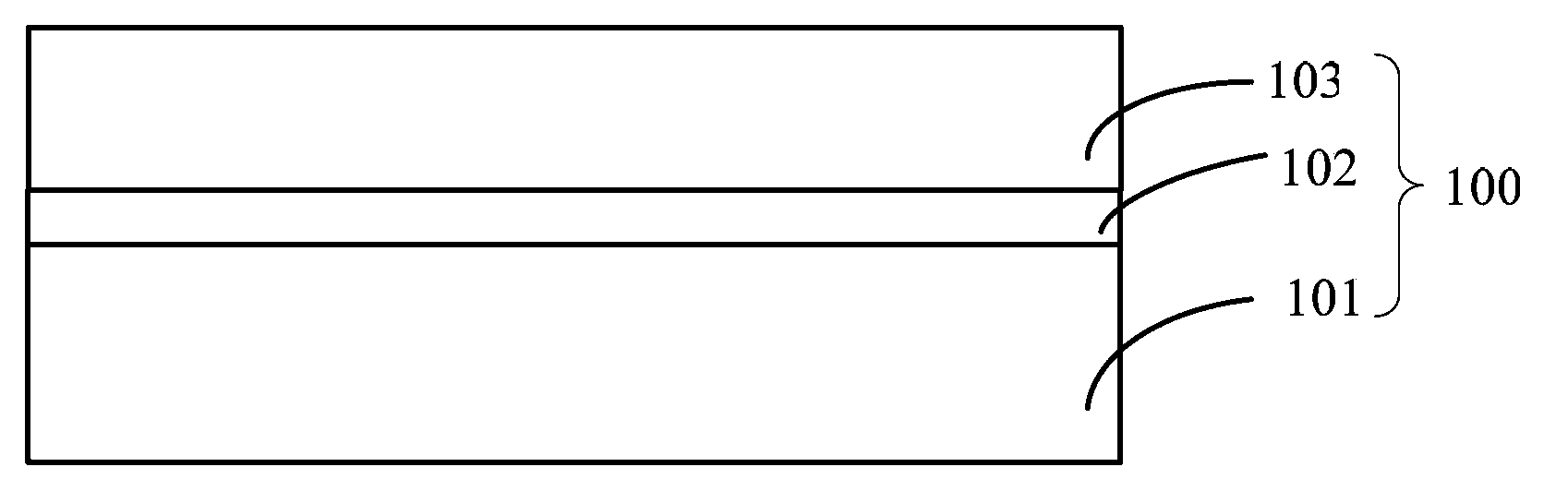

[0029] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings. The described embodiments are some, but not all, of the p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More