PID resistance crystalline silicon battery and preparation method thereof

A technology of crystalline silicon cells and electrodes, which is applied in circuits, electrical components, semiconductor devices, etc., can solve the problems of reduced photocurrent, high extinction coefficient of silicon nitride, and reduced cell efficiency. The method is simple, good resistance to PID, and low cost. cheap effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be described in detail below with reference to the accompanying drawings and in combination with embodiments.

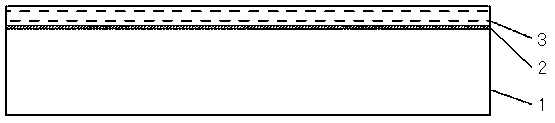

[0029] refer to figure 1 As shown, an anti-PID crystalline silicon battery includes a silicon dioxide layer 2 and a silicon nitride antireflection layer 3 covering a silicon substrate 1 in sequence. The silicon dioxide layer 2 has a thickness of 1-5 nm. The antireflection layer 3 of the silicon nitride layer has a thickness of 70-85nm.

[0030] A method for preparing an anti-PID crystalline silicon battery. After the silicon substrate 1 is cleaned, textured, diffused, dephosphorized silicon glass, and edge etched in the conventional process steps, the silicon substrate 1 is placed under a low-pressure ultraviolet mercury lamp. Continuous irradiation for 30 minutes.

[0031] The low-pressure ultraviolet mercury lamp can emit two kinds of ultraviolet light of different wavelengths at the same time, and integrates the ozone generatin...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More