A development platform for reconfigurable microcomputer protection based on fpga

A development platform and microcomputer protection technology, applied in computer control, instruments, simulators, etc., can solve the problems of occupying CPU running time and low system work efficiency, so as to improve work efficiency, improve anti-electromagnetic interference ability, and simplify circuits. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The technical scheme of the present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments, so that those skilled in the art can better understand the present invention and implement it, but the examples given are not intended to limit the present invention.

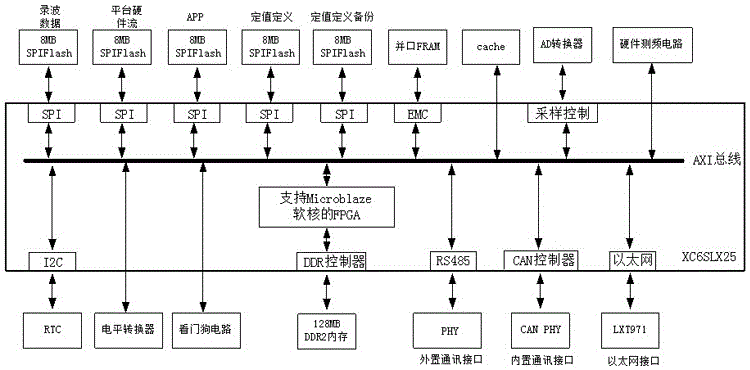

[0027] Such as figure 1 As shown, a development platform based on FPGA reconfigurable microcomputer protection, including FPGA chip supporting Microblaze soft core, internal memory, external memory, parallel interface FRAM (ferroelectric memory), cache, AD converter, hardware frequency measurement circuit, watchdog circuit, level shifter, real-time clock (RTC), external communication interface, built-in communication interface and Ethernet interface. In addition to the internal memory, all peripheral devices are interconnected with the central processing unit through the AXI64-bit bus. Several peripheral devices use serial buses to save size and c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com