Ultra-low power pseudo-differential structure non-volatile memory compatible with standard cmos process

A non-volatile, ultra-low power consumption technology, applied in the field of microelectronics, can solve the problems of small area, high integration, high power consumption, etc., and achieve the effect of high integration density, high reliability and low high voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] An ultra-low power consumption non-volatile memory with a pseudo-differential structure compatible with a standard CMOS process will be described in detail below with reference to the accompanying drawings.

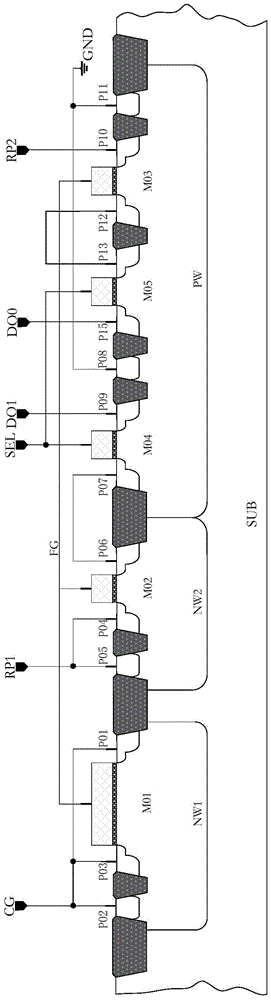

[0029] refer to Figure 7 , the present invention is made up of exactly the same storage unit, and the storage unit of this example is 16, namely memory capacity is 16 bits, but is not limited to 16 bits, and actual storage capacity can be increased according to demand, and can utilize block storage array to Increase storage capacity. from Figure 7 It can be seen that in each row, the control ports CG of all memory cells are connected together; all the selection ports SEL are connected together; in each column, all the first read ports RP1 are connected together; all the second read ports Take port RP2 and connect together, thus forming the structure of the whole memory.

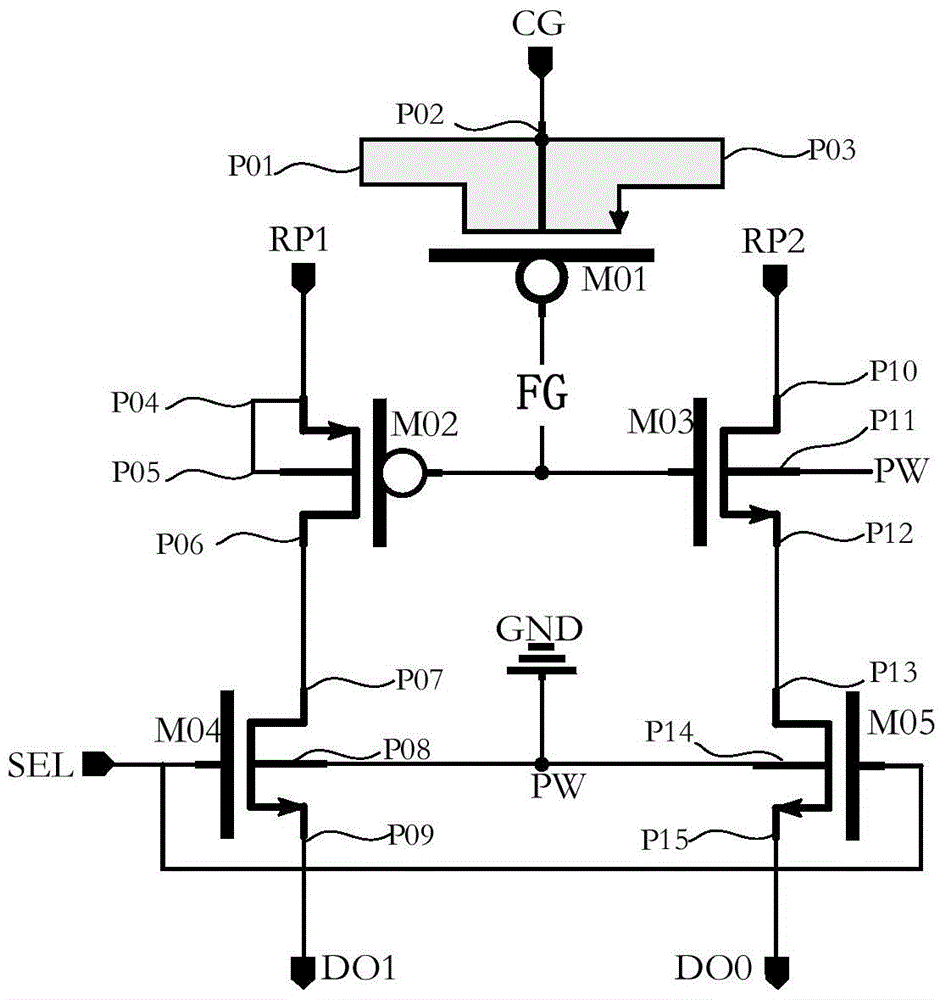

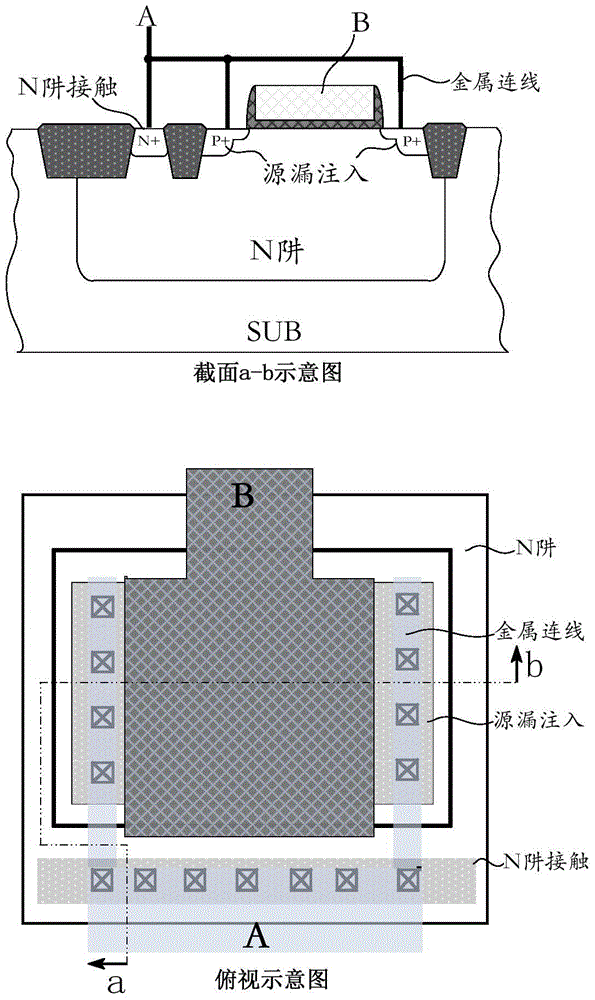

[0030] refer to figure 1 , each memory cell includes only 5 transistors, all transistors...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More