Method for forming semiconductor structure

A semiconductor and bulk substrate technology, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problem of inconsistent electrical properties of several fin field effect transistors, difficult to control the thickness and size of the gate structure, and difficult performance of semiconductor devices. Control and other issues to achieve the effect of improving stability, uniform thickness, and uniform thickness and size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] As mentioned in the background, the thickness of the gate structure on the top surface of the fin in the prior art is non-uniform and imprecise.

[0036] In one embodiment, the formation process of forming the high-K metal gate structure on the surface of the fin is as follows: Figure 2 to Figure 4 shown.

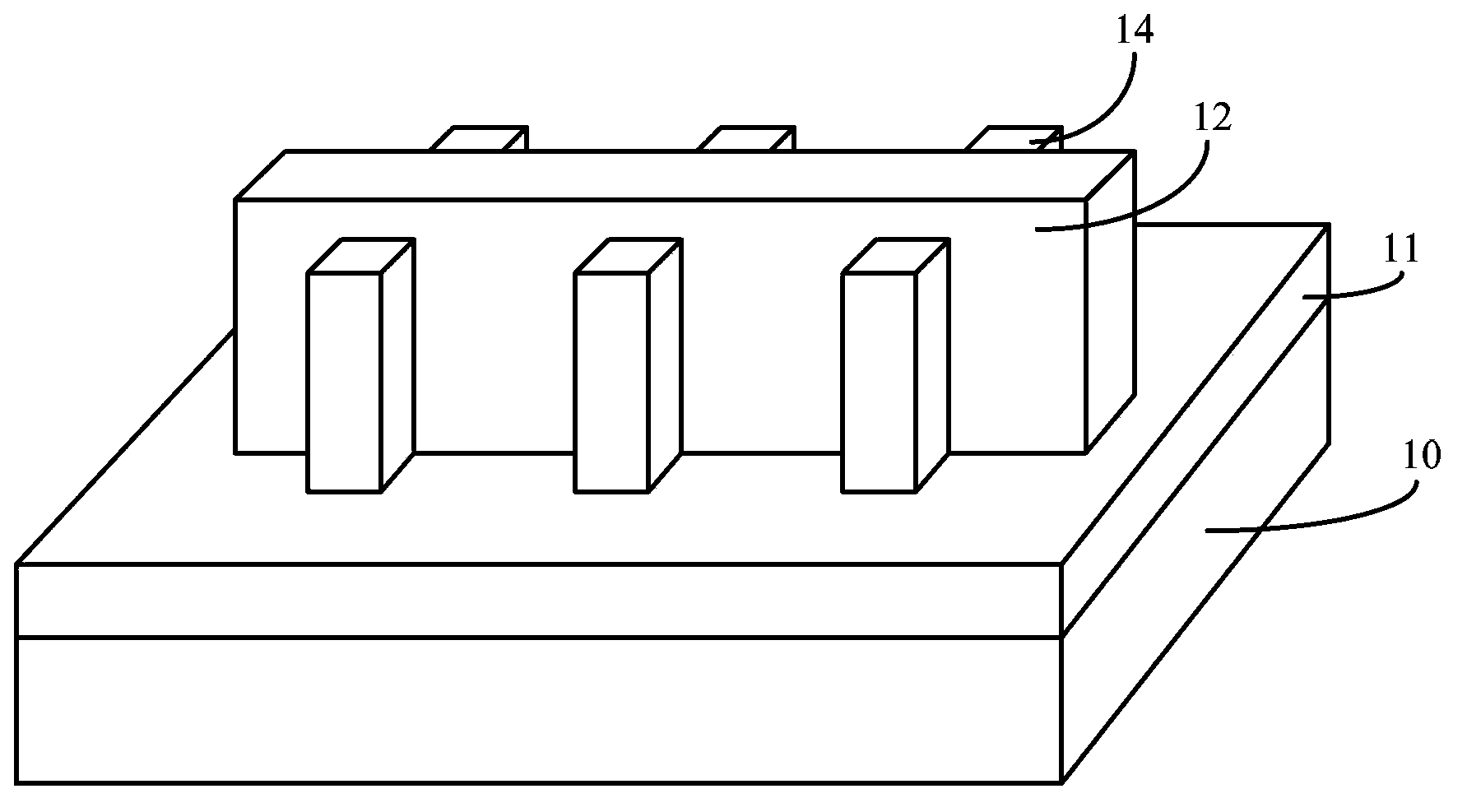

[0037] Please refer to figure 2 , providing a semiconductor substrate 10, a protruding fin 14 located on the semiconductor substrate 10, and a dielectric layer 11 covering the surface of the semiconductor substrate 10 and part of the sidewall of the fin 14, on the surface of the dielectric layer 11 and the fin The dummy gate layer 15 is deposited on the sidewalls and top surfaces of fins 14 , and the dummy gate layer 15 fills the openings (not shown) between adjacent fins 14 .

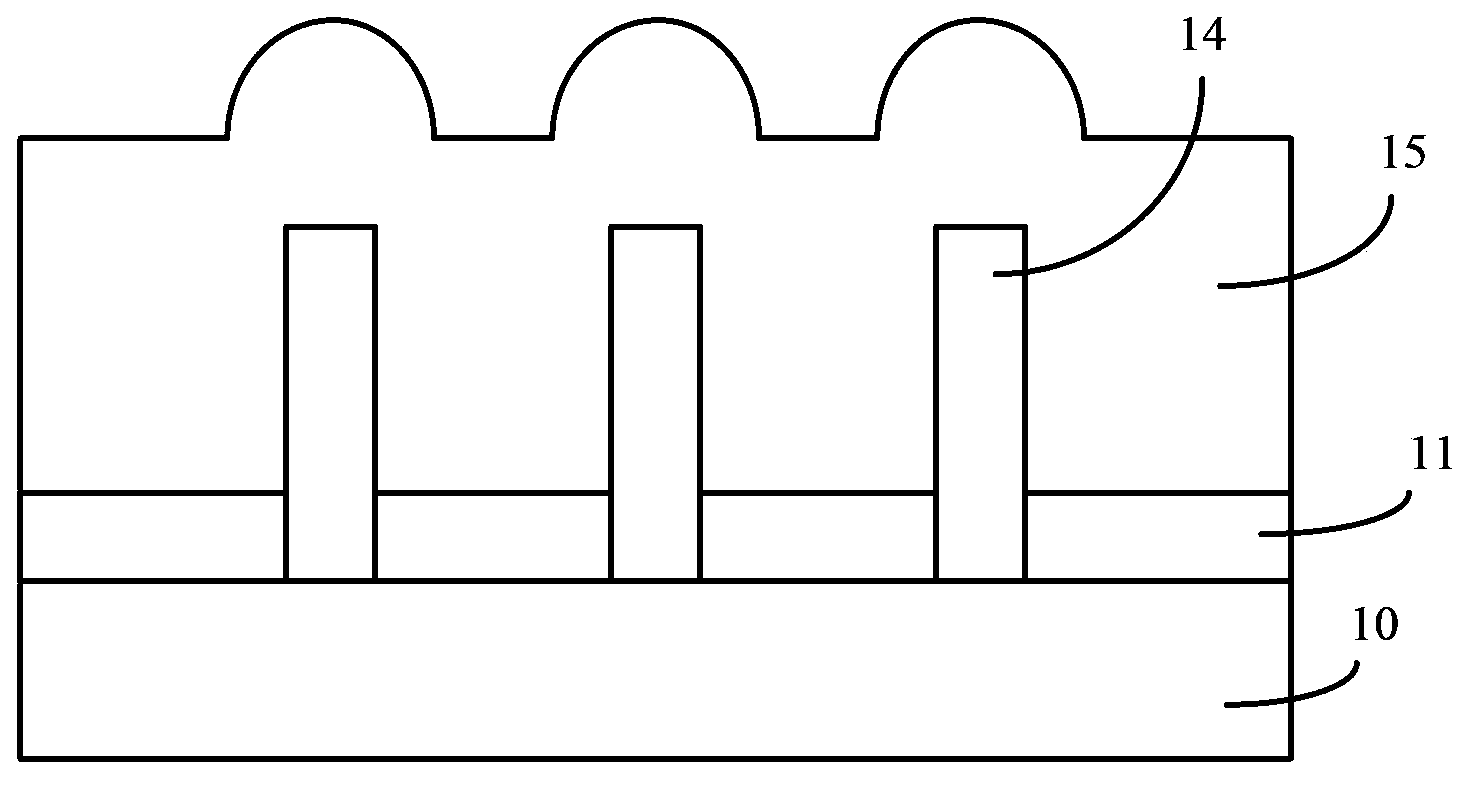

[0038] Please refer to image 3 , using a chemical mechanical polishing process to planarize the dummy gate layer 15 .

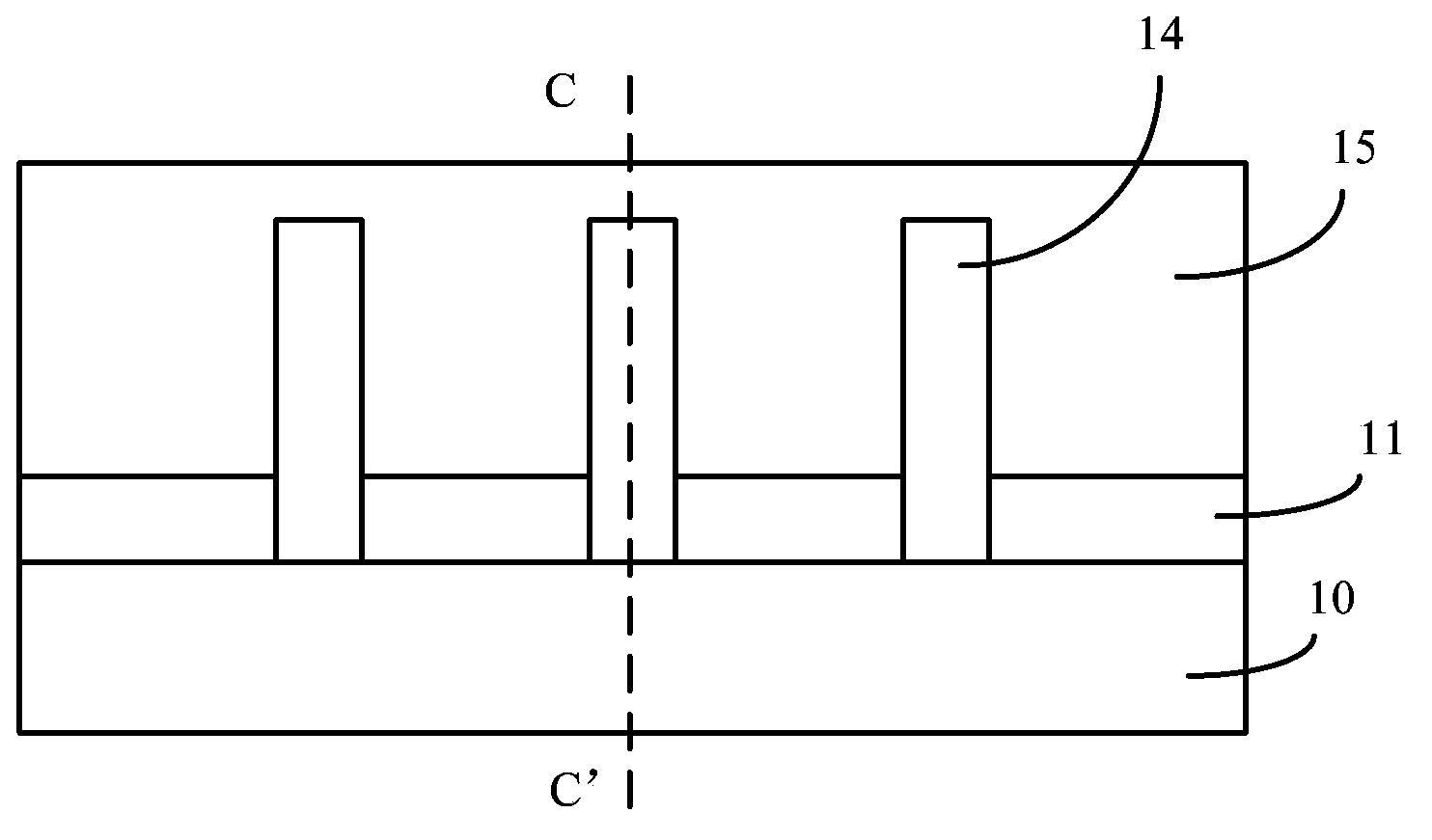

[0039] Please refer to Figure 4 , Figure 4 based on image ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More