Routing adaptive asynchronous 2d-torus network-on-chip system and its design method

A 2d-torus, network-on-chip technology, applied in the transmission system, digital transmission system, data exchange network, etc., can solve the problems of not being able to dynamically adjust the routing direction according to the congestion state in real time, and waste routing resources.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

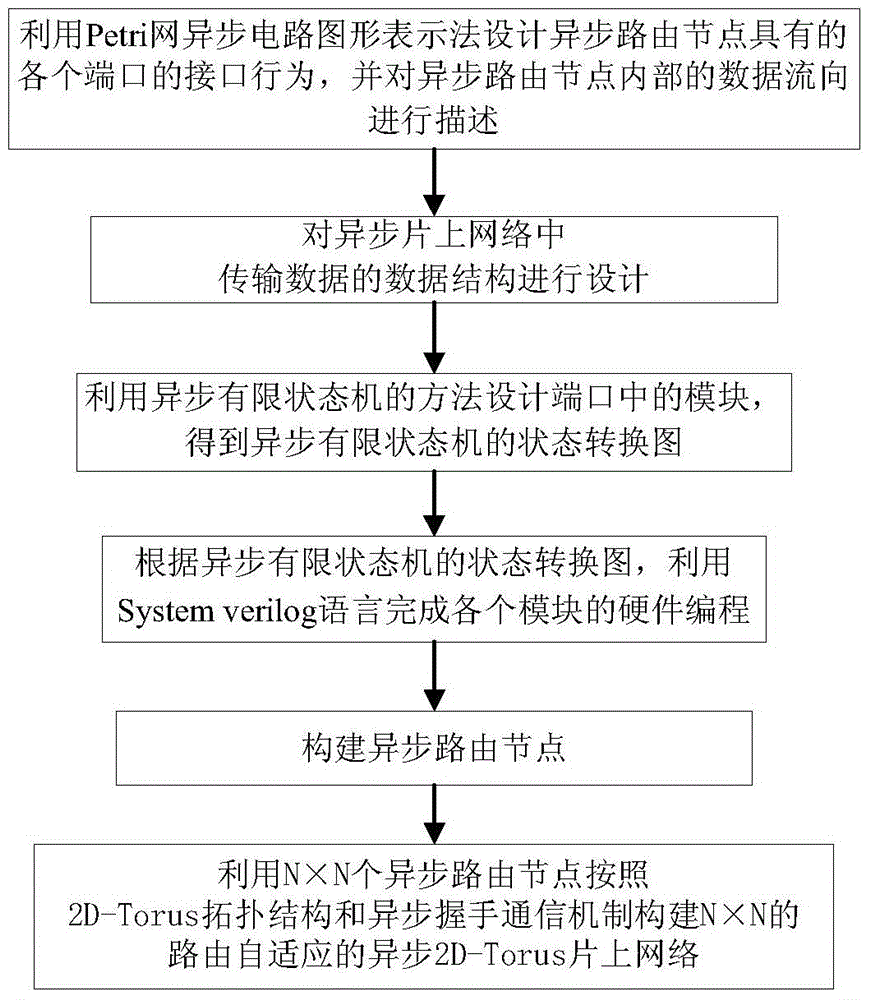

[0057] The specific implementation of the present invention will be described in detail below in conjunction with the accompanying drawings.

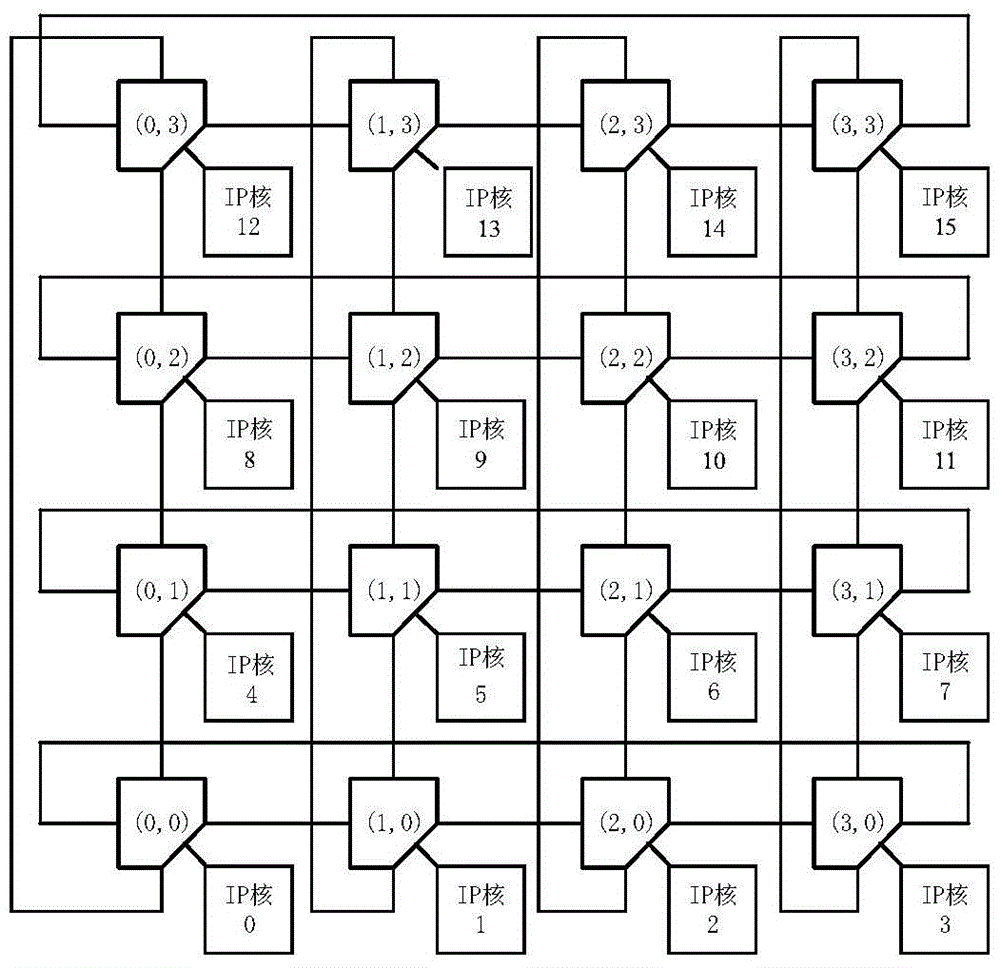

[0058] The route-adaptive asynchronous 2D-Torus network-on-chip of this embodiment adopts a 4×4 structure, such as figure 1 As shown, it includes: 16 asynchronous routing nodes and 16 IP cores, of which 16 asynchronous routing nodes, according to the 2D-Torus topology structure, adopts the asynchronous handshake communication mechanism to form a 4×4 asynchronous 2D-Torus network on chip. One IP core is mounted on each asynchronous routing node; the asynchronous routing node is used to send data from the corresponding output port to the adjacent node according to the information carried in the data, until the current asynchronous routing node is the destination address asynchronous routing node;

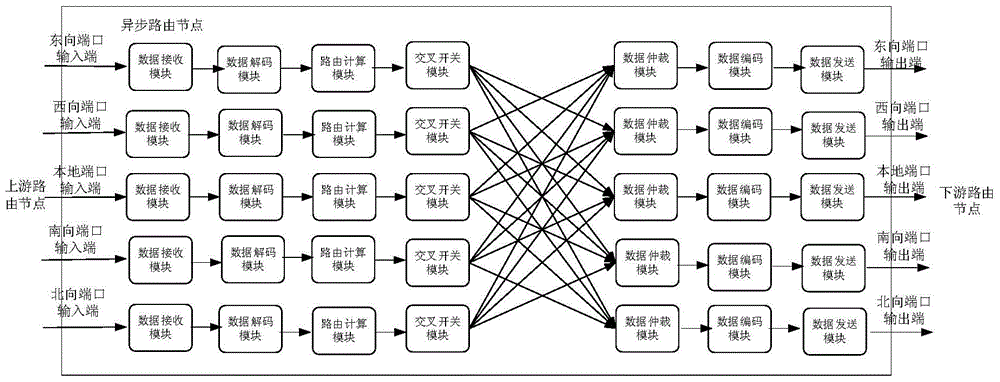

[0059] The asynchronous routing node in this embodiment, such as figure 2 As shown, the asynchronous routing node has five ports including ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More