Three-dimensional carbon nano wire transistor structure and preparation method thereof

A carbon nanowire and transistor technology, applied in the field of three-dimensional carbon nanowire transistor structure and its preparation, can solve the problems of inability to manufacture three-dimensional transistors, limit the area utilization rate of silicon wafers, etc., so as to improve the area utilization rate, reduce occupation, and ensure The effect of practicality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

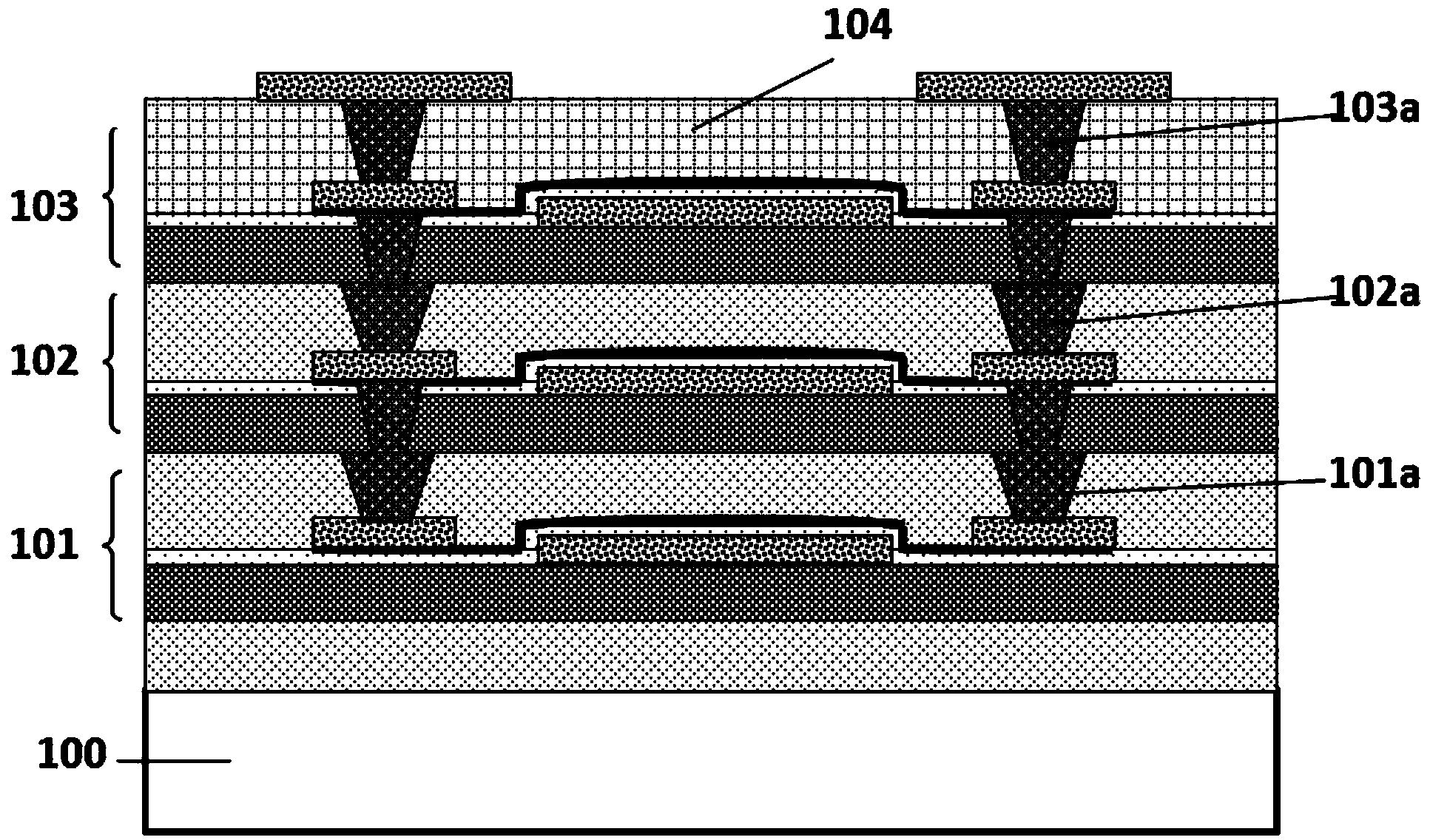

[0032] The invention provides a three-dimensional carbon nanowire transistor structure and a preparation method thereof, which can manufacture smaller transistors to increase transistor density, increase the width-to-length ratio of transistors, and improve the area utilization rate of silicon wafers.

[0033] Such as figure 1Shown is the cross-sectional structure of the three-dimensional carbon nanowire transistor structure provided by the present invention. Although the illustration only shows the superposition of three device layers, in actual operation, more device layers can be added according to product needs, and the device width-to-length ratio can be increased by connecting more carbon nanowire transistors in parallel. In the figure, 101, 102 and 103 are the device layers arranged with the same carbon nanowire transistors, through the through holes 101a, 102a, the interconnection between the corresponding poles of the carbon nanowire transistors in the upper and lower...

Embodiment

[0035] Hereinafter, the preparation method of the three-dimensional carbon nanowire transistor structure provided by the present invention will be described in detail.

[0036] In order to avoid tedious repetition, this embodiment only selects a three-dimensional carbon nanowire transistor structure with two device layers for detailed introduction.

[0037] Such as Figure 2a As shown, an insulating dielectric layer SiO2 is grown on a silicon substrate 100 by a thermal oxidation process, with a thickness of 30-50 nanometers. Since the carbon nanowire transistor provided by the present invention is different from traditional transistors, it is not necessary to connect the source, drain, gate, and three electrodes to the substrate, so the silicon substrate 100 is the supporting substrate here. Because in actual application, the structure of the present invention may share the substrate with other devices, and since the present invention uses a back gate design, the deposition o...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More