High-transfer-characteristic low-stray-capacitance embedded grid insulation tunneling enhanced transistor

A low parasitic capacitance, high transfer technology, applied in the direction of circuits, electrical components, semiconductor devices, etc., can solve the problems of increasing production costs, no improvement, large gate to source, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0044] Below in conjunction with accompanying drawing, the present invention will be further described:

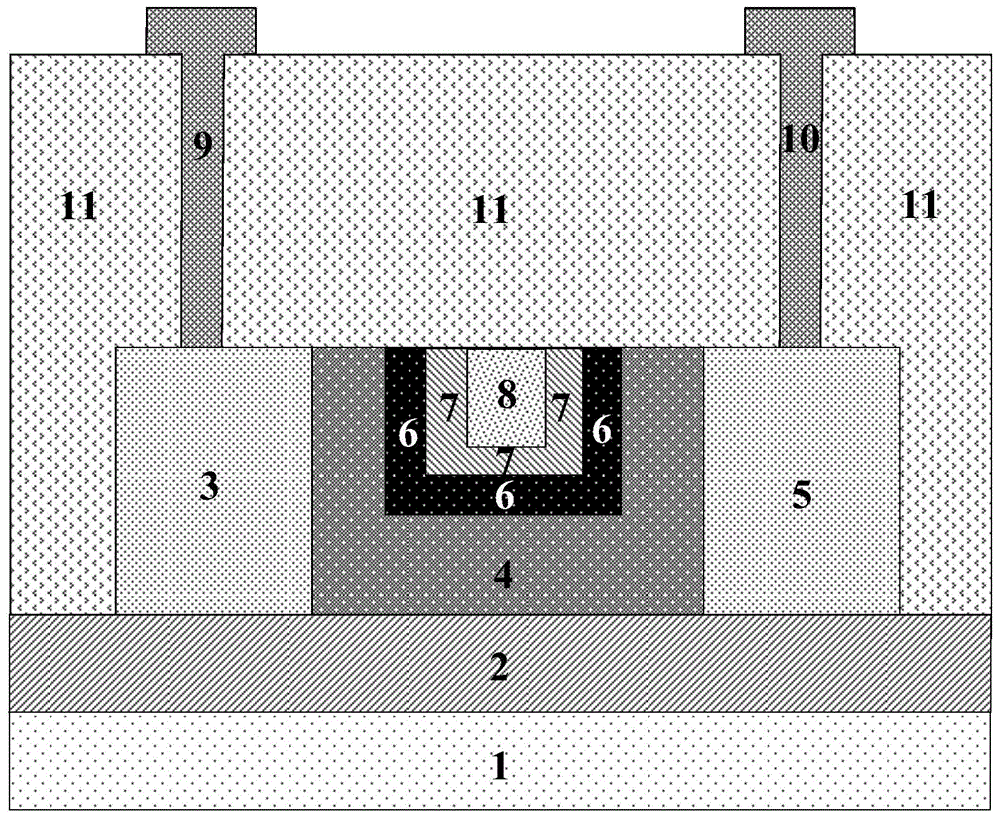

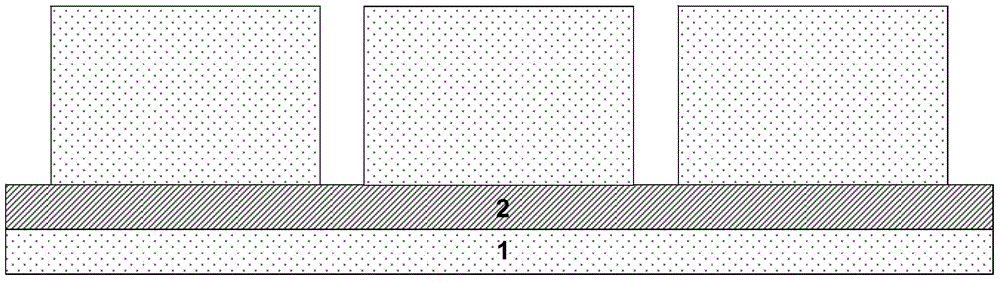

[0045] Such as figure 1 It is a schematic diagram of a two-dimensional structure of an embedded gate insulation tunneling enhanced transistor with high transfer characteristics and low parasitic capacitance in the present invention formed on a bulk silicon substrate; it specifically includes a single crystal silicon substrate 1; a wafer insulating layer 2; an emitter region 3; Region 4; Collector region 5; Conductive layer 6; Tunneling insulating layer 7; Gate electrode 8; Emitter 9; Collector 10;

[0046] High transfer characteristics and low parasitic capacitance Embedded gate insulation tunneling enhancement transistor, using a bulk silicon wafer containing only a single crystal silicon substrate 1 as the device substrate, or using a single crystal silicon substrate 1 and a wafer insulating layer at the same time 2 of the SOI wafer as the substrate for generating devic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More