Method for interconnecting back faces of wafer level chips during packaging

A wafer-level chip and backside technology, which is applied in wafer-level chip packaging to form openings exposing solder pads, and in the field of backside interconnection, can solve the problem of small area of connectable lines, weak structure strength of solder pads and metal lines, and electrical continuity. The performance is not reliable enough to achieve the effect of increasing the contact area and improving the circuit conduction performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

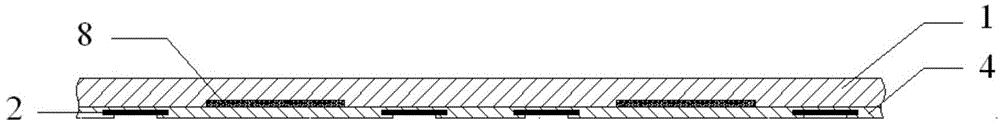

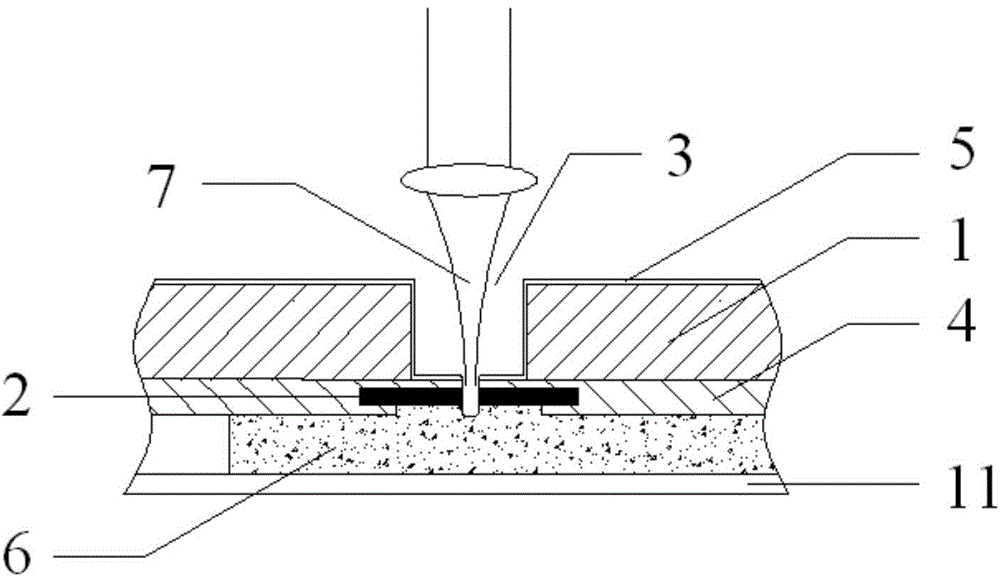

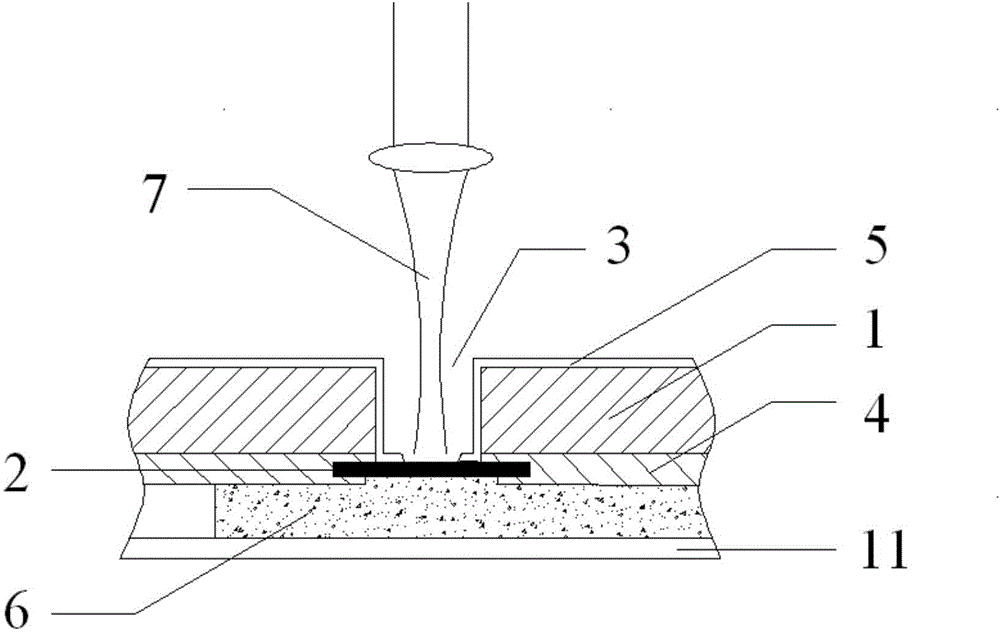

[0038] Such as image 3 , Figure 4 with Figure 5 As shown, a method for forming an opening for exposing the bonding pad 2 in a wafer-level chip package includes the following steps:

[0039] a. Provide a wafer with several chip units. The chip units include a substrate 1 and a dielectric layer 4 on the front surface of the substrate 1. The front surface of the substrate 1 is provided with a component area 8, and the component area 8 A number of solder pads 2 are provided on the periphery, and the solder pads 2 are located in the dielectric layer 4, and the component area 8 is electrically connected to the solder pads 2 on the periphery;

[0040] b. A first opening 3 opposite to the solder pad 2 is formed on the back of the substrate 1, and the first opening 3 extends from the back of the substrate 1 to above the corresponding solder pad 2;

[0041] c. Laying an insulating layer 5 in the first opening 3 formed in step b and on the back surface of the substrate 1;

[0042] d. Use a l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More