Integrated method of surface channel CMOS (complementary metal oxide semiconductor) logic device and SONOS (silicon-oxide-nitride-oxide-silicon) device

A surface channel and logic device technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of inability to realize the integration of surface channel CMOS logic devices and SONOS devices, the inability to resist polysilicon penetration, device leakage, etc. problems, to achieve the effect of realizing the integration of small-sized surface channel devices and high-density storage devices, reducing the size, and reducing the size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

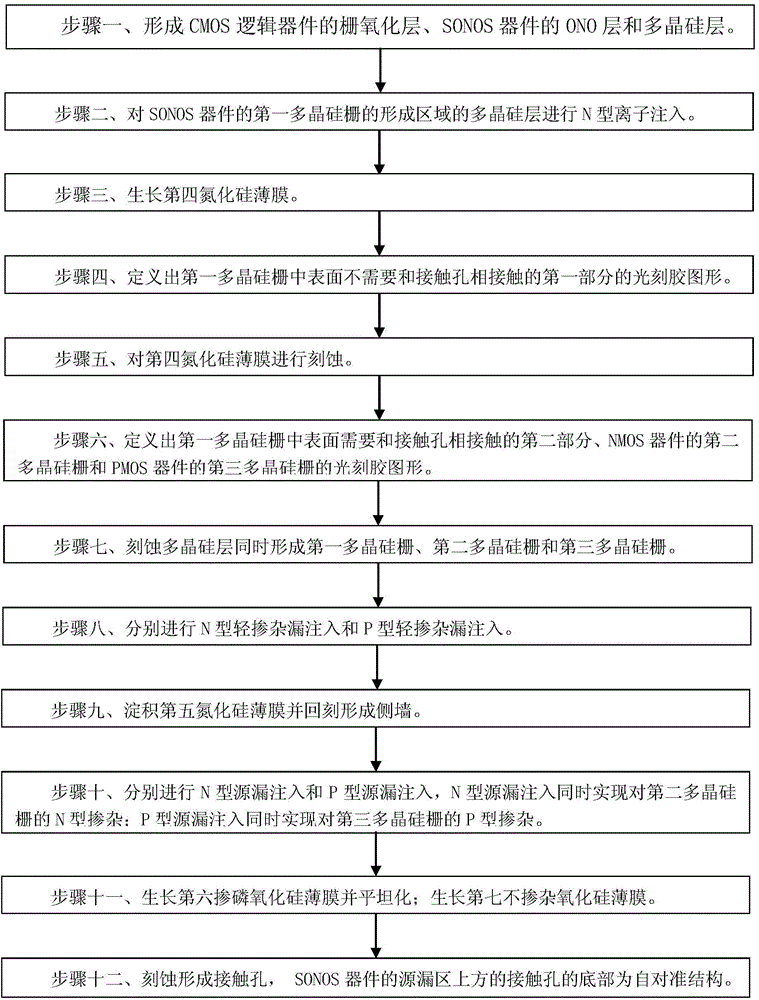

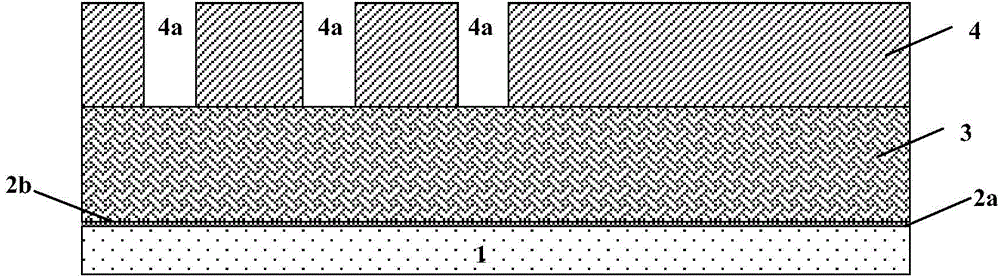

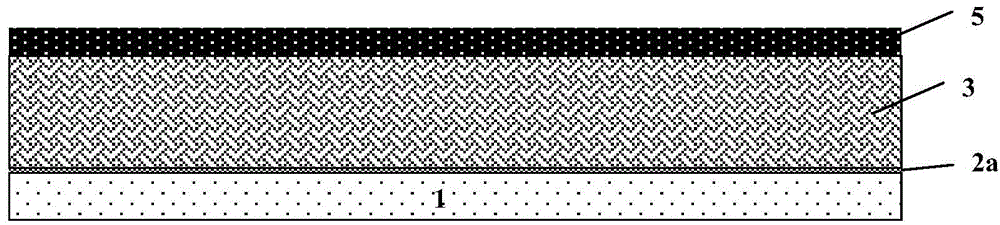

[0031] Such asfigure 1 Shown is the flow chart of the method of the embodiment of the present invention; Figure 2A to Figure 2J Shown is a device structure diagram in each step of the method of the embodiment of the present invention. The surface channel CMOS logic device in the integration method of the surface channel CMOS logic device and the SONOS device in the embodiment of the present invention includes a surface channel NMOS device and a surface channel PMOS device, including the following steps:

[0032] Step 1, such as Figure 2A As shown, the gate oxide layer 2a of the surface channel NMOS device and the surface channel PMOS device is formed on the surface of the silicon substrate 1 in the formation area of the surface channel CMOS logic device, and in the formation area of the SONOS device The ONO layer 2B of the SONOS device is formed on the surface of the silicon substrate 1, and the ONO layer 2B is composed of a first layer of silicon oxide, a second layer ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More