Forming method of CMOS (complementary metal-oxide-semiconductor) transistor

A technology of transistors and semiconductors, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of mask layer material residue, difficult to remove, and affect the quality of gates, etc., to achieve improved aspect ratio and easy The effect of removal

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

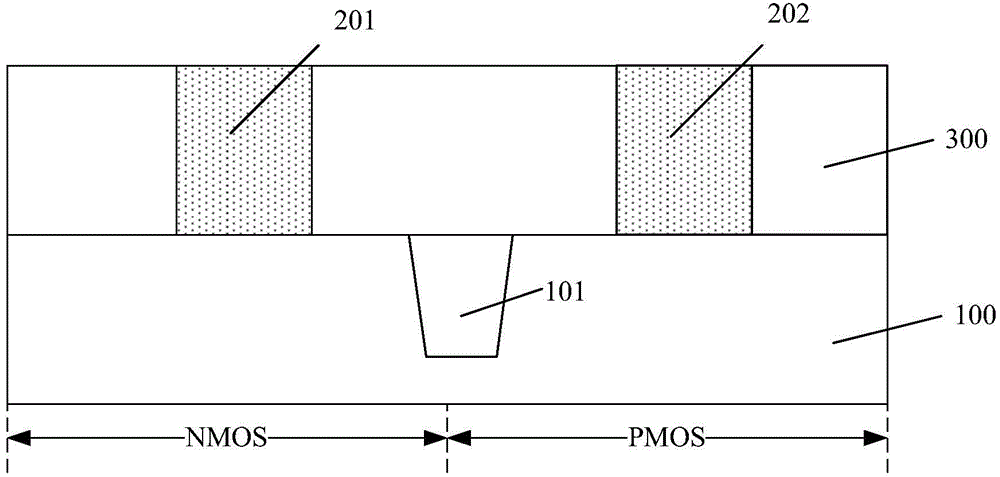

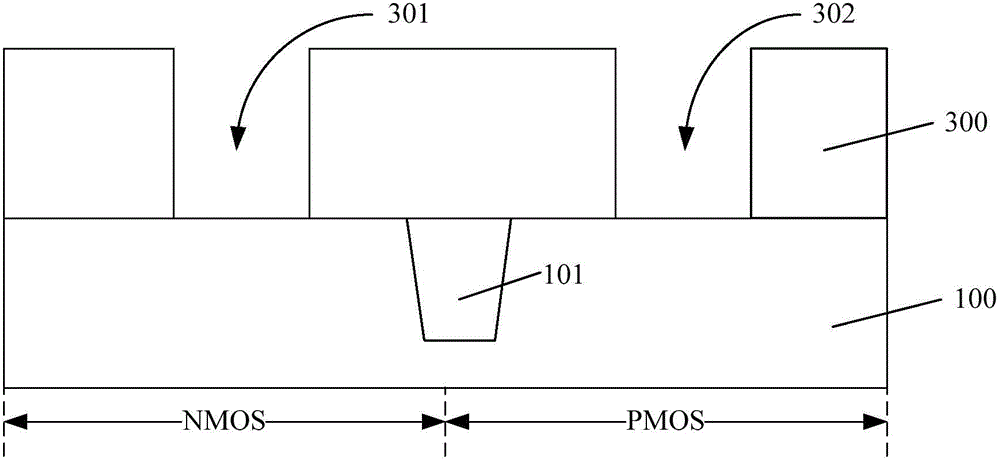

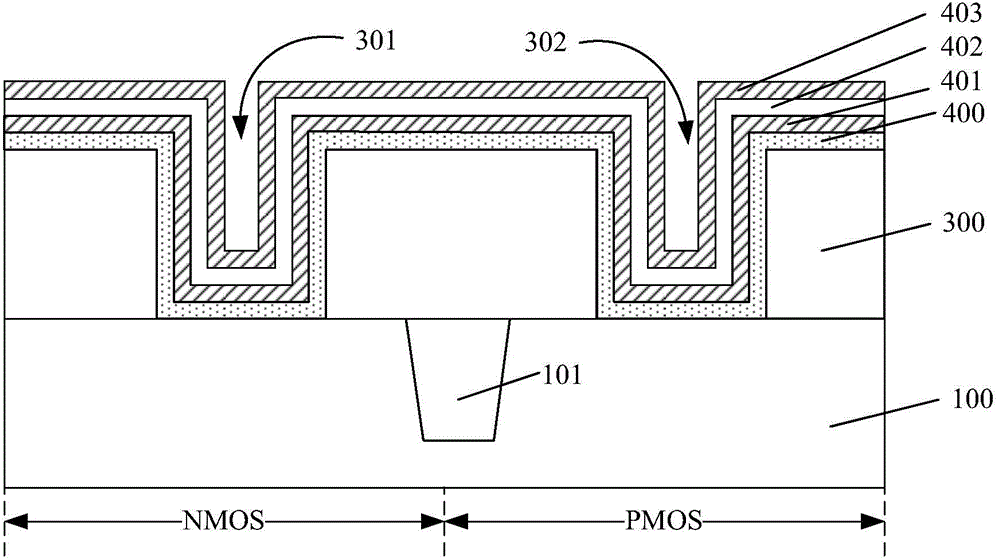

[0031] As mentioned in the background art, the performance of the CMOS transistors formed in the prior art needs to be further improved.

[0032] In the prior art, in the process of forming the NMOS transistor and the PMOS transistor, the same work function layer is formed in the NMOS region and the PMOS region at the same time, and then after the mask layer is formed in the PMOS region, the PMOS work function layer on the NMOS region is removed, so that Subsequent formed CMOS transistors and PMOS transistors have different work functions. The material of the mask layer is an organic material such as a photoresist layer or a bottom anti-reflection material. Although the filling effect of the mask layer in the groove for forming the grid can be improved, the organic material is removed during the removal process. Easy to leave residue. In the prior art, a mask layer is usually formed on the NMOS and PMOS regions at the same time, and then the mask layer on the NMOS region is r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More