MOS structure and method for making the same, and method for making metal silicide

A technology of metal silicide and MOS structure, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of reducing gate resistance and contact resistance, the effect of reducing gate resistance and contact resistance is not very good, the resistance value is large, and the power consumption of semiconductor devices The effect is not very good and other problems, to achieve the effect of ensuring electrical performance, low power consumption, small grid resistance and contact resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

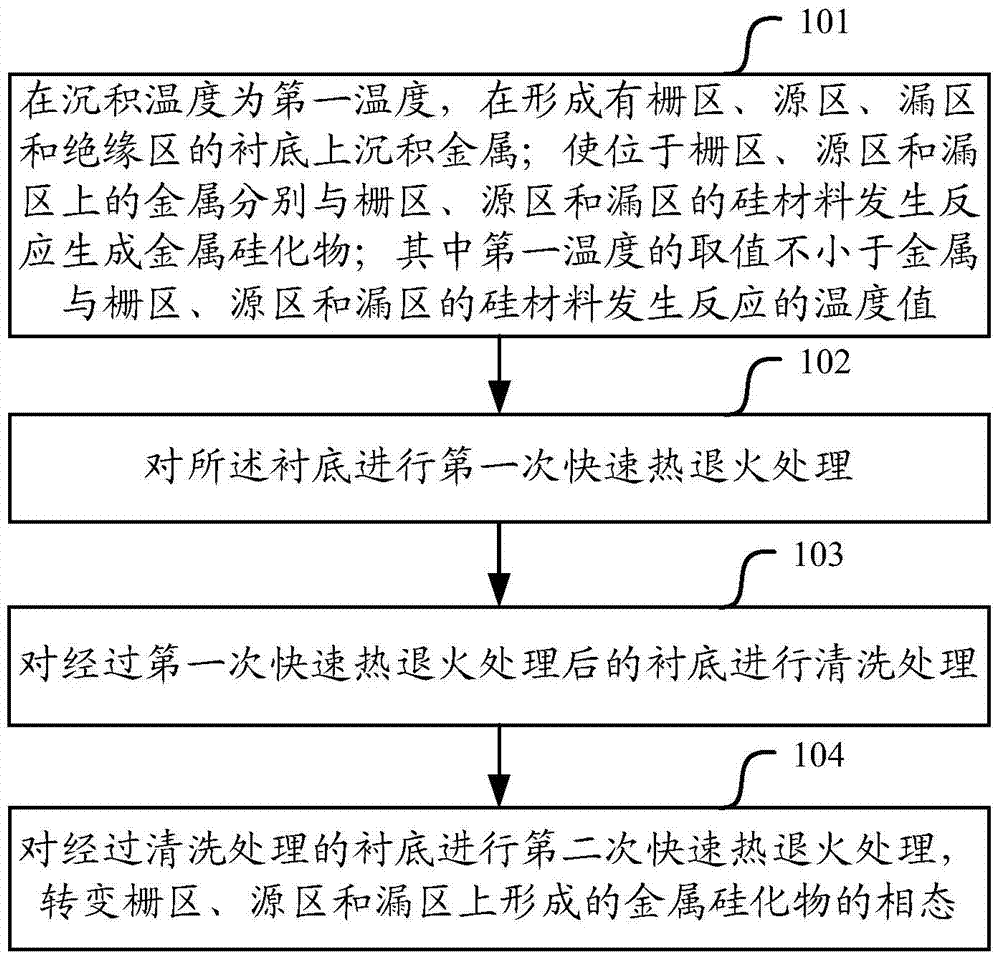

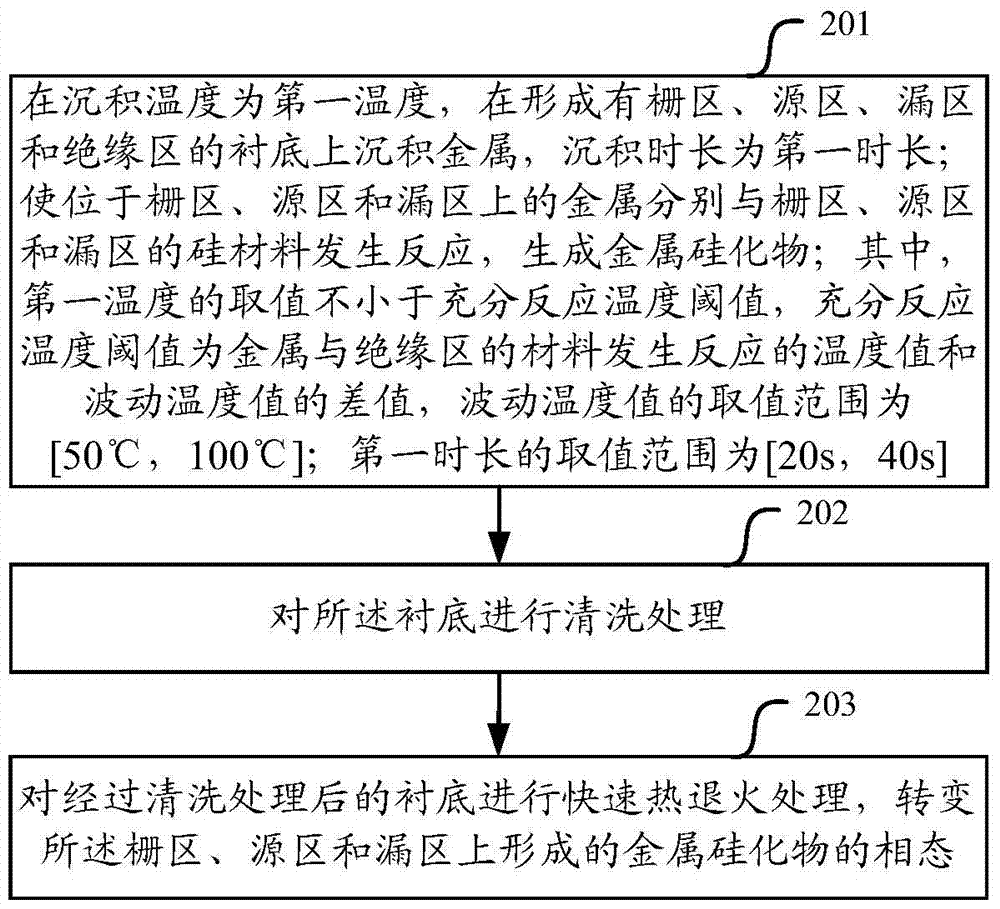

Method used

Image

Examples

Embodiment 1

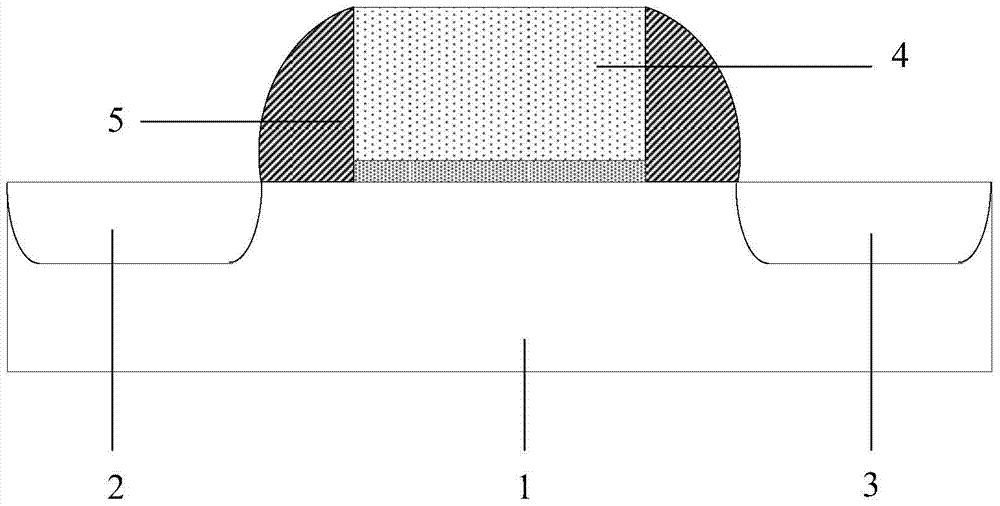

[0123] Such as Figure 3A As shown, the MOS structure includes a substrate 1, a source region 2 and a drain region 3 located in the substrate 1, and a gate region 4 and an insulating region 5 located on the substrate 1; wherein the materials of the source region 2 and the drain region 3 are Single crystal silicon, the material of the gate region 4 is polysilicon, and the material of the insulating region 5 is silicon dioxide; T i The temperature value of reaction with monocrystalline silicon and polycrystalline silicon is 200°C, T i The value of the reaction temperature with silicon dioxide is 750°C, and the range of deposition temperature is [200°C, 750°C).

[0124] Step A1. Under the condition that the deposition temperature is 200°C-500°C, the vacuum degree of the reaction chamber of the deposition equipment is 3mt (milliTorr), and the deposition power is 2.5kw, the gate region, the source region, the drain region and the insulating region are formed. Deposit a layer of T...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More