Forming method of semiconductor structure

A semiconductor and gate structure technology, which is applied in the field of semiconductor structure formation, can solve the problems of unstable leakage current performance, inhomogeneity, poor fin surface morphology and feature size, etc., and achieve the effect of precise and uniform structure size and avoiding damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] As mentioned in the background, in the existing fin field effect transistors, the surface morphology of the fin portion is poor, and the feature size is not uniform.

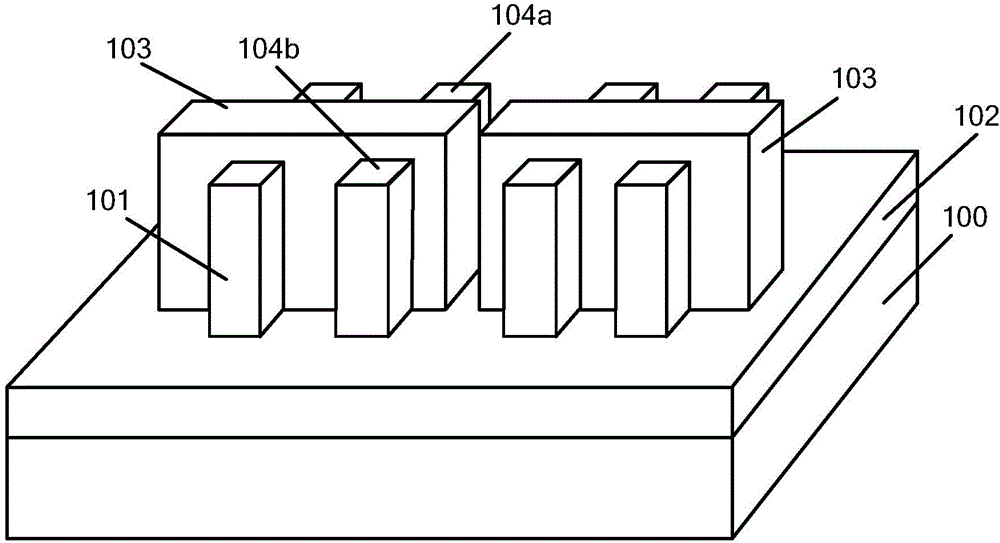

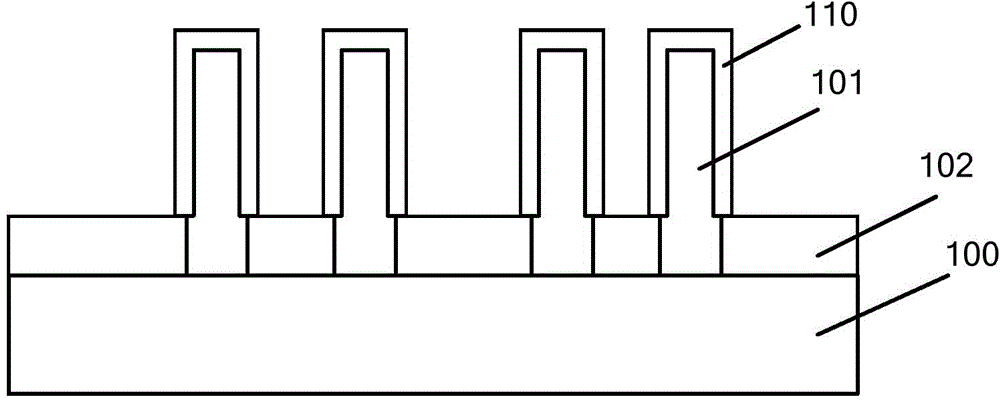

[0035] After research, it is found that in a process embodiment of forming a fin field effect transistor, such as figure 1 As shown, before the gate structure 103 is formed on the surface of the dielectric layer 102 and the top and sidewall surfaces of the fin 101, it is necessary to use an ion implantation process to dope P-type or N-type ions in the fin 101, so that the fin Portion 101 becomes an active region. In order to protect the fin 101 from damage during the ion implantation process, before the ion implantation process, a pad oxide layer 110 (such as figure 2 shown).

[0036]The thermal oxidation process is carried out in a high-temperature oxygen atmosphere, and by diffusing oxygen into the exposed sidewalls and top surfaces of the fins, the oxygen is combined with the semiconductor material ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More