Test structure and test method for gate oxide integrity

A technology for testing structure and gate oxide layer, which is used in semiconductor/solid-state device testing/measurement, electrical components, electrical solid-state devices, etc., which can solve the problems of limited testing capability, long testing cycle time, and inability to guarantee test results.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

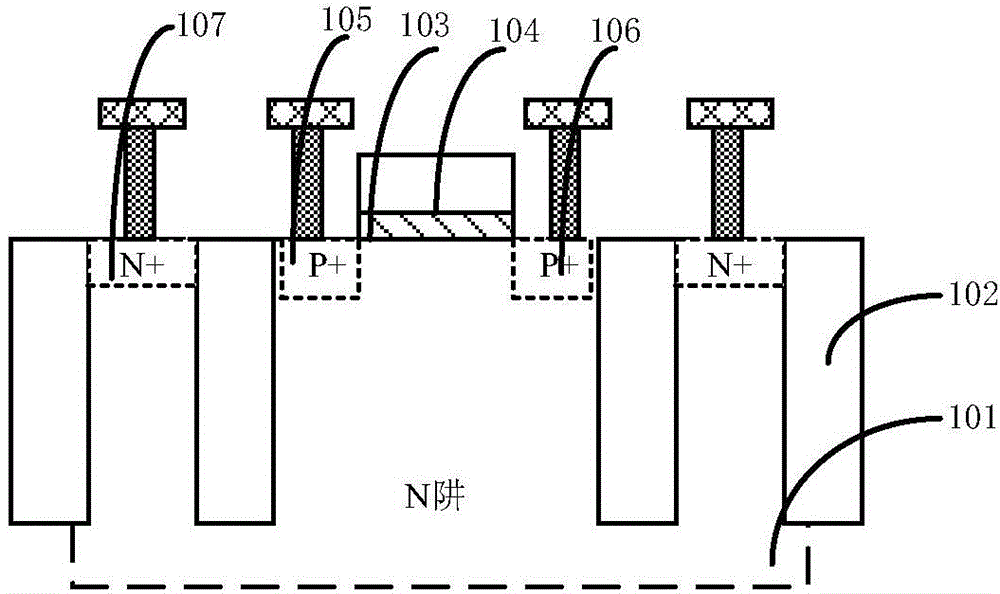

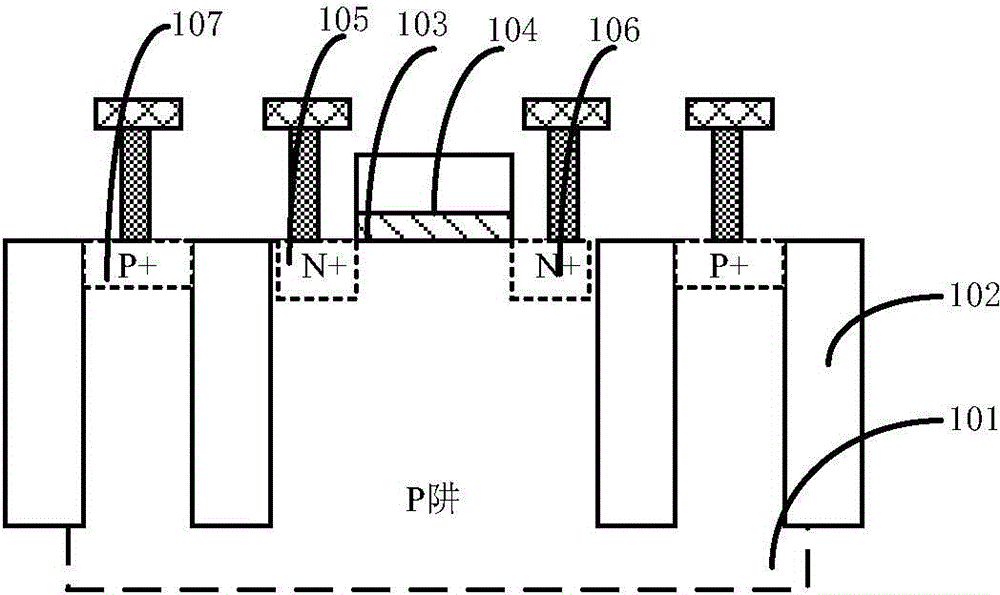

[0045] Attached below figure 2 The test structure of the present invention is further described.

[0046] First, the test structure includes at least:

[0047] A semiconductor substrate 201, in which an N well and a P well are arranged at intervals;

[0048] a gate structure, including a gate oxide layer 203 and a gate electrode 204, the gate structure is partially located above the N well and partially above the P well;

[0049] a source region and a drain region respectively located in the N well and the P well on both sides of the gate structure;

[0050] Wherein the semiconductor substrate 201 , the source region and the drain region are grounded, and the gate structure is connected to a power supply voltage.

[0051] Wherein, the semiconductor substrate 201 may be at least one of the materials mentioned below: silicon, SiGe, etc., and other active devices may also be formed in the semiconductor substrate. A silicon substrate is preferred in the present invention.

...

Embodiment 2

[0072] The present invention also provides a method for testing the test structure prepared in Example 1, the method includes applying a gradually increasing stress voltage on the gate structure to measure the breakdown voltage of the gate oxide layer , and then evaluate the gate oxide layer.

[0073] In this embodiment, the breakdown voltage of the gate oxide layer is tested by a ramp voltage test method. The Vramp test ramps up the acceleration voltage linearly from the operating voltage to the breakdown of the oxide layer. According to the measured breakdown voltage, the The gate oxide layer is evaluated. If the measured breakdown voltage is higher than the specified voltage, it means that there are no defects in the gate oxide layer and the edge of the gate structure; if the measured breakdown voltage is lower than If the specified voltage is higher, it indicates that there are defects in the gate oxide layer and the edge of the gate structure.

[0074] In the method, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More