Method for forming fin field-effect transistors, and method for forming MOS transistors

A MOS transistor, fin field effect technology, applied in the field of semiconductor manufacturing, can solve problems such as metal residues, and achieve the effect of increasing density or hardness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

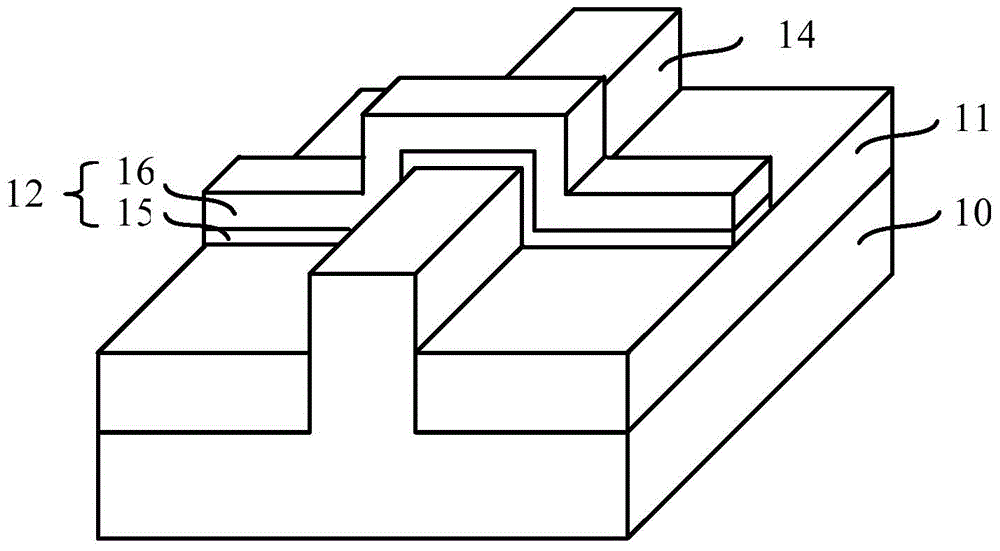

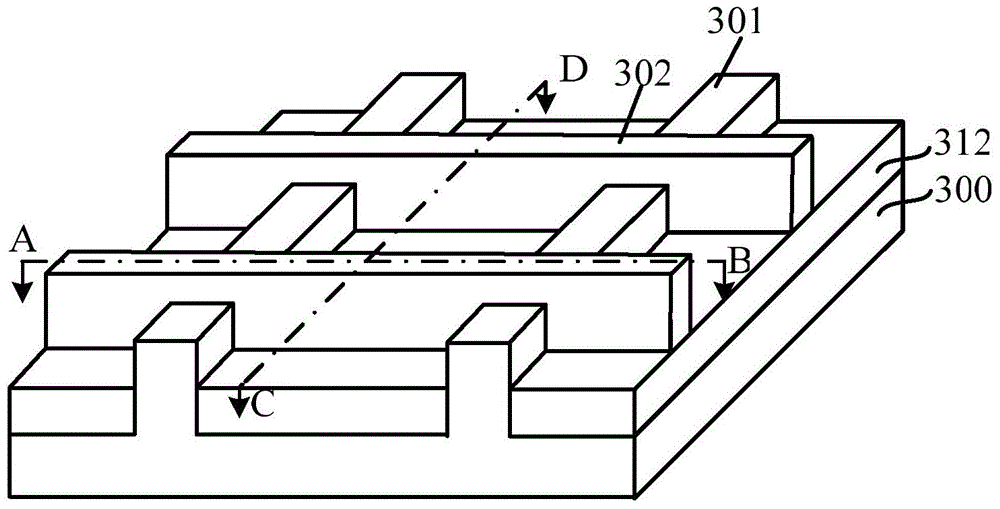

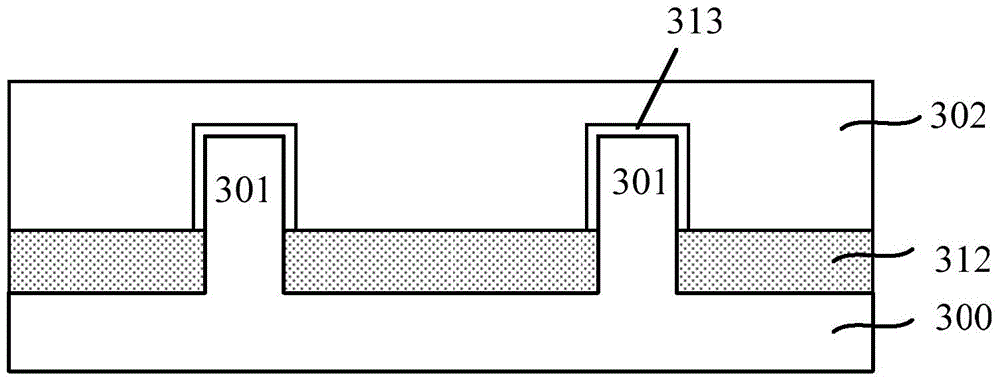

[0034]Since the fin field effect transistor has a special structure such as a fin and a gate structure across the sidewall and surface of the fin, when forming the dielectric layer, the gap between the fin and the gate structure and the gate structure It is difficult to fill the gaps well. In order to improve the gap filling performance of the dielectric layer, the prior art usually adopts the fluid chemical vapor deposition process to form the dielectric layer, although the dielectric layer formed by the fluid chemical vapor deposition has a higher gap filling performance. performance, but the material of the dielectric layer formed by fluid chemical vapor deposition is relatively soft or loose. The difference is very large, and it is very easy to form a dishing defect on the surface of the planarized dielectric layer. After removing the dummy gate to form a groove, when the metal gate is formed in the groove by deposition and chemical mechanical polishing process, part of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More