Formation method of semiconductor structure

A semiconductor and gas technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of semiconductor structure electrical properties to be improved, to optimize surface performance, improve flatness, improve surface The effect of flatness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] It can be seen from the background art that the electrical performance of the semiconductor structure formed in the prior art is relatively poor.

[0036] It has been found through research that one of the main reasons for the poor electrical performance of the semiconductor structure is: the electrical performance of the interconnection structure in the semiconductor structure is abnormal (abnormal), and even the problem of bridging (bridge) between adjacent metal layers occurs, so The abnormal electrical properties of the interconnect structure lead to poor electrical properties of the semiconductor structure.

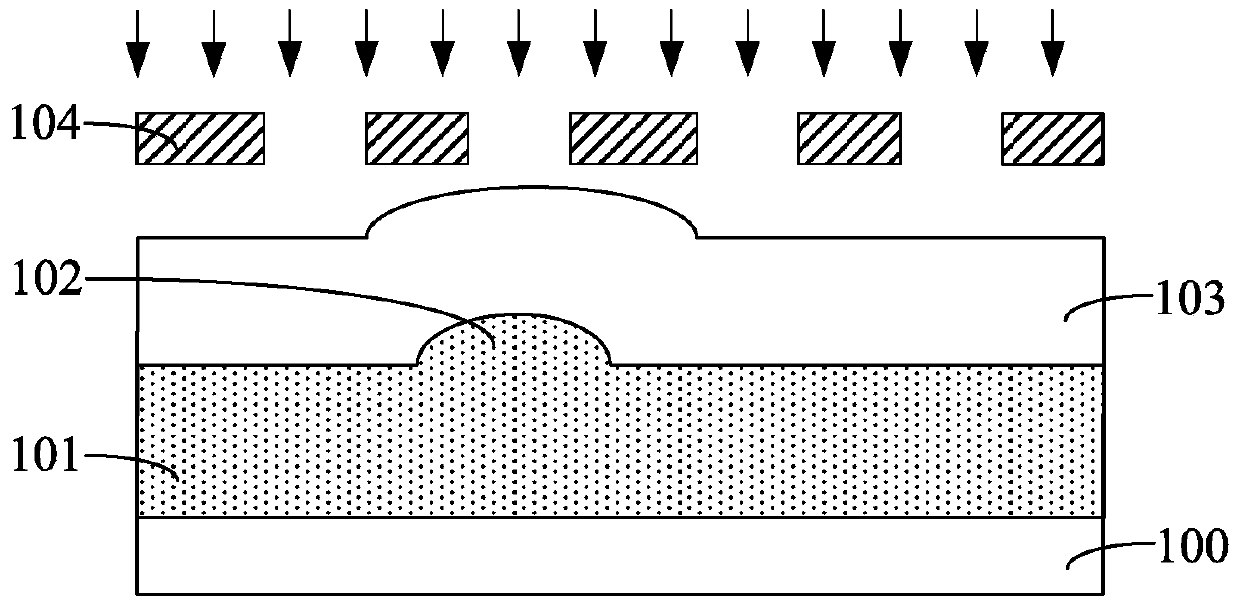

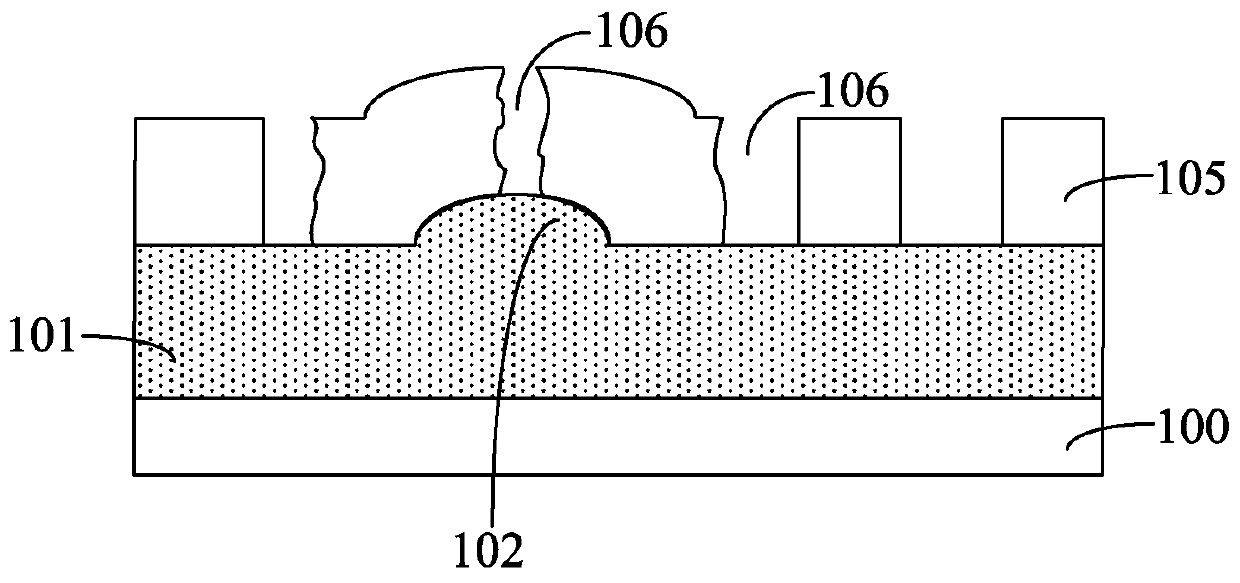

[0037] For further research on the formation method of the semiconductor structure, the formation method of the semiconductor structure includes the following steps: Please refer to figure 1 , provide a substrate 100 with a conductive layer inside the substrate 100; form a dielectric layer 101 on the surface of the substrate; form a photoresist film 103 on the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More