Gate-commutated thyristor with double p-base gate-cathode structure and preparation method thereof

A gate commutation, thyristor technology, applied in the direction of thyristor, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problem that the doping concentration of the p+ short base region cannot be too high, reduce the turn-off capability of the GCT chip, and increase the GCT chip. Process difficulty and other problems, to achieve the effect of eliminating the digging process, increasing the voltage, improving reliability and yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

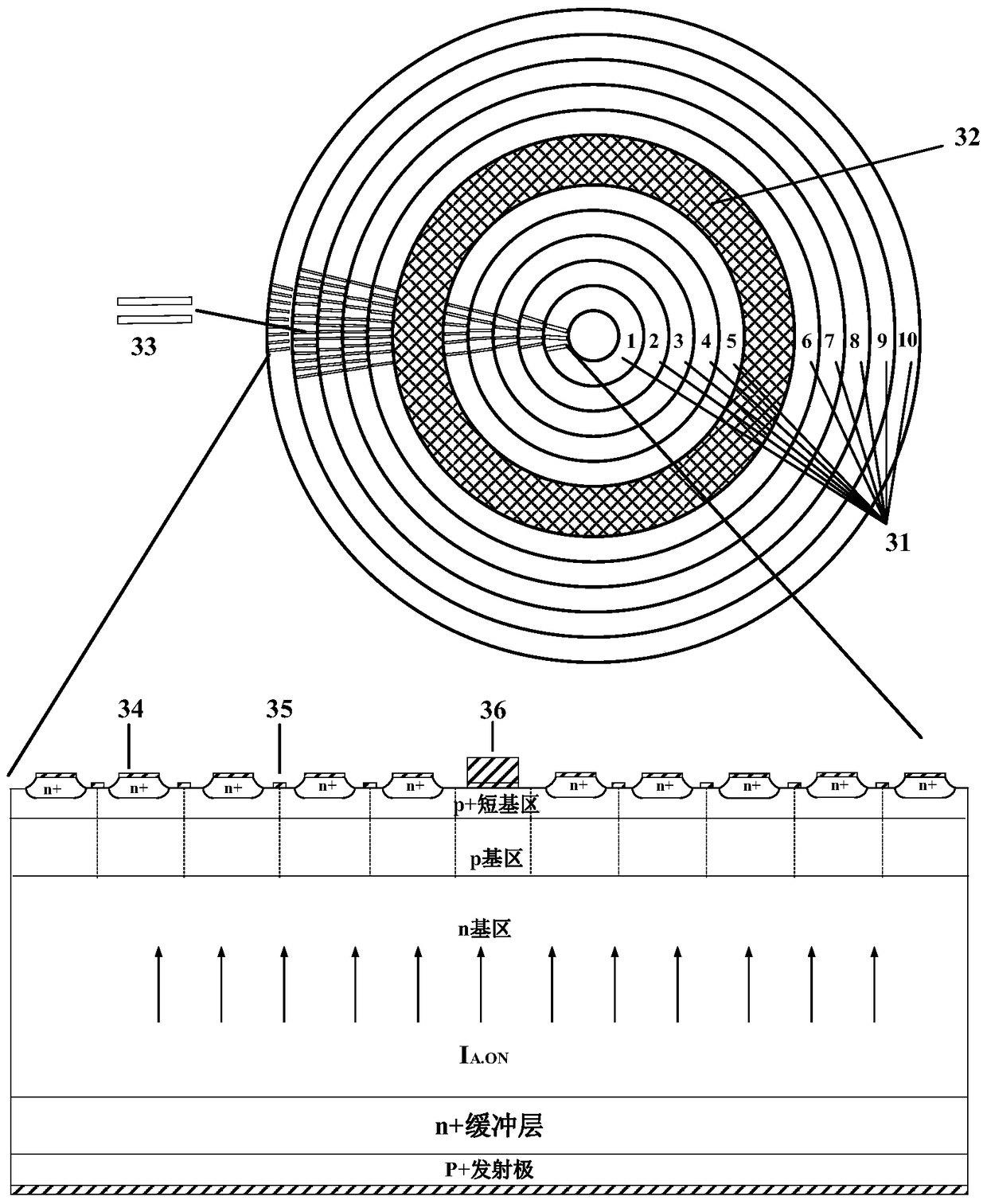

[0061] A GCT chip with a novel gate-cathode structure proposed by the present invention will be described in detail below in conjunction with the accompanying drawings and embodiments:

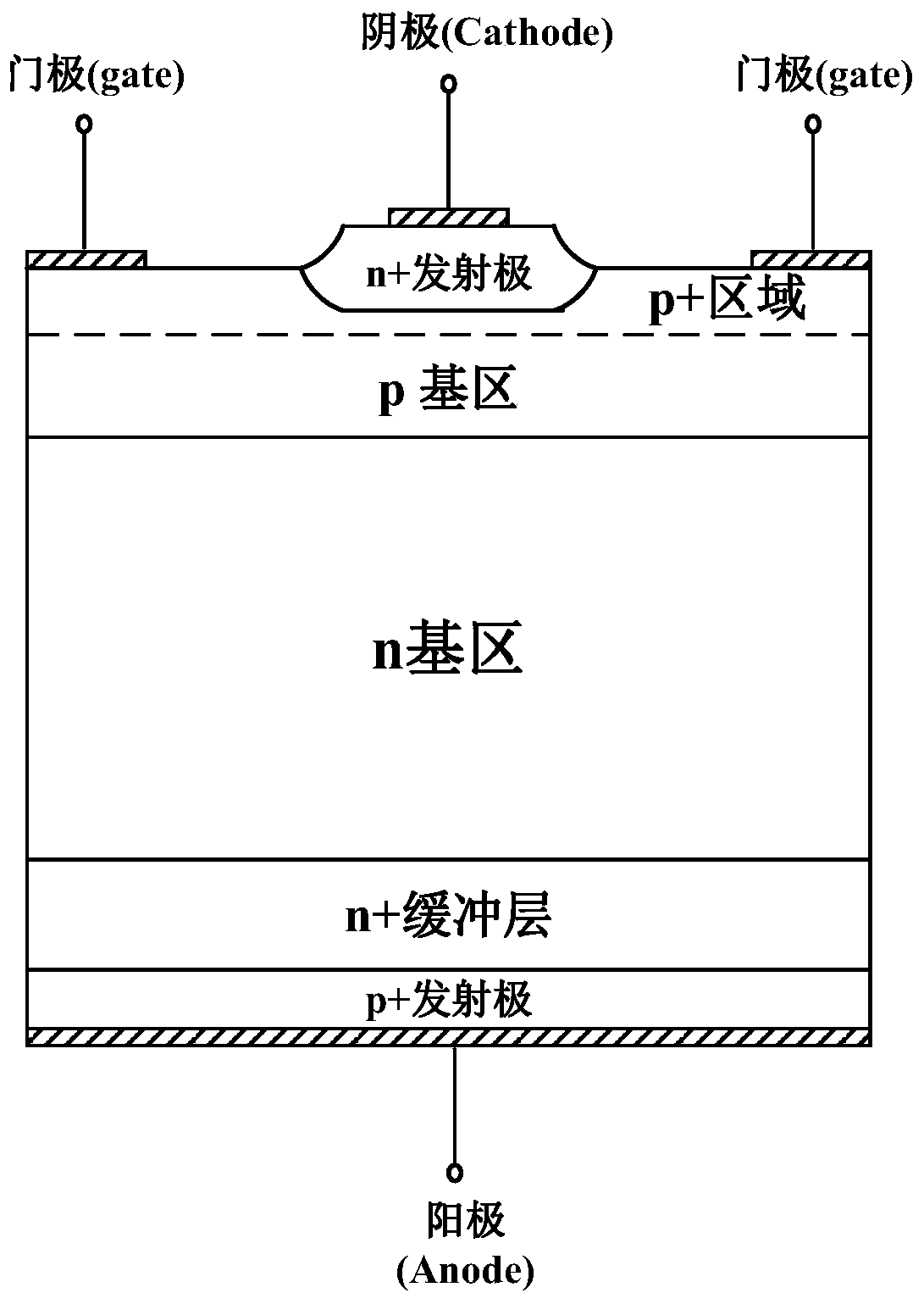

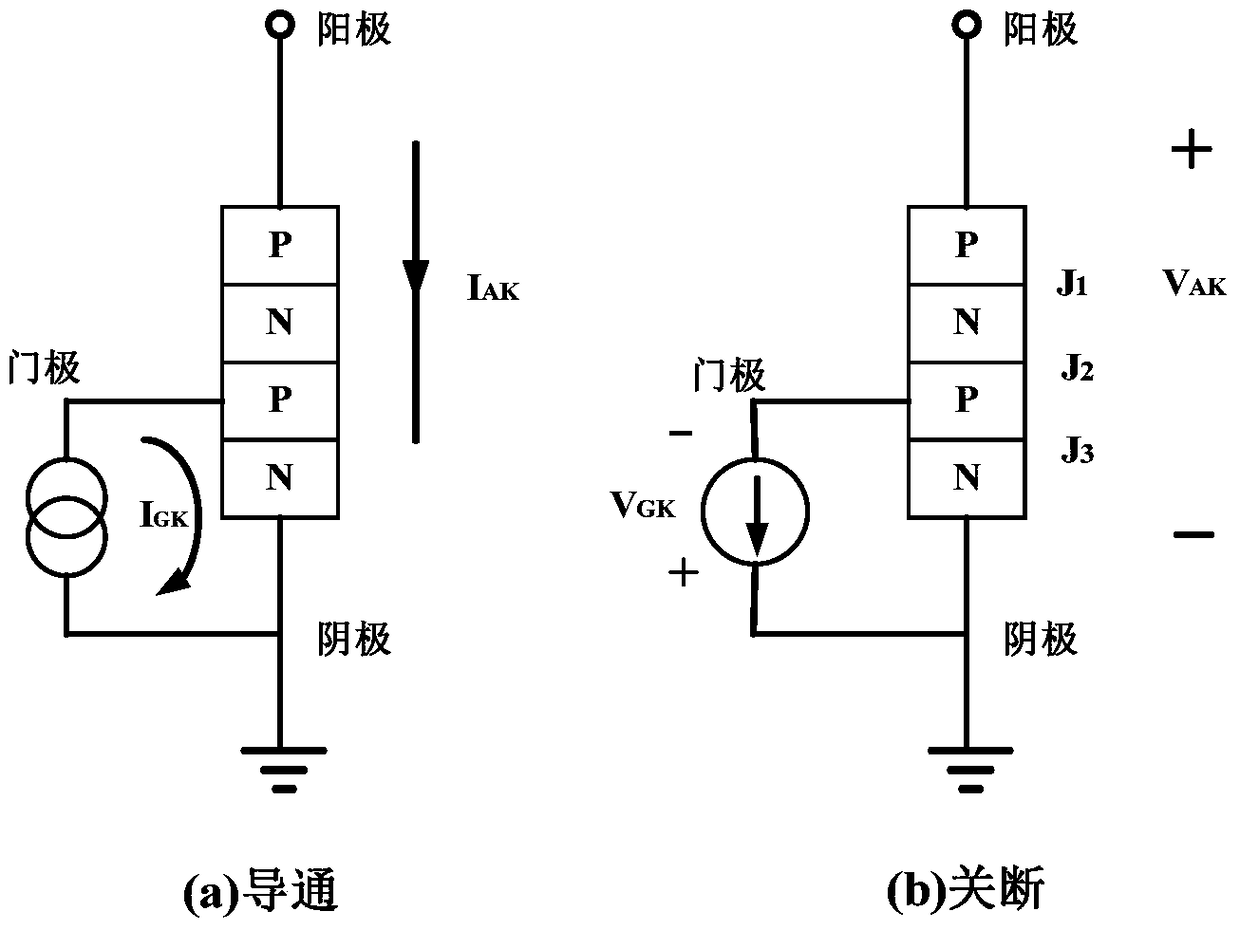

[0062] In order to overcome the deficiency of the GCT chip, it is possible to make the external drive power V GK Larger, and can make the p+ short base region form a current channel with a sufficiently low resistivity. The present invention proposes a GCT with a gate-cathode structure with double p-base regions. The specific implementation structure of the GCT chip is as follows Figure 8 shown. The GCT chip includes more than one cell, and the single cell structure includes from the cathode surface to the anode surface: n+ emitter (cathode), p base region 2, p+ short base region, p base region 1, n-substrate, n' buffer zone, p+ emitter (anode) and cathode surface metal electrode, gate surface metal electrode, anode surface metal electrode.

[0063] In the GCT chip structure proposed by the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More