Wafer level package method for reducing edge stress

A wafer-level packaging, edge stress technology, used in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as cracking, delamination, affecting the reliability of metal wiring layers, and achieve improved electrical connection, increase The effect of package reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] The present invention will be described in more detail below with reference to accompanying drawing:

[0047] The wafer-level packaging manufacturing process for reducing edge stress of this embodiment will be described in detail below with reference to FIGS. (1) to (8).

[0048] Step 1, provide wafer 100:

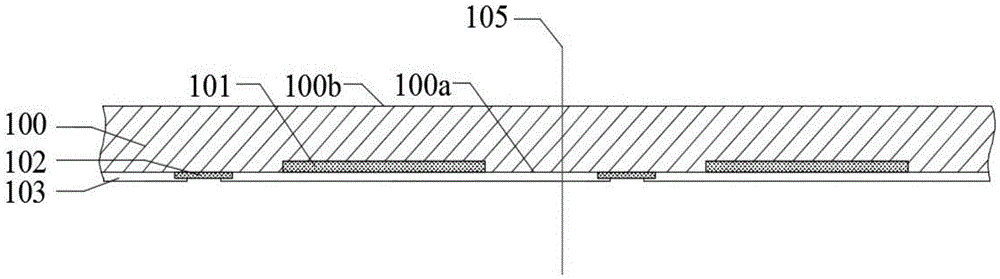

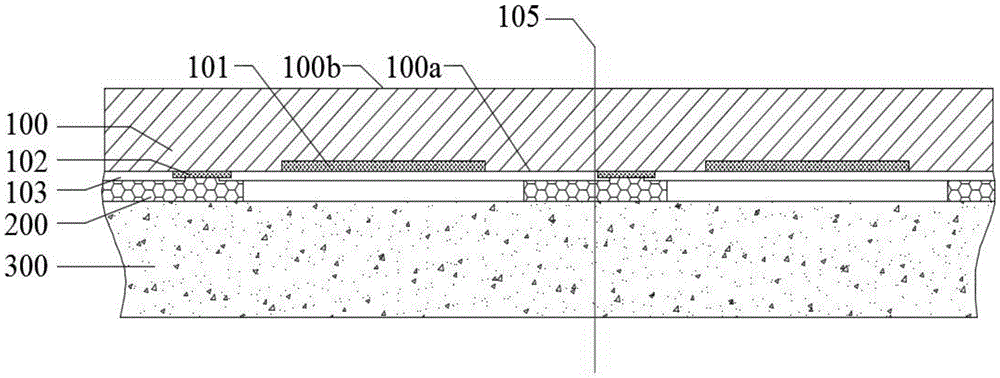

[0049] Referring to FIG. (1), a wafer 100 is provided, and a functional area 101 , pads 102 , and a dielectric layer 103 are formed on the wafer 100 . The functional areas, pads, and dielectric layers are formed on the wafer 100 . In other embodiments, the wafer material may be semiconductor materials such as germanium and gallium arsenide.

[0050] There is a dicing line 105 with a certain width between adjacent functional areas 101 of the wafer, and the dicing line does not cover the pad. Dicing along this scribe line separates the wafer into individual chips.

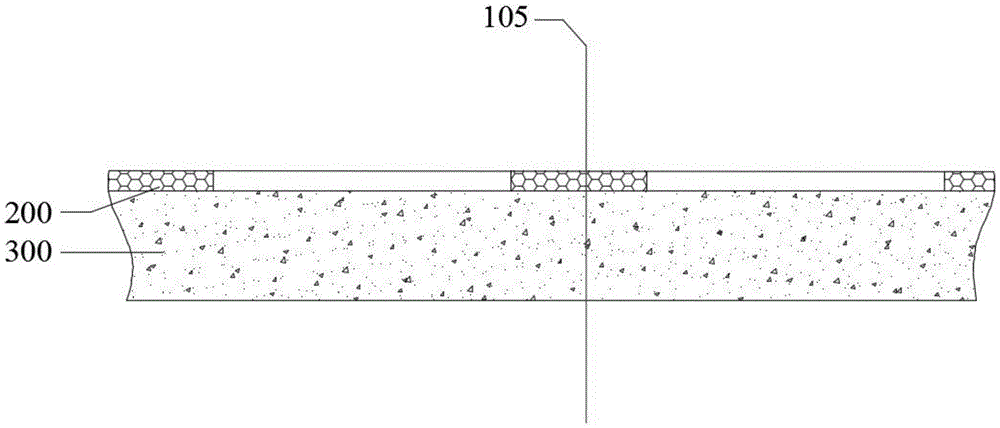

[0051] Step 2, bonding the cover plate 300 and the support wall 200:

[0052] Referring to Figure ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More