Data packet processing method and device in ofdma system

A processing method and data packet technology, which are applied in the field of data packet transmission to achieve the effects of improving performance, improving decoding speed, and speeding up

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

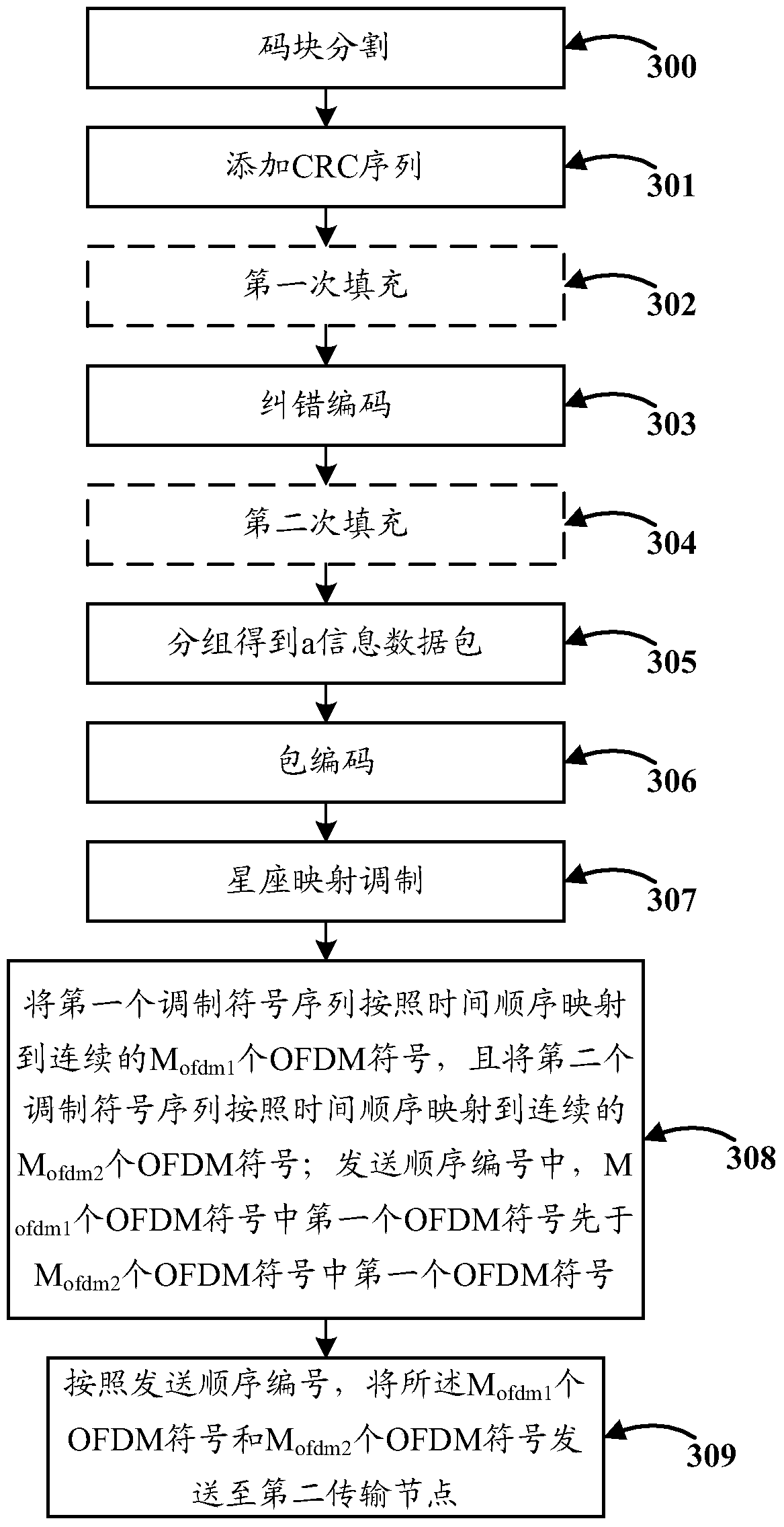

[0056] image 3 It is a flowchart of a data packet processing method in an OFDMA system according to Embodiment 1 of the present invention, such as image 3 As shown, the OFDMA system data packet processing method of the embodiment of the present invention comprises the following steps:

[0057] 300. Perform code block segmentation on the source data packet to be transmitted to obtain d data blocks;

[0058] 301. Add a CRC sequence to each data block respectively;

[0059] 303. Perform error correction coding on the d data blocks after adding the CRC sequence,

[0060] 305. Perform grouping to obtain a information data packets of equal length;

[0061] 306. Perform packet encoding on a information data packet to obtain b verification data packets;

[0062] 307. Perform constellation mapping modulation on the a information data packets to obtain a first modulation symbol sequence with a length of k1, and perform constellation mapping modulation on the b verification data pa...

example 1

[0120] In an OFDMA communication system, a single OFDM symbol has 1024 subcarriers, and the number of valid data subcarriers is 800. This example is used for the first transmission node to transmit data for the mobile user 100 to the second transmission node for the base station 101, such as figure 1 shown. The data packet processing method in the OFDMA system of the embodiment of the present invention at least includes the following steps, such as image 3 Shown:

[0121] 300. Perform code block segmentation on the 1968-bit source data packet to be transmitted to obtain d=6 data blocks, each of which has a length of 328 bits;

[0122] 301. Add a CRC sequence of h=8 bits to each data block respectively. After adding the CRC sequence, the length of each data block becomes 336 bits. Since the length of each data block is equal and equal to the mother code input bit is 336 bits, so No first fill required;

[0123] 303. Perform Turbo error correction coding on the d=6 data blo...

example 2

[0131] The difference between example 2 and example 1 is that each information packet obtained by grouping in step 305 has 2 * 672 bits and the modulation mode adopted by the second modulation symbol sequence in step 307 is 16QAM, as follows:

[0132] In step 305, the data after the Turbo error correction encoding is grouped to obtain equal-length a=3 information data packets, each information data packet has 2 * 672 bits, and each information data packet has 2 Turbo error correction encoding blocks ; Then in step 306, the length of a check data packet obtained by packet encoding is also 2×672 bits;

[0133] In step 307, the length of the first modulation symbol sequence is k1=2016 constellation mapping modulation symbols, the modulation order is Mod1'=2, the constellation mapping modulation mode is QPSK, and the length of the first modulation symbol sequence is k2=336 Constellation mapping modulation symbols, the modulation order is Mod2'=4, and the constellation mapping modu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More