Non-volatile memory

A non-volatile, memory technology, used in electrical solid state devices, semiconductor devices, electrical components, etc., can solve the problems of reducing the reliability of memory components, affecting the electrical performance of memory cells, and depleting the tunnel oxide layer. The effect of erasing voltage, increasing speed, and increasing coupling rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

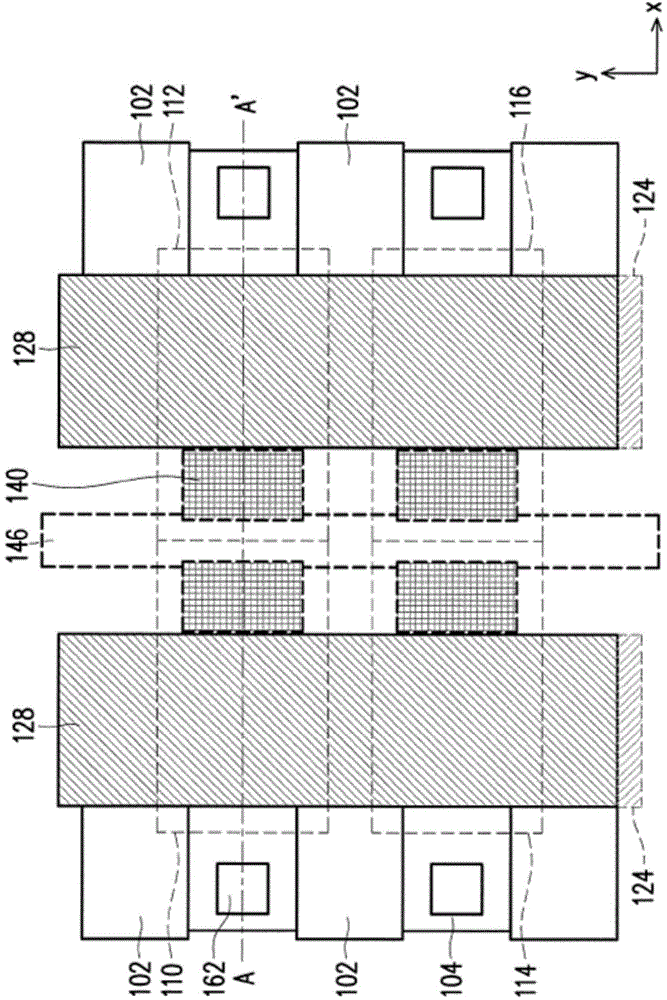

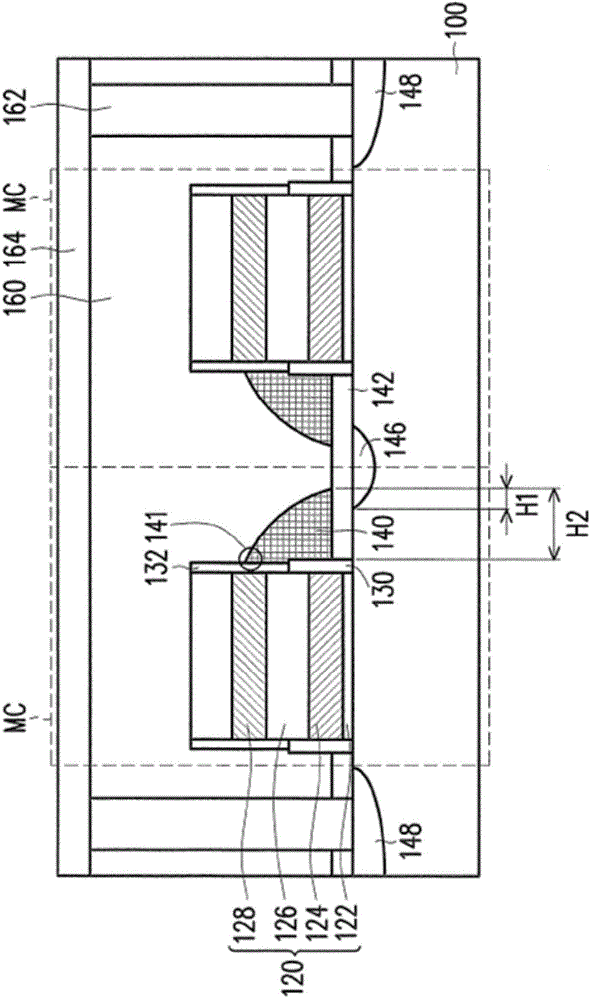

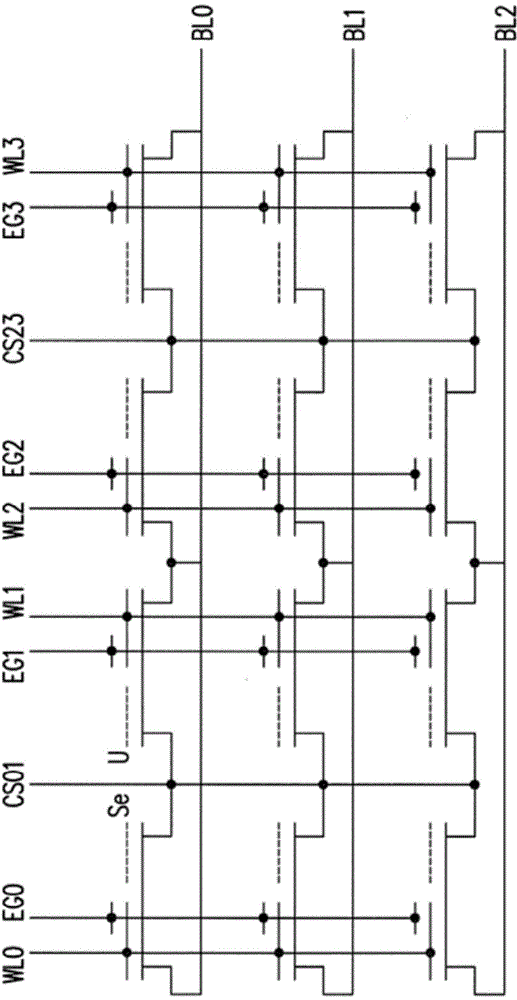

[0085] Figure 1A It is a top view of a non-volatile memory shown in the first embodiment of the present invention. Figure 1B It is a schematic cross-sectional view of a non-volatile memory shown in the first embodiment of the present invention. Figure 1B shown as along the Figure 1A Sectional view of line A-A' in the middle. Figure 1C It is a schematic circuit diagram of a non-volatile memory shown in the first embodiment of the present invention.

[0086] Please refer to Figure 1A and Figure 1B , the nonvolatile memory includes a plurality of memory cells MC. These memory cells MC are arranged in a row / column array.

[0087] The nonvolatile memory is disposed on the substrate 100 . For example, a plurality of isolation structures 102 arranged regularly are disposed in the substrate 100 to define a grid-like active region 104 . The isolation structure 102 is, for example, a shallow trench isolation structure.

[0088] Each memory cell MC includes a stack structure...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com