Relaxation oscillator and monolithic integrated chip

A relaxation oscillator and comparator circuit technology, applied in the direction of pulse generation, electrical components, electric pulse generation, etc., can solve the problem of low current utilization rate, and achieve high current utilization rate, ultra-low power consumption, and low power consumption Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

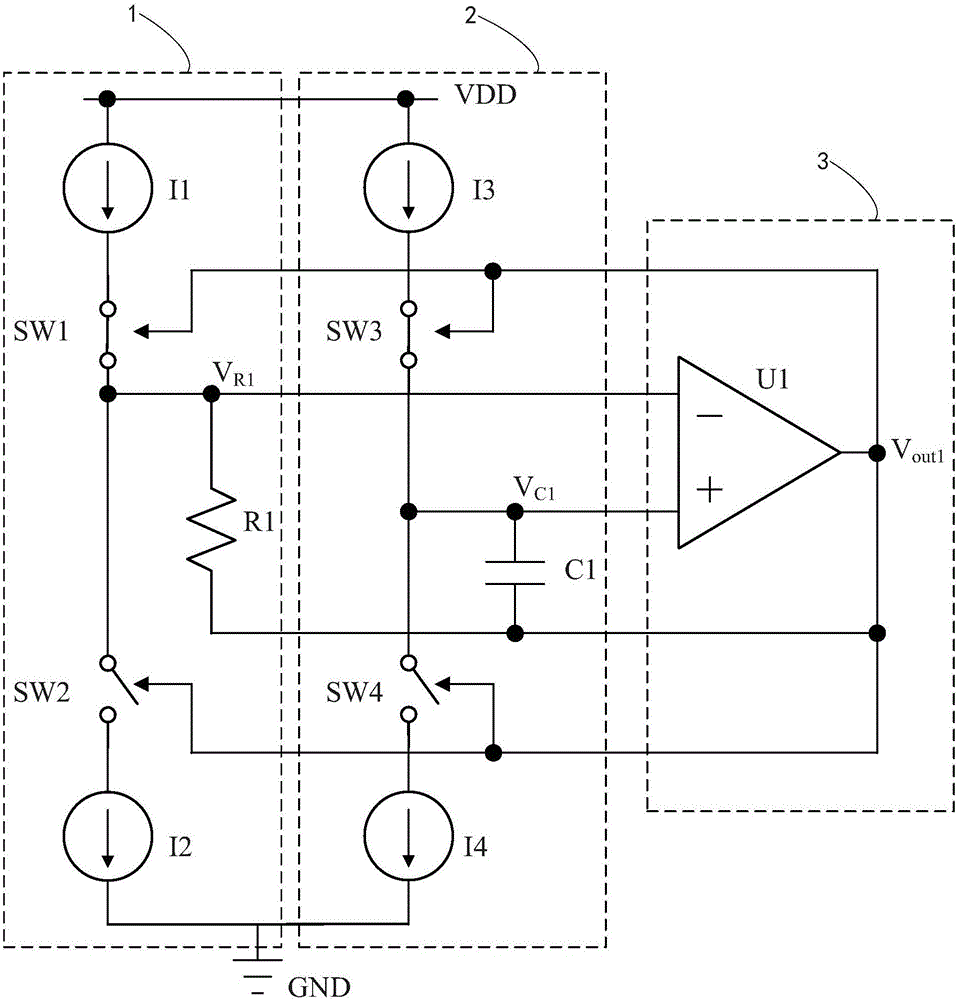

[0030] Such as figure 1 as shown, figure 1 It is an electrical schematic diagram of a relaxation oscillator circuit of an embodiment of the relaxation oscillator of the present invention. It can be seen from the figure that the relaxation oscillator circuit of the oscillator includes a threshold voltage generating circuit 1, a capacitor charging and discharging circuit 2, and a comparator circuit 3. The threshold voltage generating circuit 1 inputs a threshold value to the inverting input terminal of the comparator circuit 3. The capacitor charging and discharging circuit 2 inputs the capacitor voltage signal to the non-inverting input terminal of the comparator circuit 3 . Threshold voltage generating circuit 1 includes a first current source I1, a second current source I2 and a threshold resistor R1, the first current source I1 applies a current to the threshold resistor R1 through a first inverting switching element SW1 (that is, the current flows from the first current so...

no. 2 example

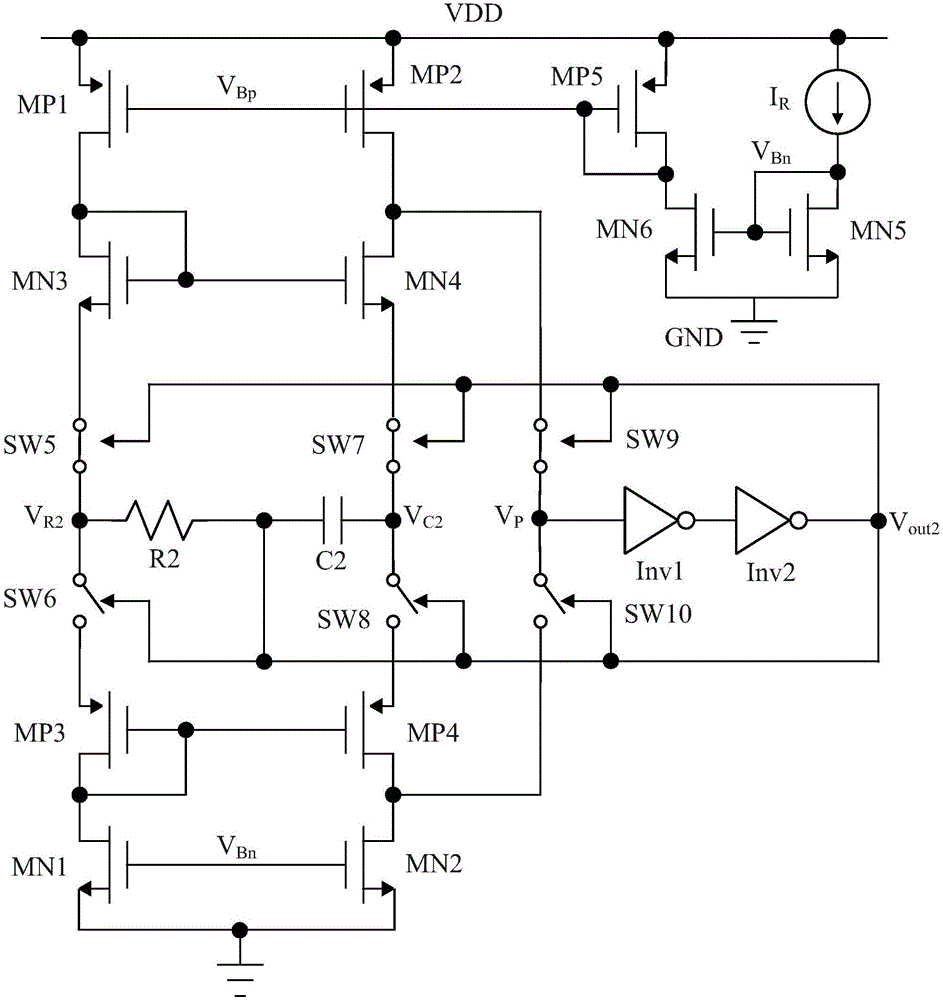

[0038] Such as figure 2 as shown, figure 2 It is a schematic circuit diagram of another embodiment of the present invention. In this embodiment, the relaxation oscillator circuit includes a bias circuit, and the bias circuit includes a reference current source I R , the fifth NMOS transistor MN5, the sixth NMOS transistor MN6 and the fifth PMOS transistor MP5, wherein the reference current source I R electrically connected to the power line VDD while referenced to the current source I R It is electrically connected to the drain and gate of the fifth NMOS transistor MN5, the gate of the fifth NMOS transistor MN5 is electrically connected to the gate of the sixth NMOS transistor MN6, and the drain and gate of the fifth PMOS transistor MP5 are connected to the sixth NMOS transistor MN5. The drain of the tube MN6 is electrically connected. The bias circuit consists of a current source I R , the fifth NMOS transistor MN5 , the sixth NMOS transistor MN6 and the fifth PMOS tra...

Embodiment 3

[0046] see Figure 4 , Figure 4 It is the electrical principle diagram of the relaxation oscillator circuit of the third embodiment of the relaxation oscillator of the present invention.

[0047] In this embodiment, the relaxation oscillator circuit includes a bias circuit, and the bias circuit includes a reference current source I R1 , NMOS tube MN51, NMOS tube MN61 and PMOS tube MP51, wherein the reference current source I R1 electrically connected to the power line VDD while referenced to the current source I R1 It is electrically connected to the drain and gate of NMOS transistor MN51, the gate of NMOS transistor MN51 is electrically connected to the gate of NMOS transistor MN61, and the drain and gate of PMOS transistor MP51 are electrically connected to the drain of NMOS transistor MN61. The bias circuit consists of a current source I R1 , NMOS tube MN51, NMOS tube MN61 and PMOS tube MP51 form a mirror current source to provide bias current for the oscillation circu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More