Performance test system for low-illumination CMOS chip

A technology for testing system and chip performance, applied in electronic circuit testing, non-contact circuit testing, electrical measurement, etc., can solve the problems of large error and cumbersome operation, and achieve the effect of increasing error, stability and repeatability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

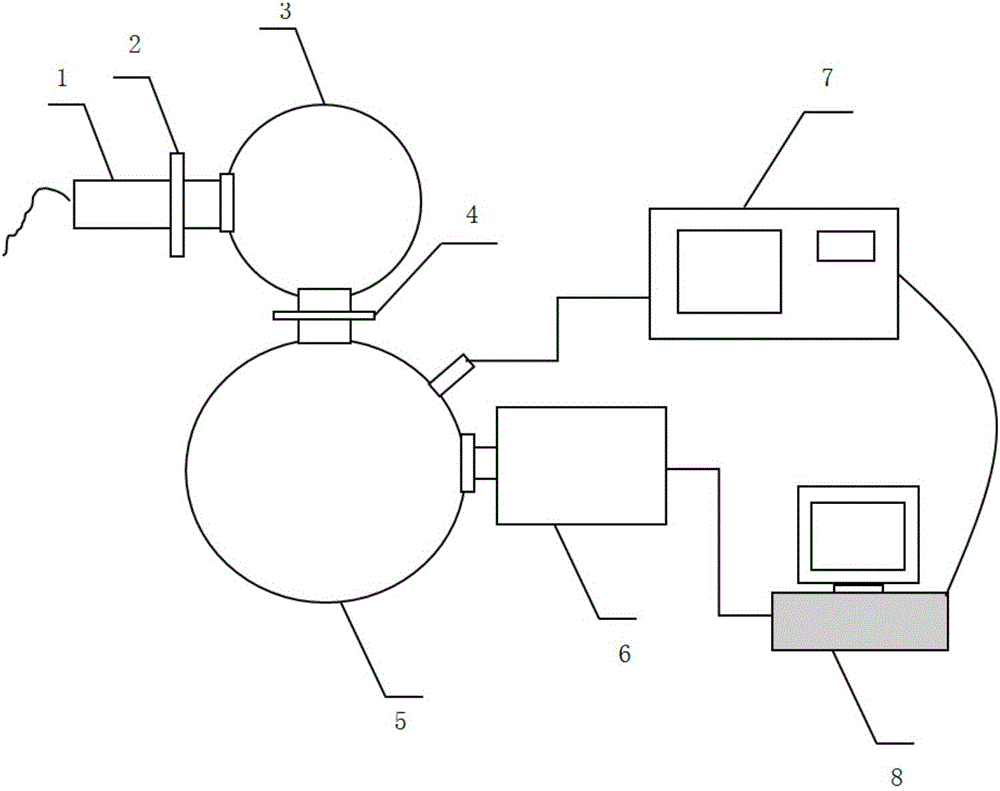

[0012] combine figure 1 , a low-illuminance CMOS chip performance testing system of the present invention, comprising a tungsten-halogen light source 1, an electric slit 2, a first integrating sphere 3, a variable aperture stop 4, a second integrating sphere 5, a dark box 6, and Low illumination CMOS chip, light meter 7 and computer 8;

[0013] The electric slit 2 is arranged between the tungsten halogen light source 1 and the light incident surface of the first integrating sphere 3, and the variable aperture stop 4 is arranged between the light exit surface of the first integrating sphere 3 and the light incident surface of the second integrating sphere 5 Between the surfaces, the light-emitting surface of the second integrating sphere 5 is connected to the entrance of the obscura 6, and the low-illuminance CMOS chip to be tested is built in the obscura 6, and the output end of the low-illuminance CMOS chip is connected to the computer 8. Two apertures are used to connect si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More