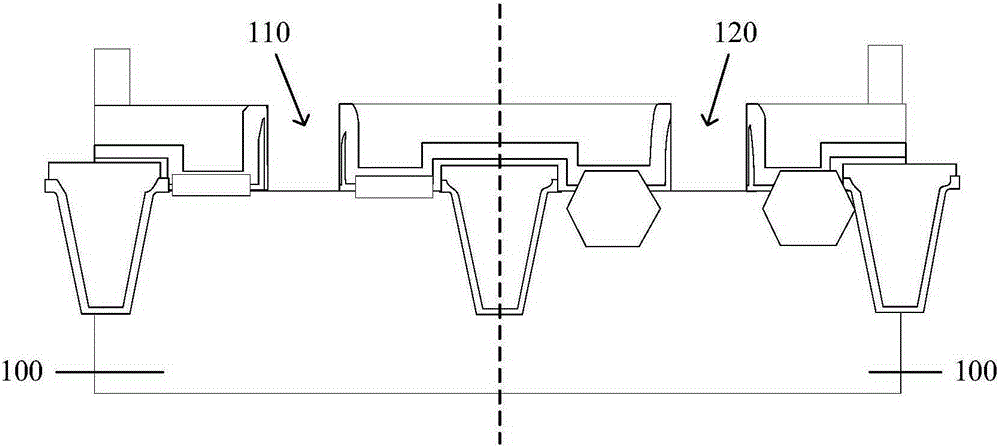

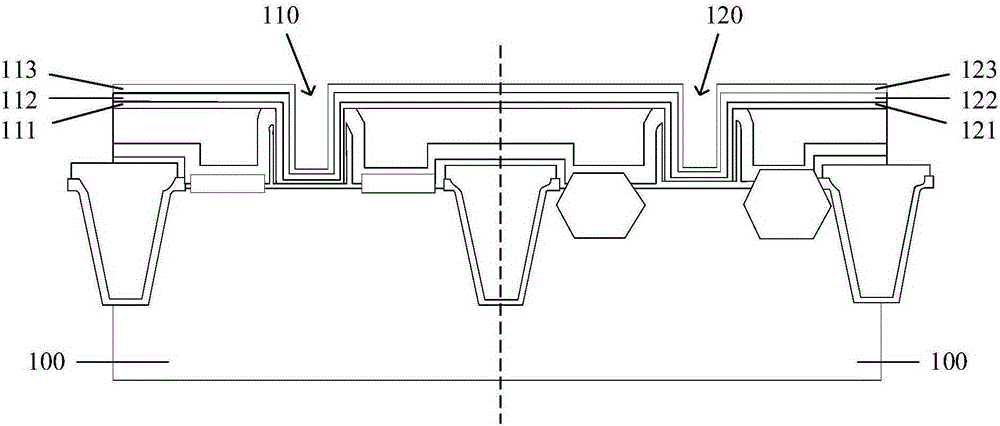

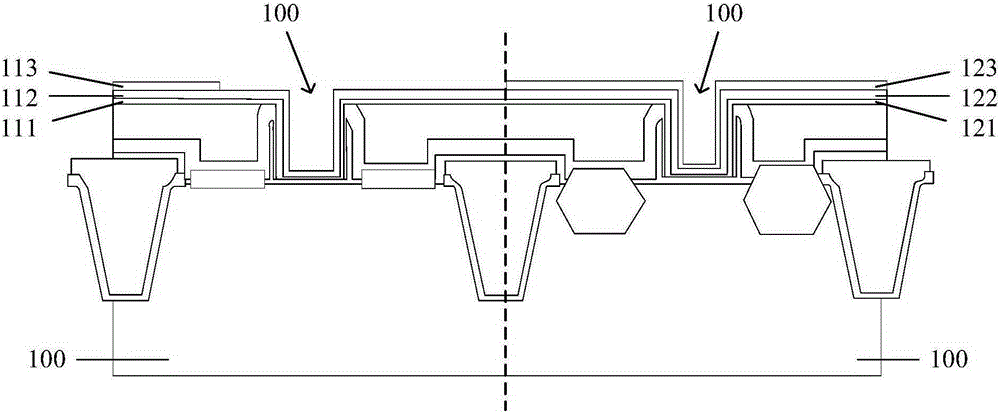

High-K metal gate structure, fin type field effect transistor and manufacturing methods therefor

A technology of metal gate and fabrication method, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as transistor performance mismatch and transistor matching performance degradation, and achieve improved matching performance and stable electrical properties. , the effect of preventing the mismatch problem

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] As mentioned in the background art, the existing manufacturing method easily leads to a decrease in the matching performance of the NMOS transistor and the PMOS transistor. According to the analysis of the inventors, it turns out that in the semiconductor structure using aluminum as the metal gate, the matching performance of transistors (NMOS transistors and PMOS transistors, etc.) is seriously degraded due to the problem of aluminum diffusion; however, for the semiconductor structure using tungsten as the metal gate In the semiconductor structure, although the problem of aluminum diffusion no longer exists, the matching performance of the transistor still decreases. The inventor further analyzed and found that the original tungsten metal gate is formed by chemical vapor deposition (CVD), and when CVD forms a tungsten metal gate, the precursor used is usually tungsten hexafluoride (WF 6 ) or tungsten tetrafluoride (WF 4 ), and the fluorine in tungsten hexafluoride or ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com