Differential architecture storage unit for improving NBTI (Negative Bias Temperature Instability) effect of P-type NVM (Non Volatile Memory)

A storage unit and memory technology, applied in static memory, read-only memory, information storage, etc., can solve problems such as device performance degradation, and achieve the effects of improved stability, reduced power consumption, increased reliability and storage life

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

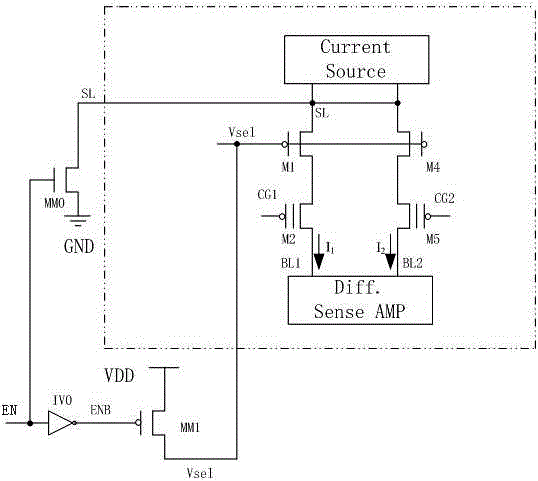

[0056] figure 1 It is based on the traditional floating gate type pFlash storage unit, and adopts a differential architecture on the basis of it, and adds an NBTI recovery circuit at the same time.

[0057] see figure 1 As shown, the basic module is a floating gate type pFlash memory cell. The uppermost module is the constant current source module Current Sourced, which is usually realized by a MOS current source operating in the saturation region. Its advantage is that it is compatible with standard processes and the current is stable. The PMOS transistor M1 and the PMOS transistor M4 are selection transistors, the gate of which is connected to the gate voltage Vsel of the word line, the source is connected to the above-mentioned constant current source module, the drain is respectively connected to the floating gate storage transistor MOS transistor M2 and MOS transistor M5, and the substrate It is directly connected to the source, and the gate voltage Vsel is usually high...

Embodiment 2

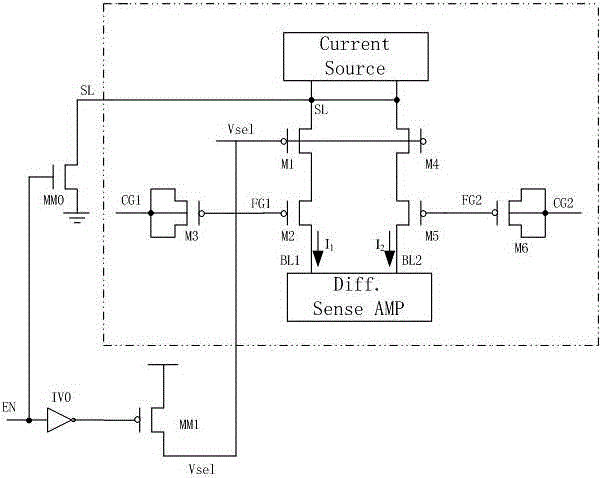

[0061] figure 2 It is a 3TP-type MTP storage unit based on a standard CMOS logic architecture. On the basis of it, a differential architecture is adopted, and an NBTI recovery circuit is added at the same time.

[0062] see figure 2 As shown, the basic module is a 3T MTP storage unit; the top module is a constant current source module Current Sourced, which is usually realized by a MOS current source operating in the saturation region, and its advantage is that it is compatible with standard processes and has a stable current; PMOS tube M1 And the PMOS transistor M4 is a selection transistor, the gate of which is connected to the gate voltage Vsel of the word line, the source is connected to the above-mentioned constant current source module Current Sourced, the drain is respectively connected to the MOS transistor M2 and the MOS transistor M5, and the substrate is directly connected to the source , usually the gate voltage Vsel is high voltage, so there are special require...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More