Method for reducing silicon carbide epitaxial basal plane dislocation density

A silicon carbide, basal plane technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of inappropriate silicon carbide epitaxy process, cumbersome process, surface damage of silicon carbide substrate, etc., to reduce BPD defects , avoid pre-processing, reduce the effect of damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

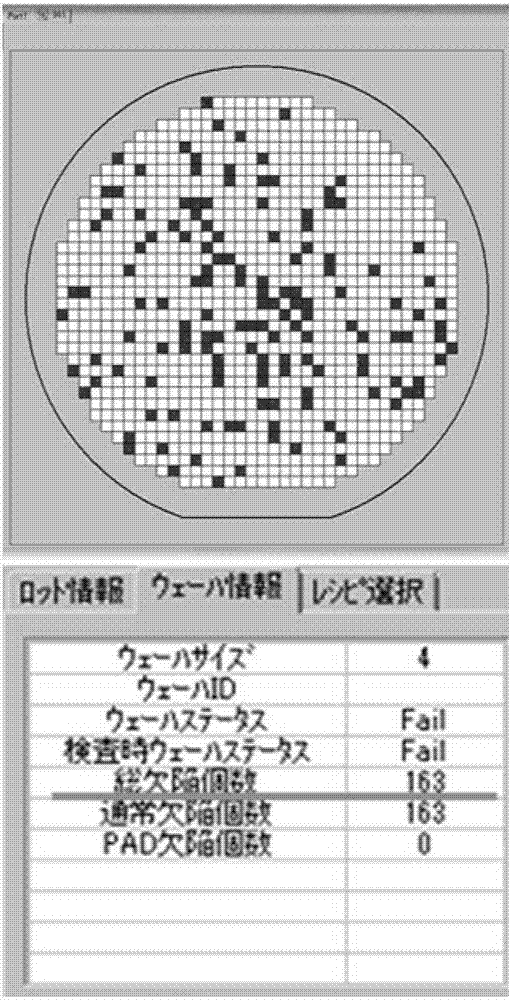

Embodiment 1

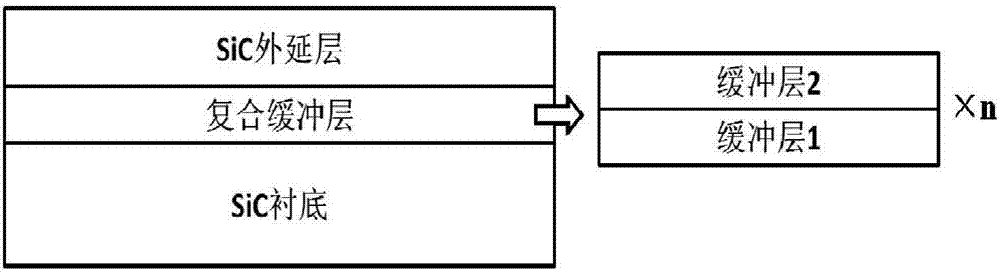

[0035] To grow a SiC epitaxial wafer on a composite buffer layer with a periodic high-low doping structure, the specific steps are as follows:

[0036] (1) Select a silicon carbide substrate with a silicon surface that is 4° to the direction, and the substrate BPD defect density is 1000cm -2 ,, the substrate is placed in the reaction chamber of the SiC epitaxial system, placed on the graphite base, and the graphite base has a tantalum carbide coating;

[0037] (2) Use argon to replace the gas in the reaction chamber several times, introduce hydrogen into the reaction chamber, and gradually increase the H 2 Flow rate to 80L / min, set the pressure of the reaction chamber to 100mbar, gradually raise the temperature of the reaction chamber to the growth temperature of 1600°C, maintain the temperature of the reaction chamber for 10 minutes after reaching the growth temperature, and perform pure hydrogen etching on the substrate;

[0038](3) A small flow of silane (SiH 4 ) and pro...

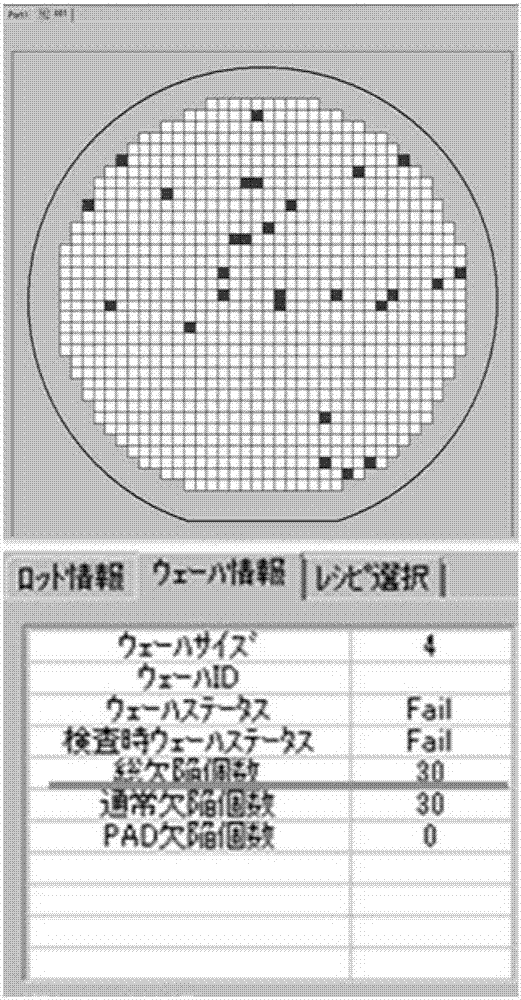

Embodiment 2

[0045] To grow SiC epitaxial wafers on a composite buffer layer with two periods of high-low doping structure, the specific steps are as follows:

[0046] (1) Select a silicon carbide substrate with a silicon surface that is 4° to the direction, and the substrate BPD defect density is 1000cm -2 ,, the substrate is placed in the reaction chamber of the SiC epitaxy system, placed on the graphite base, and the graphite base has a tantalum carbide coating;

[0047] (2) Use argon to replace the gas in the reaction chamber several times, introduce hydrogen into the reaction chamber, and gradually increase the H 2 Flow rate to 80L / min, set the pressure of the reaction chamber to 100mbar, gradually raise the temperature of the reaction chamber to the growth temperature of 1600°C, maintain the temperature of the reaction chamber for 10 minutes after reaching the growth temperature, and perform pure hydrogen etching on the substrate;

[0048] (3) A small flow of silane (SiH 4 ) and p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More