A kind of manufacturing method of high mobility electron transistor

A technology with high mobility and manufacturing methods, which is applied to circuits, electrical components, semiconductor devices, etc., can solve the problems of increasing surface height drop, unfavorable manufacturing process, and increasing the overall thickness of transistors, so as to increase thickness, improve performance, and reduce resistance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

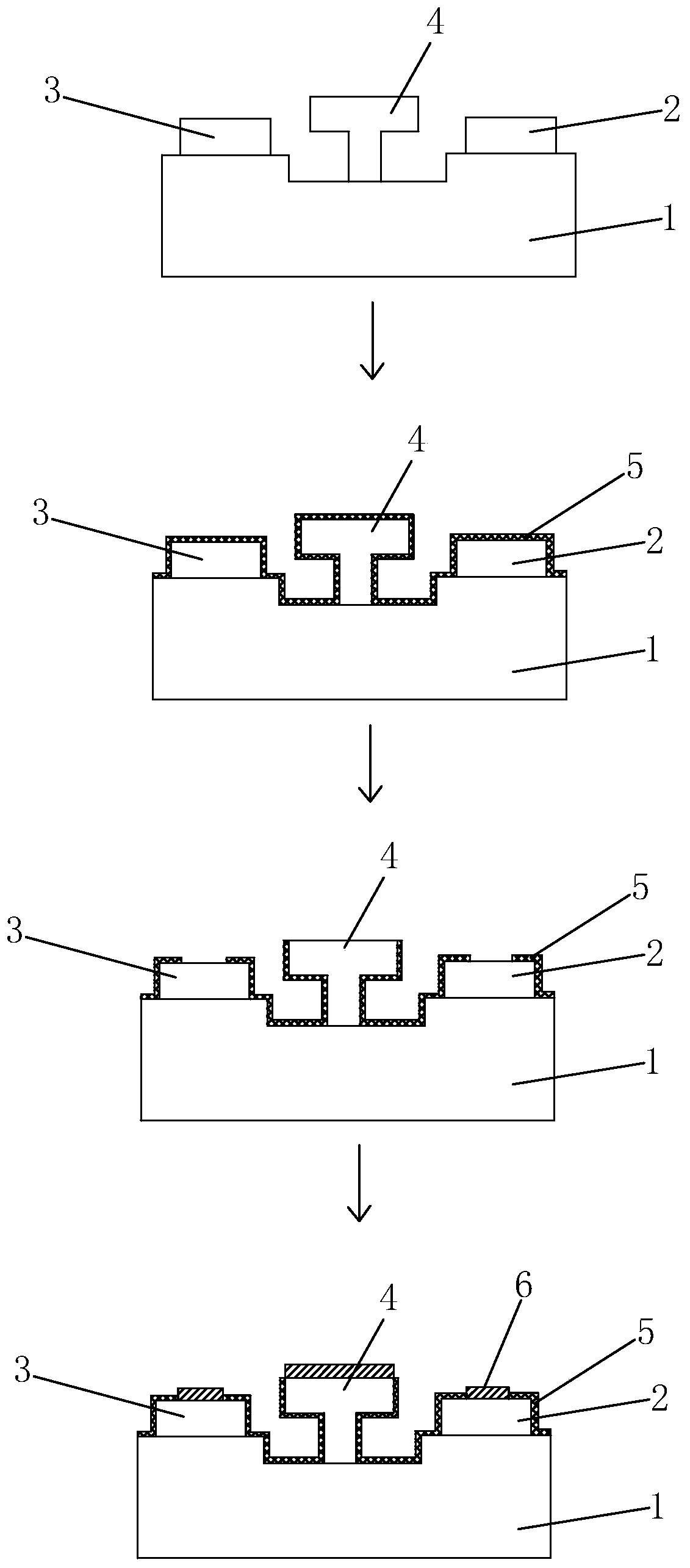

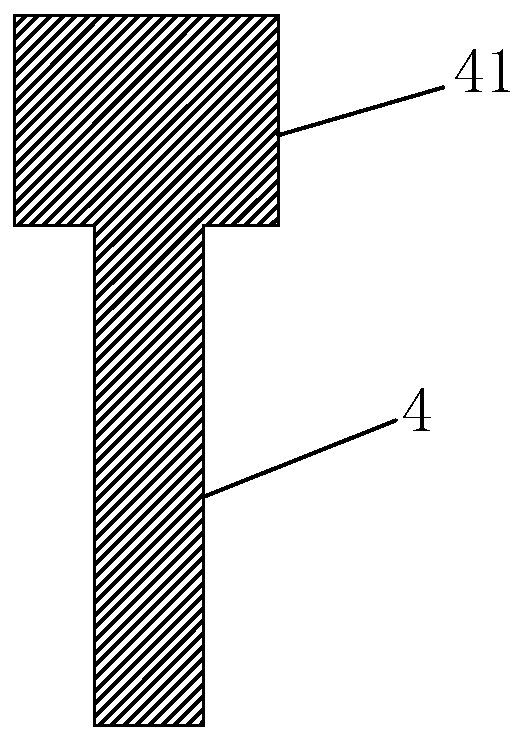

[0026] refer to figure 1 , a kind of manufacturing method of high-mobility electron transistor of embodiment 1, firstly provide the high-mobility electron transistor structure that has finished device manufacturing process, described high-mobility electron transistor structure comprises compound semiconductor substrate 1 and is deposited by metal A source 2, a drain 3 and a gate 4 are formed on a compound semiconductor substrate. The semiconductor substrate 1 can be a group III and V compound semiconductor, such as GaAs, InGaP, InP and the like. The gate 4 is a T-shaped gate structure, and the top line width is greater than the bottom line width. Specifically, the bottom line width is 0.2-0.3 μm, and the top line width is 0.8-1.2 μm. refer to figure 2 , viewed from above, the gate 4 is located between the source 2 and the drain 3 , and its end is expanded to form a lead-out pad 41 . The gate 4 is a Ti / Pt / Au metal composite layer with a thickness of 20-40nm / 20-40nm / 500-700n...

Embodiment 2

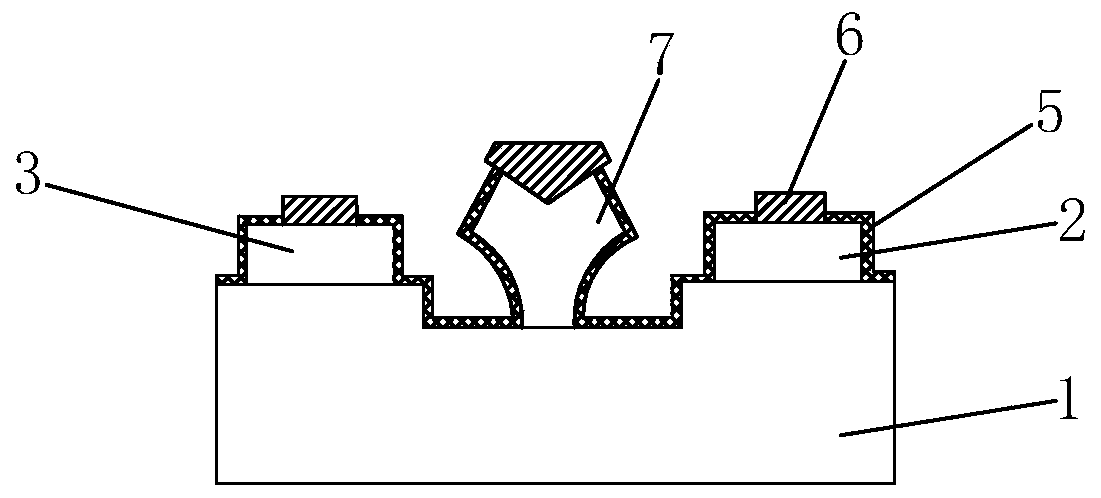

[0032] refer to image 3 The difference between embodiment 2 and embodiment 1 is that the gate 7 has a Y-shaped gate structure, the line width at the bottom is 0.1-0.2 μm, and the line width at the top is 0.7-0.9 μm. The gate 7 is a Ni / Au metal composite layer with a thickness of 10-30nm / 100-300nm, for example, 20nm / 200nm.

[0033] Similarly, during the fabrication of the first metal wiring layer, metal is deposited on the Y-shaped gate with a narrow line width and its lead-out pad at the same time, which increases the thickness of the gate metal layer while realizing the lead-out of the wiring, and reduces the resistance of the gate metal. Floor. Among them, the thickening of the gate metal layer and the metal interconnection are formed in the same metal interconnection process, which is suitable for standard manufacturing processes. While increasing the thickness of the gate metal layer, the overall thickness of the device is not increased, and the large height difference i...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com