Semiconductor device and preparation method thereof, and electronic apparatus

A technology of electronic devices and semiconductors, applied in the direction of microstructure devices, processing microstructure devices, assembling microstructure devices, etc., can solve problems such as chipping, easy to hit the knife, and swaying of the cutting knife, so as to simplify the cutting process and reduce The effect of process cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0048] In order to solve the above-mentioned problems existing in the current technology, the invention provides a method for preparing a semiconductor device, the method comprising:

[0049] A first wafer is provided, the first wafer has a first surface and a second surface oppositely arranged, a first bonding ring is formed on the first surface, and all the outer surfaces of the first bonding ring are A first cutting groove is formed on the edge of the first surface;

[0050] providing a second wafer, the surface of the second wafer is formed with a second bonding ring;

[0051] bonding the first bonding ring to the second bonding ring to bond the first wafer to the second wafer;

[0052] thinning the second surface of the first wafer to expose the first dicing groove and simultaneously exposing the dicing groove region of the second wafer;

[0053] cutting the first wafer and the second wafer.

[0054] Specifically, the widths of the dicing lines on the outside of the fi...

Embodiment 1

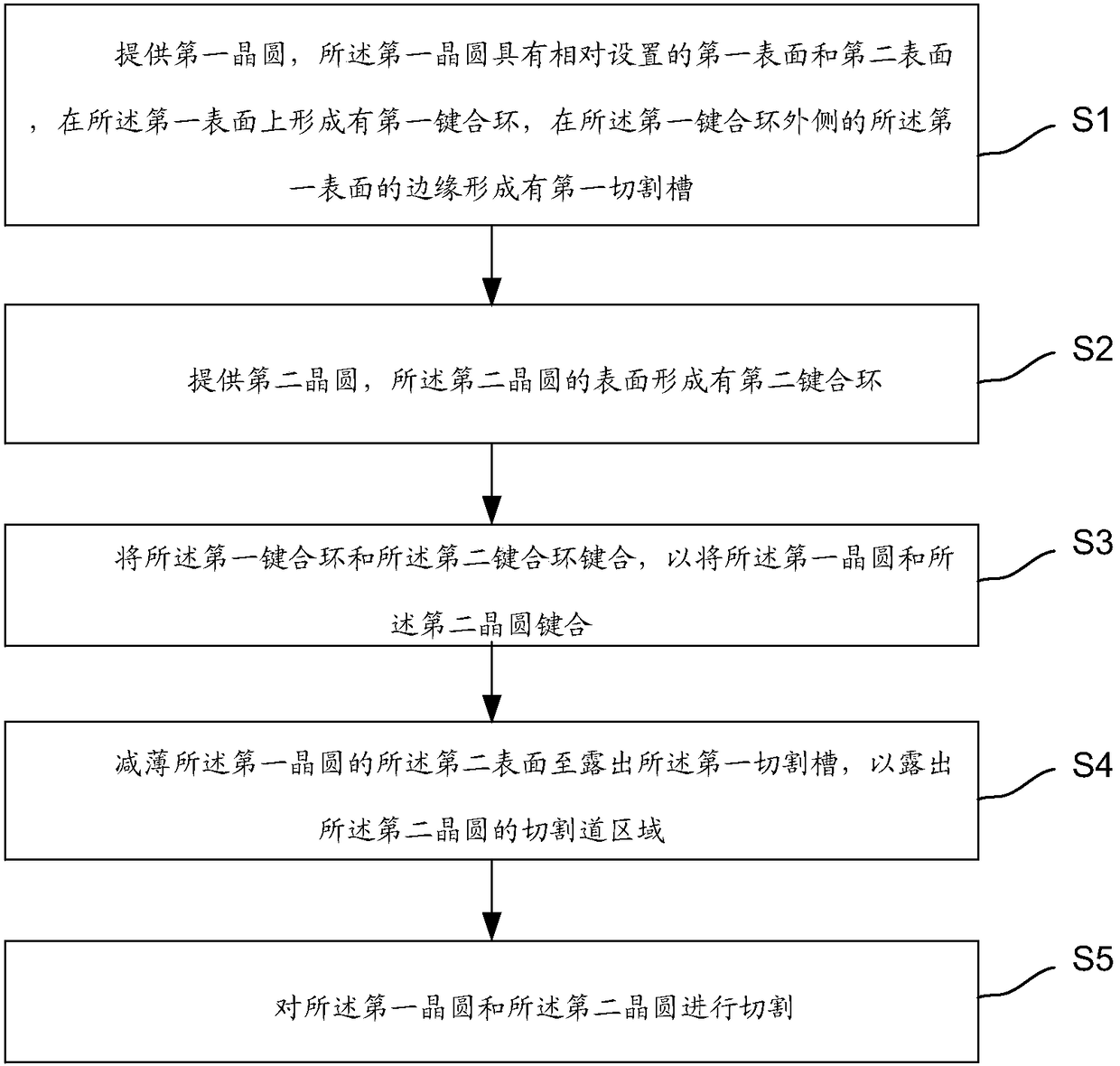

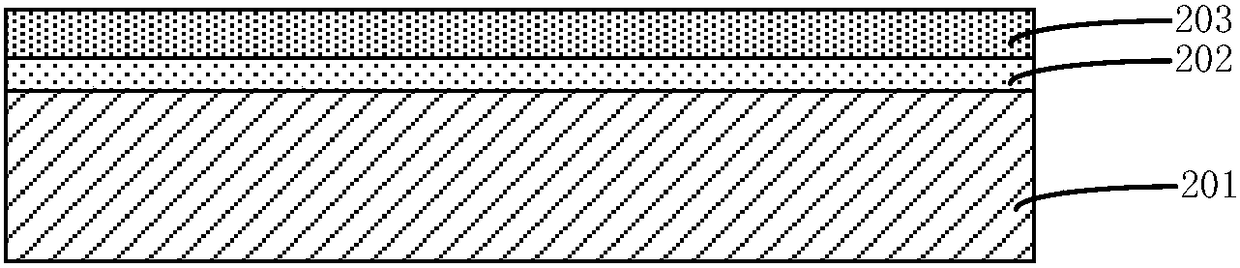

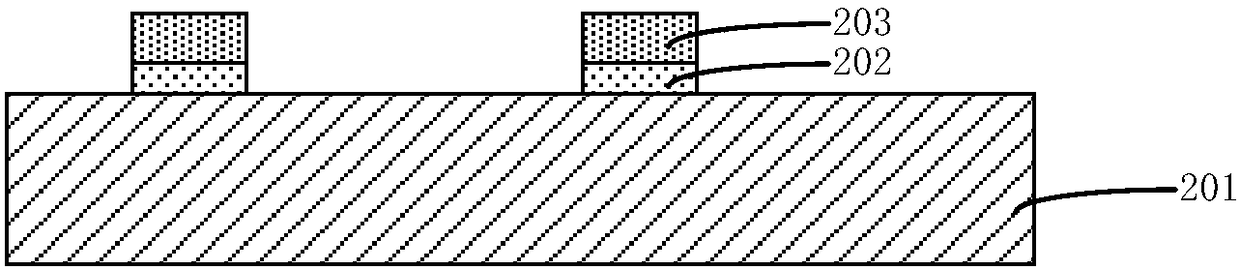

[0069] The preparation method of the semiconductor device of the present invention is described in detail below with reference to the accompanying drawings, figure 1 Shows a flow chart of the fabrication process of the semiconductor device of the present invention; Figures 2A-2H A schematic cross-sectional view of a structure obtained by implementing the method for manufacturing a semiconductor device according to an embodiment of the present invention is shown.

[0070] The invention provides a method for preparing a semiconductor device, such as figure 1 As shown, the main steps of the preparation method include:

[0071] Step S1: providing a first wafer, the first wafer has a first surface and a second surface oppositely arranged, a first bonding ring is formed on the first surface, and a first bonding ring is formed on the first bonding ring A first cutting groove is formed on the edge of the first surface on the outer side;

[0072] Step S2: providing a second wafer, ...

Embodiment 2

[0134] The present invention also provides a semiconductor device, which is prepared by the method described in the first embodiment.

[0135] The semiconductor device includes:

[0136] first wafer;

[0137] a first dicing groove and a second dicing groove located in the first wafer;

[0138] A second wafer, where the second wafer is integrated with the first wafer.

[0139] The first wafer 201 may be at least one of the materials mentioned below: silicon, silicon-on-insulator (SOI), silicon-on-insulator (SSOI), silicon-germanium-on-insulator (S-SiGeOI) and Silicon germanium on insulator (SiGeOI), etc.

[0140] In the present invention, the semiconductor device can be a MEMS device, the first wafer 201 is a cover wafer, the second wafer is a MEMS wafer, and pressure sensors and acceleration sensors can be formed on the MEMS wafer. , CMOS image sensors, etc., as well as conventional devices such as active devices, other MEMS devices, and interconnect structures.

[0141] ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com