NAND gate flash memory without junction in rear grid and manufacturing method of flash memory

The technology of a flash memory and its manufacturing method is applied in the field of gate-back non-junction NAND flash memory and its manufacture, which can solve the problems of large memory size, high process difficulty, complex structure, etc., and achieve simple memory structure and high channel current. Ease of control, effect of increasing memory cell density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

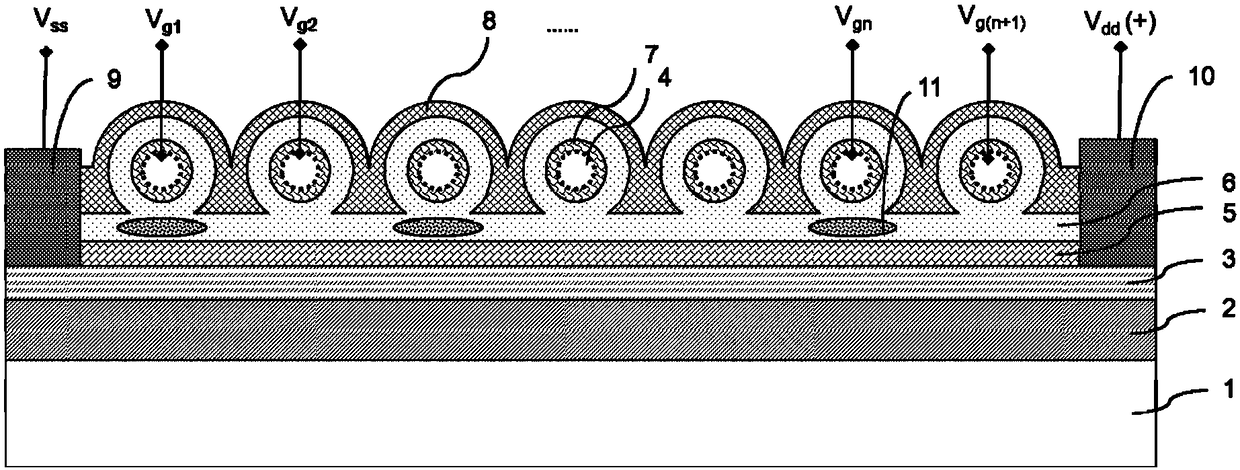

[0063] The present invention provides a gate-last non-junction NAND flash memory, please refer to figure 1 , shown as a schematic diagram of the structure of the memory, including:

[0064] substrate1;

[0065] an insulating layer 2 located on the substrate 1;

[0066] The channel layer 3 is located on the insulating layer 2 and adopts a two-dimensional semiconductor material;

[0067] A grid array of carbon nanotubes, suspended above the channel layer 3, including a number of discrete carbon nanotubes 4, the carbon nanotubes 4 are used as gate electrodes of transistors in the memory;

[0068] The gate trapping structure includes a tunnel layer 5, a charge trapping layer 6, and a blocking layer 7; wherein, the tunneling layer 5 is located on the channel layer 3, and the blocking layer 7 surrounds the outer surface of the carbon nanotube 4, The charge trapping layer 6 includes a first portion surrounding the outer surface of the blocking layer 7 and a second portion located ...

Embodiment 2

[0081] The present invention also provides a method for fabricating a gate-back non-junction NAND flash memory, comprising the following steps:

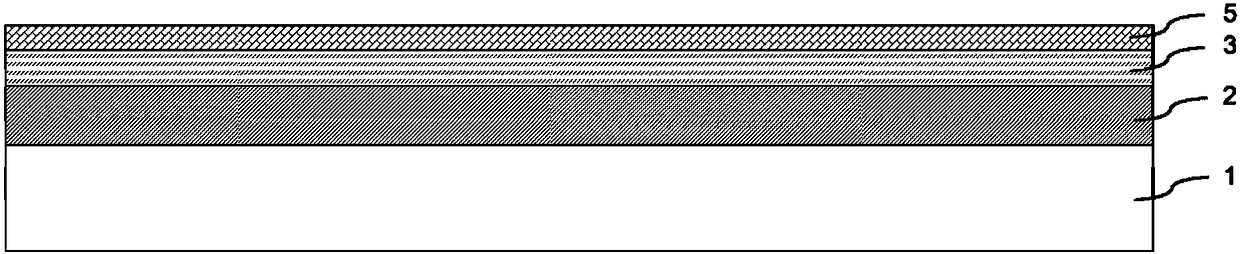

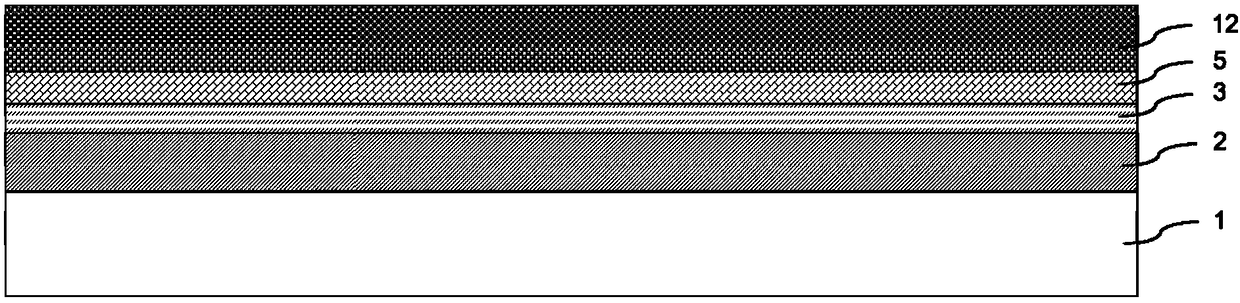

[0082] See first figure 2 A substrate 1 is provided, and an insulating layer 2 , a two-dimensional semiconductor material channel layer 3 and a tunnel layer 4 are sequentially formed on the substrate 1 from bottom to top.

[0083] Specifically, the substrate 1 includes, but is not limited to, a suitable semiconductor substrate such as silicon, germanium, and silicon germanium, and the insulating layer 2 includes, but not limited to, a suitable insulating material such as silicon oxide. For example, the insulating layer may be formed by growing an oxide layer on a silicon substrate.

[0084] The channel layer 3 is made of two-dimensional semiconductor material with a thickness of 1-10 atomic layers. As an example, the two-dimensional semiconductor material is selected from MoS 2 、WS 2 、ReS 2 And any one of SnO, in this embodimen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More