Superjunction-based integrated power device and manufacturing method thereof

A technology of integrated power and manufacturing methods, which is applied in the field of power semiconductor devices, can solve the problems of circuit miniaturization, large occupied area, and high integration level, and is beneficial to system integration and miniaturization, low cost, and high reliability. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

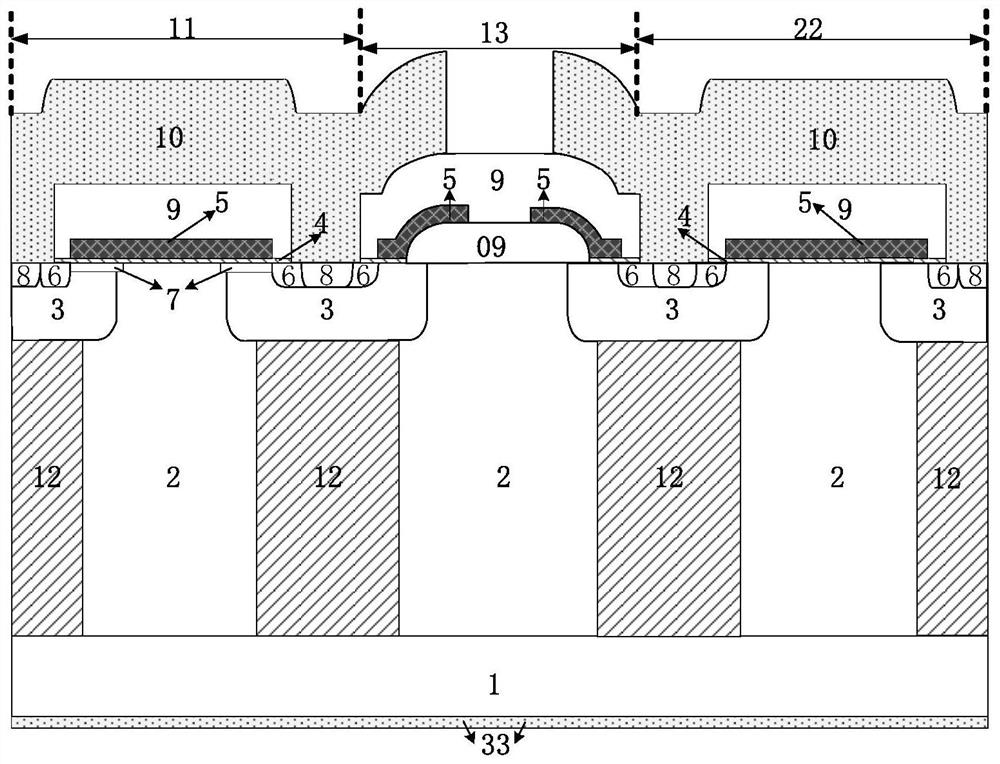

[0048] Such as figure 1 As shown, a superjunction-based integrated power device, its cell structure includes a first doping type substrate 1, and the first doping type substrate 1 is provided with an enhancement superjunction MOSFET 22, a depletion superjunction MOSFET Junction MOSFET11 and an isolation structure 13, two super-junction MOSFET devices share the drain, the isolation structure 13 is arranged between the enhanced super-junction MOSFET22 and the depletion-type super-junction MOSFET11, and the drain metal is arranged under the substrate 33;

[0049] The enhanced super junction MOSFET 22 includes second doping type strips 12 and first doping type strips 2 alternately arranged on the first doping type substrate 1, and the second doping type strips 12 and first doping type strips alternately arranged Above the doping type strip 2 are two second doping type well regions 3; two first doping type heavily doped source regions 6 are respectively arranged in the second dopi...

Embodiment 2

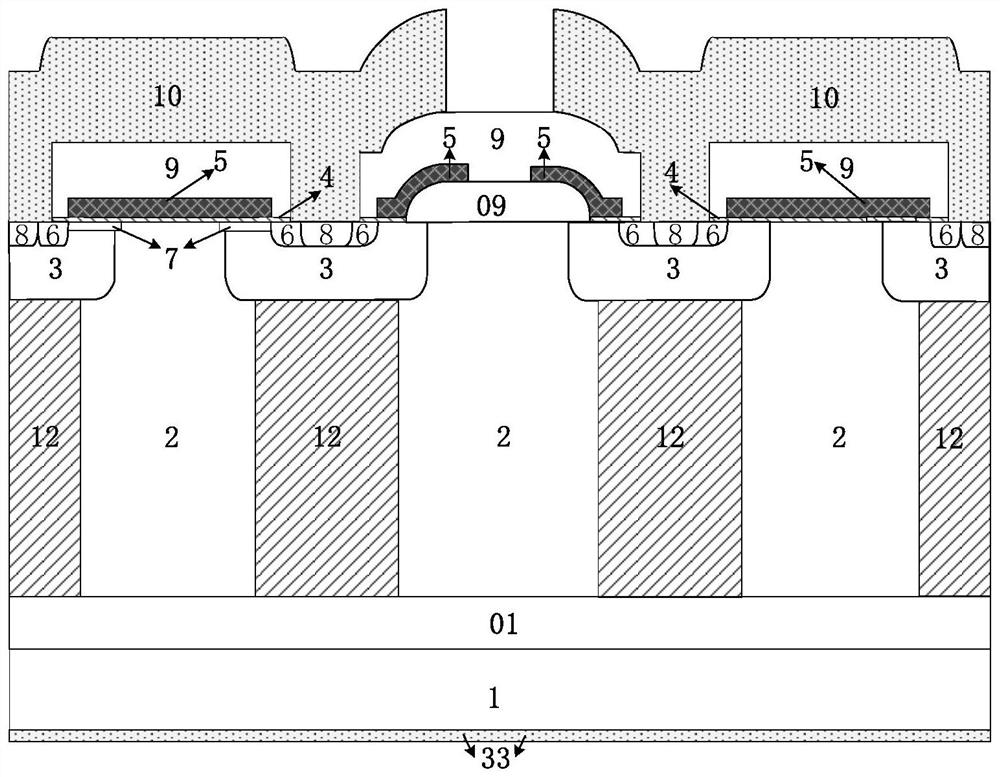

[0076] Such as figure 2As shown, a superjunction-based integrated power device of this embodiment differs from Embodiment 1 in that: the substrate 1 of the first doping type alternates with strips 12 of the second doping type and the first doping type The first doping type doping Buffer layer 01 is arranged between the drift regions formed by the impurity type strips 2 .

Embodiment 3

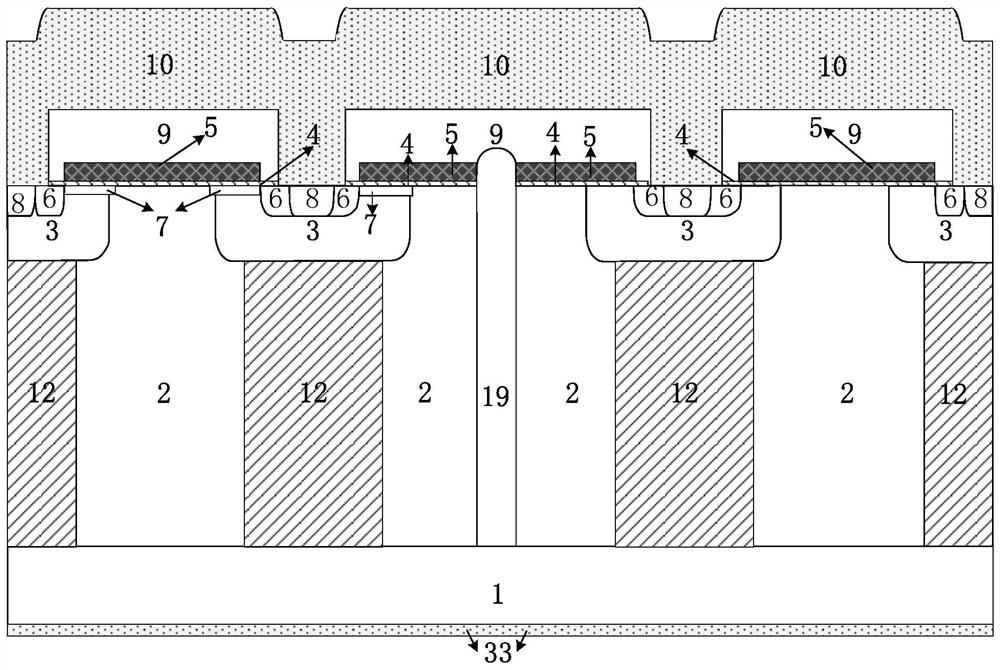

[0078] Such as image 3 As shown, a superjunction-based integrated power device of this embodiment differs from Embodiment 1 in that: the isolation structure formed by combining the second doping type well region 3 and the second doping type strip 12 uses A single complete strip of media 19 is substituted.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More