Deep silicon etching method based on SOG wafers

A deep silicon etching and wafer technology, which is used in the process of producing decorative surface effects, decorative arts, gaseous chemical plating, etc. Etch depth, unrealizable bulk silicon structure, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

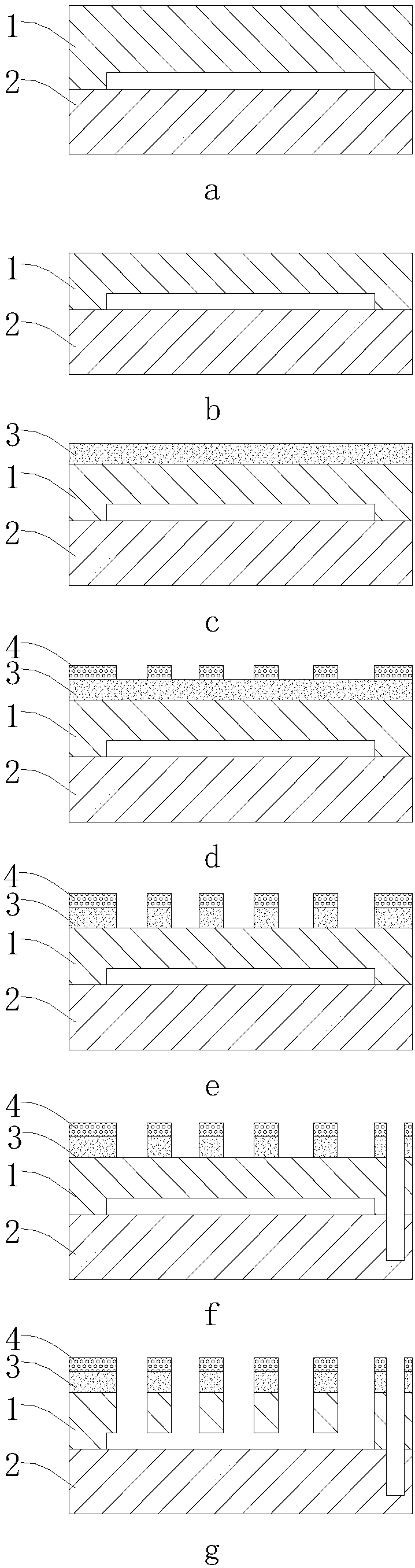

[0042] process such as figure 1 shown.

[0043] a. Silicon structure layer-glass substrate bonding:

[0044] The silicon structure layer 1 with anchor points and the glass substrate 2 with conductive leads are bonded to complete the silicon structure layer-glass substrate bonding process to form an SOG wafer with a diameter of 6 inches. The parameters of the bonding process are: the temperature of the process chamber is 350°C, the pressure of the process chamber is 5×10-4mbar, the bonding pressure is 600N, the bonding voltage is 800V, and the bonding time is 90s.

[0045] b. Thinning the silicon structure layer:

[0046] Using a KOH solution with a temperature of 80° C. and a concentration of 30%, soaking the silicon structure layer for 1200 min, and thinning the silicon structure layer 1 of the SOG wafer to a required thickness of 80 μm. After soaking, rinse with water for 5 times, and then use a spin dryer to spin dry at a speed of 2000 rpm for 5 minutes, and fill the spi...

Embodiment 2

[0065] process such as figure 1 shown.

[0066] a. Silicon structure layer-glass substrate bonding:

[0067] The silicon structure layer 1 with anchor points and the glass substrate 2 with conductive leads are bonded together to form a 6-inch diameter SOG wafer. The parameters of the bonding process are: the temperature of the process chamber is 350°C, the pressure of the process chamber is 5×10-4mbar, the bonding pressure is 600N, the bonding voltage is 800V, and the bonding time is 90s.

[0068] b. Thinning the silicon structure layer:

[0069] Using a KOH solution with a temperature of 80° C. and a concentration of 30%, soaking the silicon structure layer for 1200 min, and thinning the silicon structure layer 1 of the SOG wafer to a required thickness of 80 μm. After soaking, rinse with water for 5 times, and then use a spin dryer to spin dry at a speed of 2000 rpm for 5 minutes, and fill the spin dryer with hot nitrogen at 50°C and 20 LPM.

[0070] c. Deposition of SiO...

Embodiment 3

[0088] process such as figure 1 shown.

[0089] a. Silicon structure layer-glass substrate bonding:

[0090] The silicon structure layer 1 with anchor points and the glass substrate 2 with conductive leads are bonded to complete the silicon structure layer-glass substrate bonding process to form an SOG wafer with a diameter of 6 inches. The parameters of the bonding process are: the temperature of the process chamber is 350°C, the pressure of the process chamber is 5×10-4mbar, the bonding pressure is 600N, the bonding voltage is 800V, and the bonding time is 90s.

[0091] b. Thinning the silicon structure layer:

[0092] Using a KOH solution with a temperature of 80° C. and a concentration of 30%, soaking the silicon structure layer for 1200 min, and thinning the silicon structure layer 1 of the SOG wafer to a required thickness of 80 μm. After soaking, rinse with water for 5 times, and then use a spin dryer to spin dry at a speed of 2000 rpm for 5 minutes, and fill the spi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Etching depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More