Flexible epitaxial ferroelectric-gate thin-film transistor and preparation method thereof

A thin film transistor and ferroelectric thin film technology, applied in the field of flexible epitaxial ferroelectric gate thin film transistor and its preparation, can solve the problems of no high temperature resistance, slow reading speed, easy polarization fatigue and the like, and achieve excellent high temperature resistance performance, Overcome the effects of poor bonding, good lattice matching

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

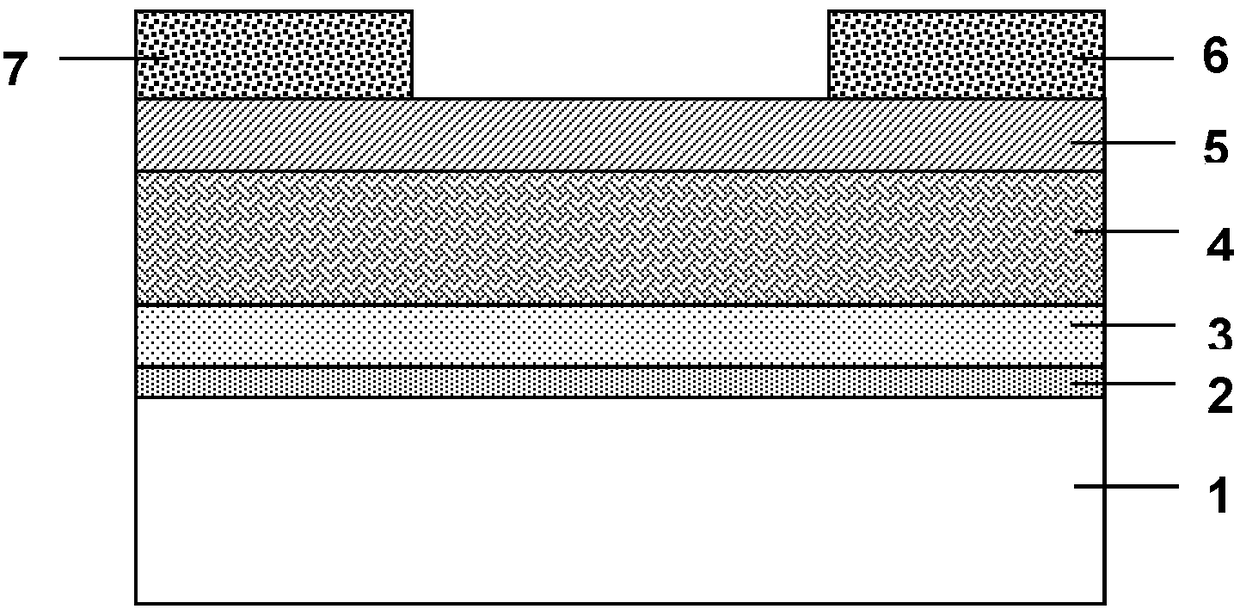

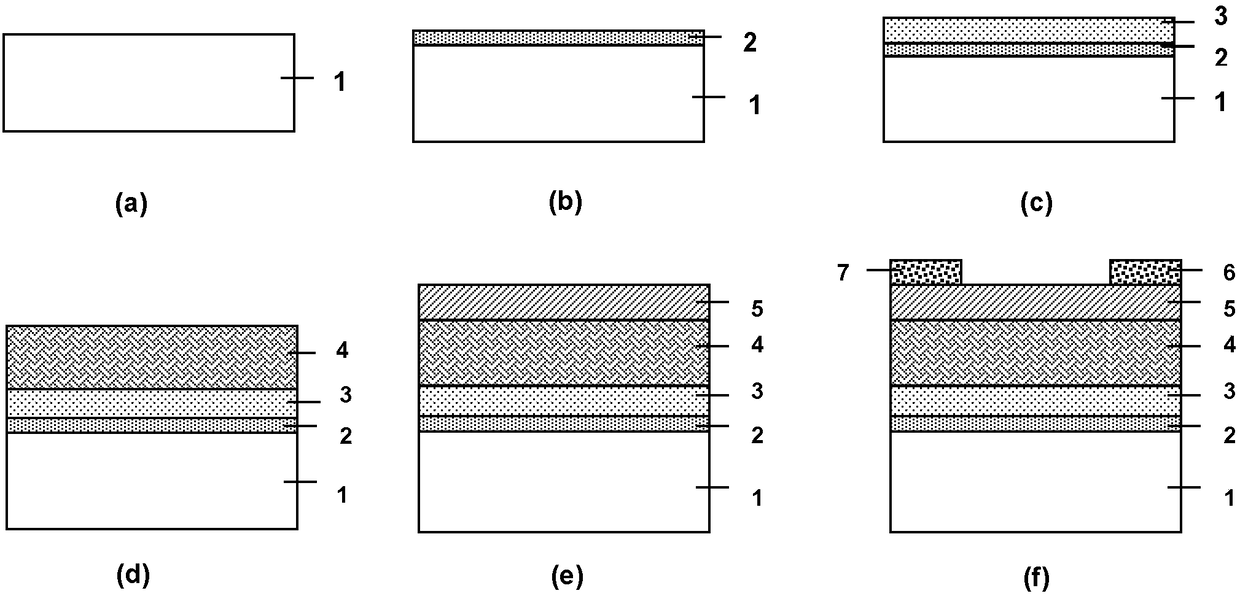

[0067] like figure 1 As shown, Embodiment 1 discloses a flexible epitaxial ferroelectric gate thin film transistor, comprising: a mica flexible substrate 1; a buffer layer 2 formed on the mica substrate 1; a bottom gate electrode 3 formed on the buffer layer 2; The epitaxial ferroelectric thin film layer 4 formed on the bottom gate electrode 3; the channel layer 5 formed on the epitaxial ferroelectric thin film layer 4; the source electrode 6 formed on the channel layer 5; The drain electrode 7 is formed by separating the source electrode.

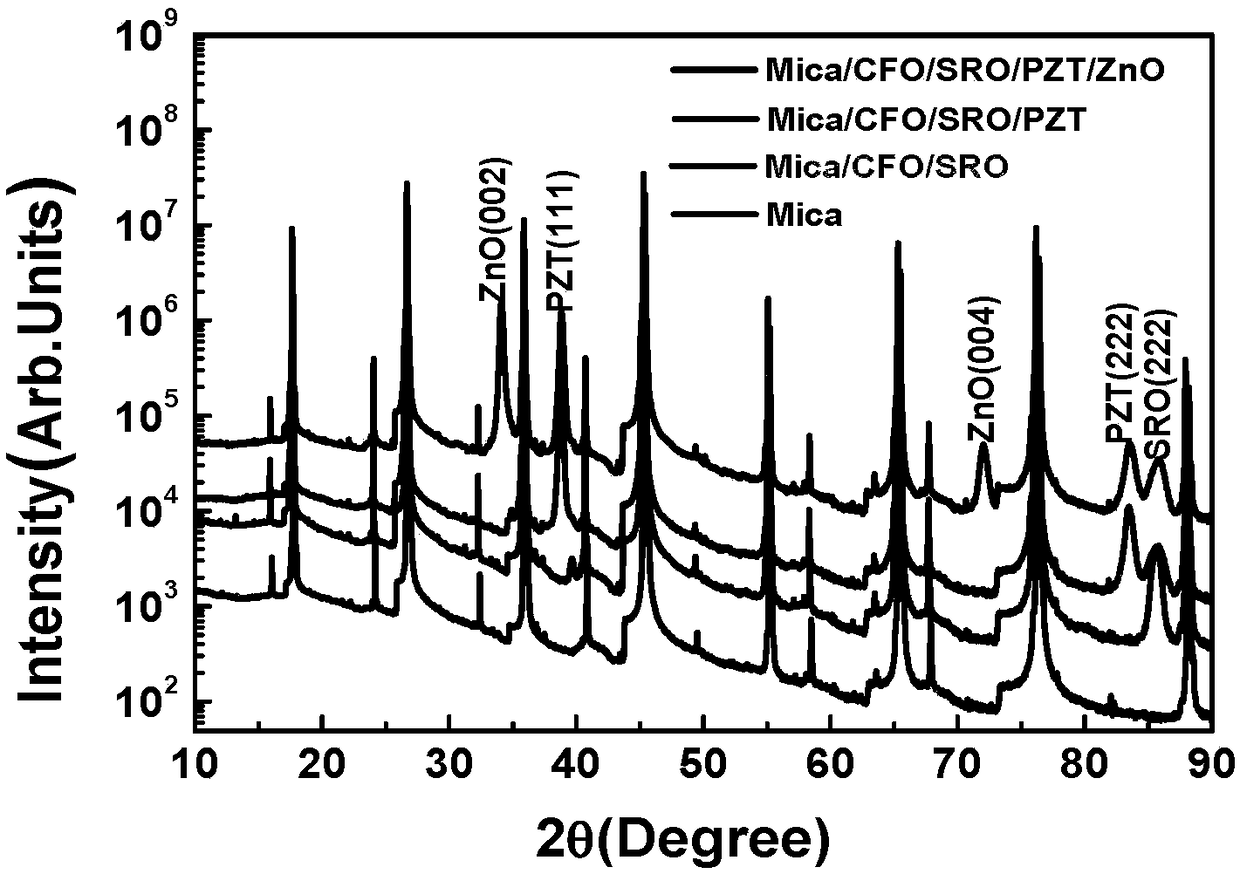

[0068] The ferroelectric thin film layer 4 is composed of a lead zirconate titanate thin film material, and the ratio of the amounts of Pb, Zr and Ti in the lead zirconate titanate thin film material is 1:0.1:0.9; the thickness of the ferroelectric thin film layer 4 is 150 nm; 1 is composed of natural mica material with a thickness of 20 μm; the buffer layer 2 is composed of CoFe 2 O 4 It is composed of thin film material, and the thick...

Embodiment 2

[0077] Embodiment 2 discloses a flexible epitaxial ferroelectric gate thin film transistor, such as figure 1 shown, including:

[0078] Mica flexible substrate 2;

[0079] The buffer layer 2 formed on the mica substrate 1;

[0080] The bottom gate electrode 3 formed on the buffer layer 2;

[0081] an epitaxial ferroelectric thin film layer 4 formed on the bottom gate electrode 3;

[0082] The channel layer 5 formed on the epitaxial ferroelectric thin film layer 4;

[0083] The source electrode 6 formed on the channel layer 5;

[0084] and a drain electrode 7 formed on the channel layer and separated from the source electrode.

[0085] The ferroelectric thin film layer 4 is composed of a lead zirconate titanate thin film material, and the ratio of the amounts of Pb, Zr, and Ti in the lead zirconate titanate thin film material is 1:0.2:0.8; the thickness of the ferroelectric thin film layer 4 is 120 nm; Substrate 1 is composed of natural mica material with a thickness of 1...

Embodiment 3

[0094] Embodiment 3 discloses a flexible epitaxial ferroelectric gate thin film transistor, such as figure 1 shown, including:

[0095] Mica flexible substrate 2;

[0096] A buffer layer 2 formed on the mica substrate 1;

[0097] a bottom gate electrode 3 formed on the buffer layer 2;

[0098] The epitaxial ferroelectric thin film layer 4 formed on the bottom gate electrode 3;

[0099] A channel layer 5 formed on the epitaxial ferroelectric thin film layer 4;

[0100] a source electrode 6 formed on the channel layer 5;

[0101] and a drain electrode 7 formed on the channel layer and separated from the source electrode.

[0102] The ferroelectric thin film layer 4 is composed of lead zirconate titanate thin film material, the ratio of the amount of Pb, Zr, and Ti substances in the lead zirconate titanate thin film material is 1:0.3:0.7; the thickness of the ferroelectric thin film layer 4 is 180nm; Substrate 1 is composed of natural mica material with a thickness of 30 μm...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More