A lateral MOSFET device and a method for fabricate that same

A device and lateral technology, applied in the field of power semiconductors, can solve the problems of poor reliability, poor reverse recovery characteristics, and high power loss, achieve good shielding effect, reduce the electric field level, and improve the electric field concentration effect.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

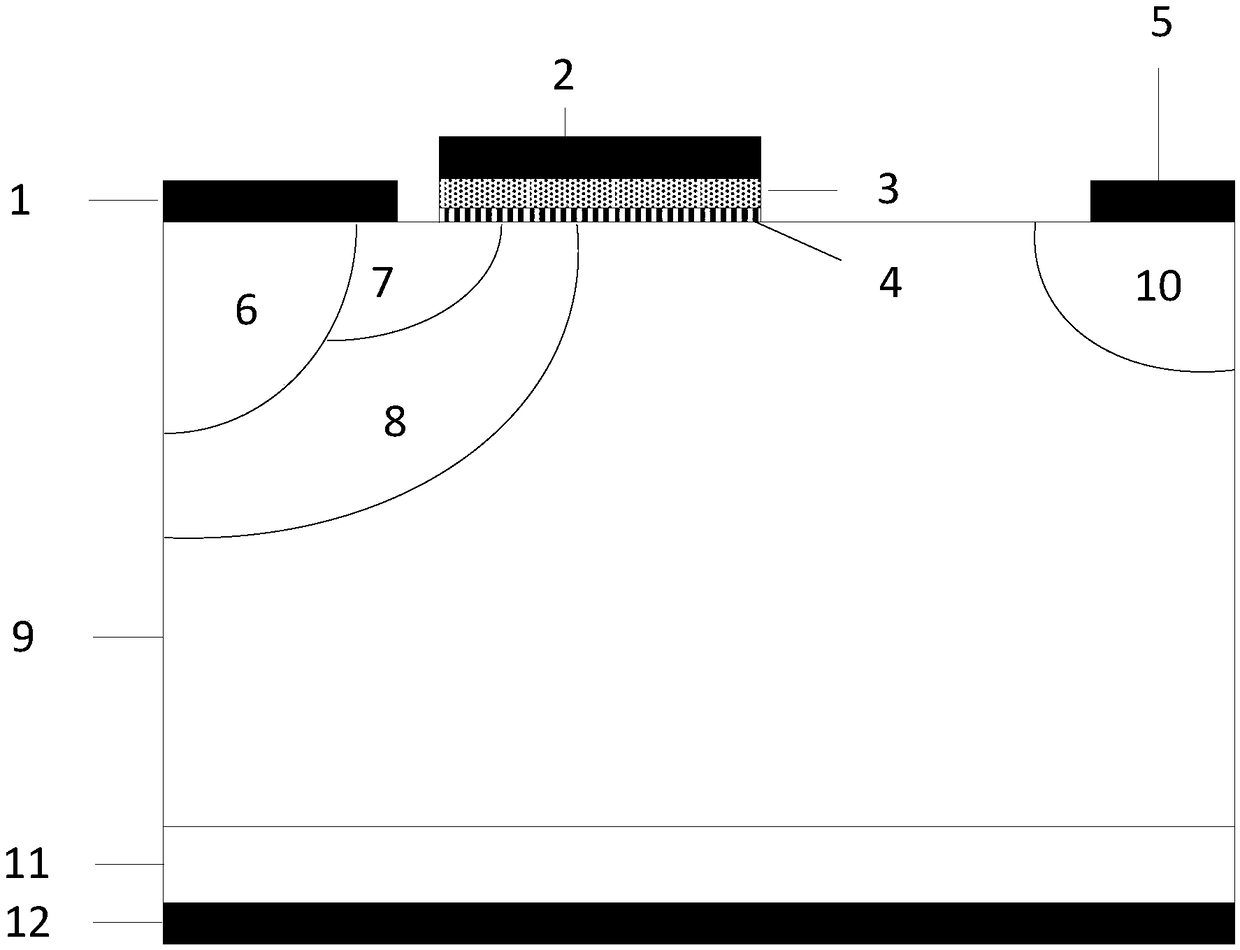

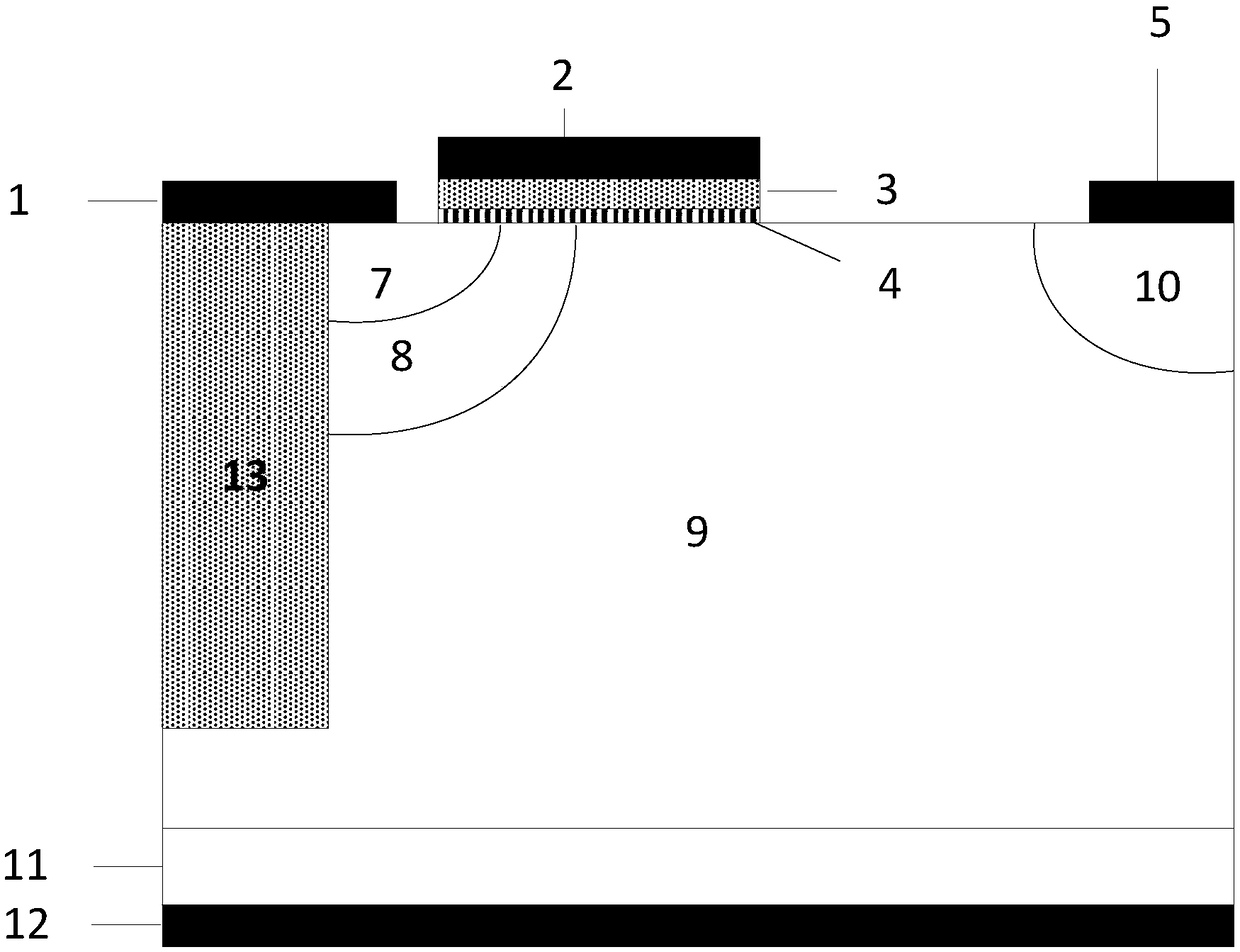

[0098] In a lateral silicon carbide MOSFET provided in this embodiment, the device cell structure is as follows: figure 2 As shown, it includes a substrate electrode 12, a P-type silicon carbide substrate 11 and a silicon carbide N- epitaxial layer 9 stacked vertically from bottom to top, and the top layer on one side of the N-type silicon carbide epitaxial layer 9 is provided with silicon carbide N type drain region 10, the top layer on the other side is provided with a silicon carbide N+ source region 7; the upper surface of the silicon carbide N-type drain region 10 is provided with a drain metal 5; it is characterized in that: the silicon carbide N- epitaxial layer 9 The top layer is also provided with a polysilicon region 13; the polysilicon region 13 is adjacent to the silicon carbide N+ source region 7 and is arranged on the side away from the drain metal 5; the upper surface of the polysilicon region 13 and part of the silicon carbide N+ source region 7 The upper surf...

Embodiment 2

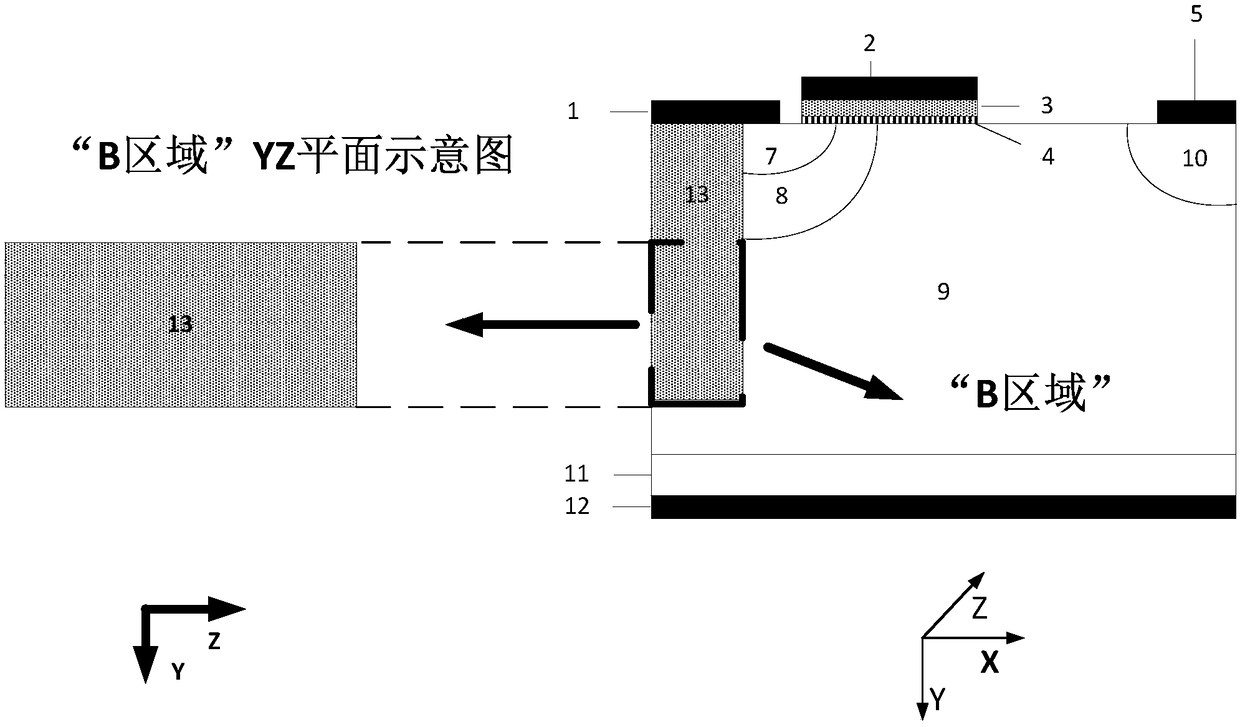

[0101] A lateral silicon carbide MOSFET provided in this embodiment, the cell structure of the device in this embodiment is as follows Figure 4 As shown, it differs from Embodiment 1 in that the bottom layer of the polysilicon region 13 of the present invention is set as independent polysilicon partitions, and several narrow-bandgap semiconductor partitions are isolated by the N- epitaxial layer 9 . like Figure 4 Shown in the "Area B" area. The conventional design of embodiment 1 same area is as image 3 shown. In this embodiment, the contact area between the integrated diode device and the silicon carbide N-epitaxy 9 is increased, so as to have better on-state performance of the diode.

Embodiment 3

[0103] A lateral silicon carbide MOSFET provided in this embodiment, the cell structure of the device in this embodiment is as follows Image 6 As shown, it differs from Embodiment 1 in that the lateral silicon carbide MOSFET device also has a three-dimensional gate structure, such as Image 6 Shown in area C. The three-dimensional gate structure increases the channel area of the device during forward conduction, thereby optimizing the forward performance of the MOSFET;

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More