Nanowire transistor and forming method thereof

A transistor and nanowire technology, applied in the field of nanowire transistors and their formation, can solve the problems of large parasitic capacitance and poor performance of nanowire transistors, and achieve the effect of reducing parasitic capacitance and improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] There are many problems in the nanowire transistor in the prior art, for example, the parasitic capacitance between the gate and the source-drain doped layer is large, and the performance of the nanowire transistor is poor.

[0035] In combination with a method for forming a nanowire transistor, the reason why the performance of the nanowire transistor is poor due to the large parasitic capacitance between the gate and the source-drain doped layer of the nanowire transistor formed in the prior art is analyzed:

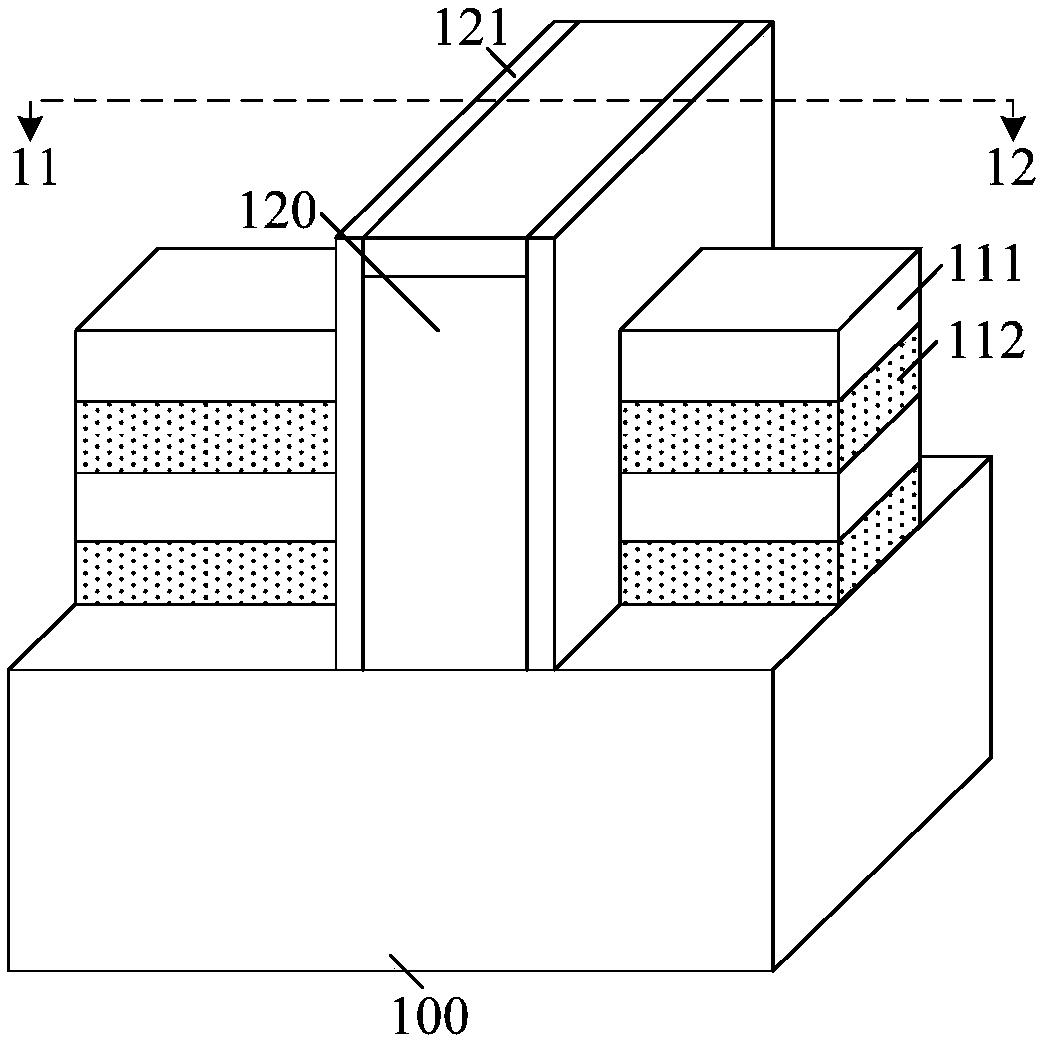

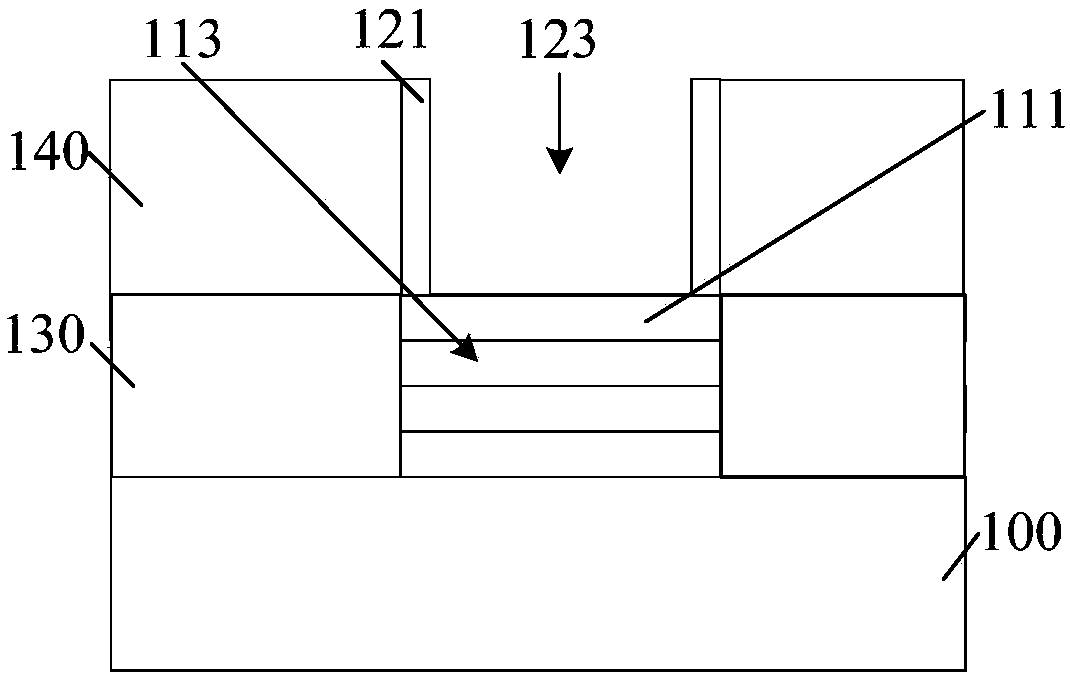

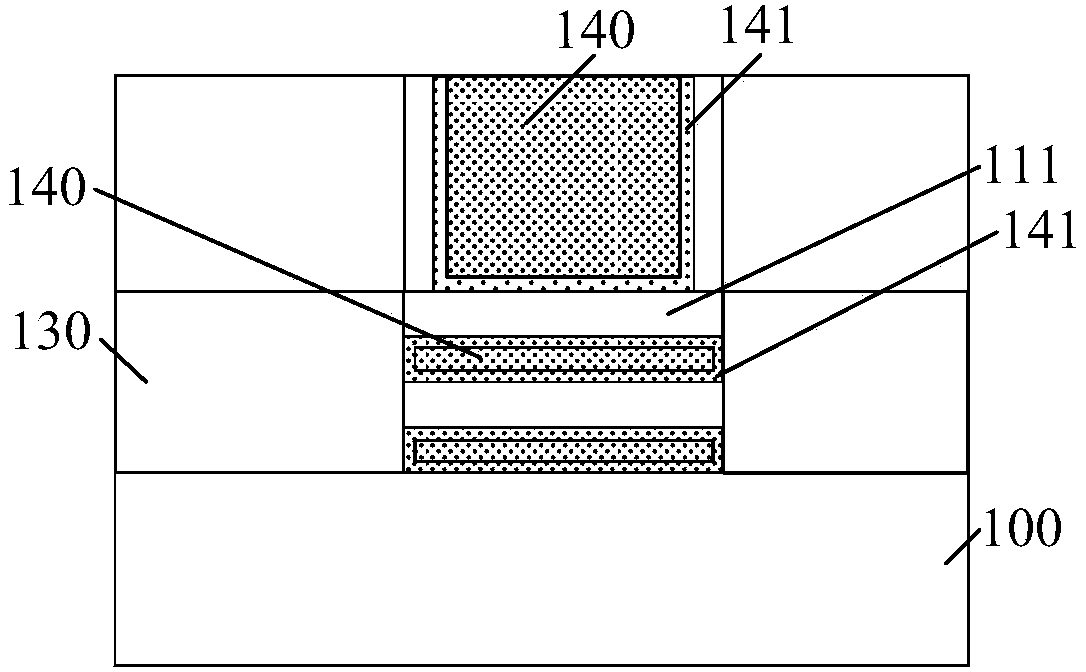

[0036] Figure 1 to Figure 3 It is a structural schematic diagram of each step of a method for forming a nanowire transistor.

[0037] Please refer to figure 1 , providing a substrate 100; forming a combined structure on the substrate 100, the combined structure includes a plurality of stacked combined layers, the combined layer includes a sacrificial layer 112 on the substrate 100 and a sacrificial layer located on the channel layer 111 on the sacrificial lay...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More