Semiconductor device and manufacturing method thereof

A manufacturing method and semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as bump voids, prevent voids, improve roughness, and increase polishing time. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

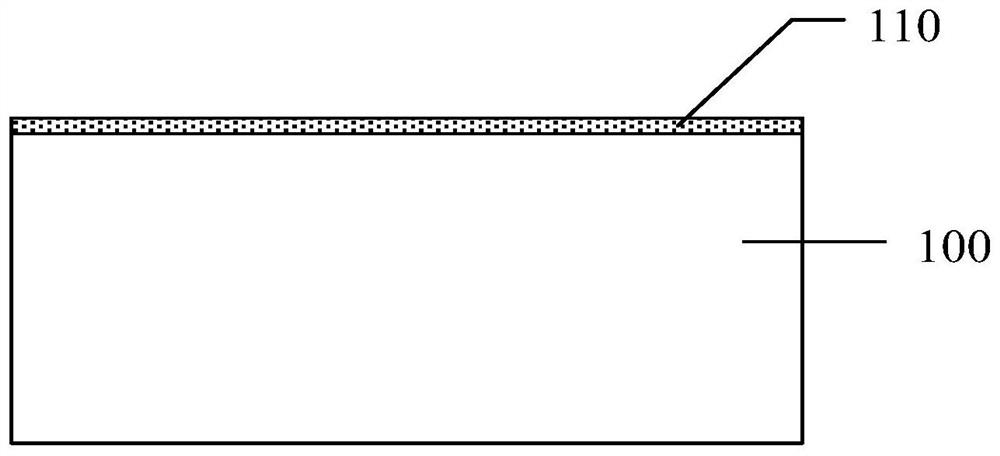

[0030] Figure 2 to Figure 6 It is a structural diagram corresponding to each step of forming a semiconductor device according to the first embodiment of the present invention. refer to figure 2 , providing a substrate 100 on which a metal oxide layer 110 is formed.

[0031] In this embodiment, the method for forming the metal oxide layer 110 may be chemical vapor deposition. The material of the metal oxide layer may be zinc oxide or aluminum oxide.

[0032] In this embodiment, the base 100 may be a semiconductor substrate, or a semiconductor substrate on which other semiconductor elements have been formed.

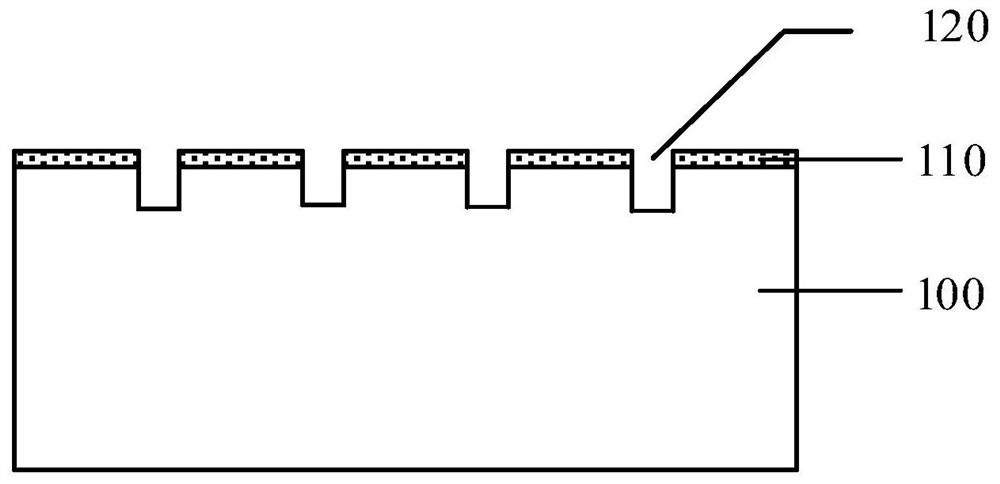

[0033] refer to image 3 , etching the metal oxide layer 110 and the substrate 100 to form a trench 120 .

[0034] In this embodiment, the method for etching the metal oxide layer 110 and the substrate 100 may be a dry etching process, and the gas used is C 4 f 8 or CF 4 .

[0035] refer to Figure 4 , forming a metal layer 130 on the metal oxide layer 110 , an...

no. 2 example

[0045] Compared with the first embodiment, the second embodiment differs in that after forming the metal oxide layer 110 and before forming the trench 120 , it further includes: forming an insulating layer 140 on the metal oxide layer 110 .

[0046] Figure 7 to Figure 11 It is a schematic structural diagram corresponding to each step of forming a semiconductor device according to the second embodiment of the present invention. refer to Figure 7 , providing a substrate 100 , forming a metal oxide layer 110 on the substrate 100 ; and forming an insulating layer 140 on the metal oxide layer 110 .

[0047] In this embodiment, the method for forming the metal oxide layer 110 may be chemical vapor deposition. The material of the metal oxide layer may be zinc oxide or aluminum oxide.

[0048]In this embodiment, the method for forming the insulating layer 140 may be chemical vapor deposition, and the material of the insulating layer 140 may be silicon oxide or silicon oxynitride....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More