Substrate etching method and corresponding processing device

A technology for processing devices and substrates, which is applied in the manufacture of discharge tubes, electrical components, semiconductors/solid-state devices, etc., can solve the problems of cost reduction, distortion, and high cost, and achieve a good effect of chemical bombardment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The present invention will be further elaborated below by describing a preferred specific embodiment in detail in conjunction with the accompanying drawings.

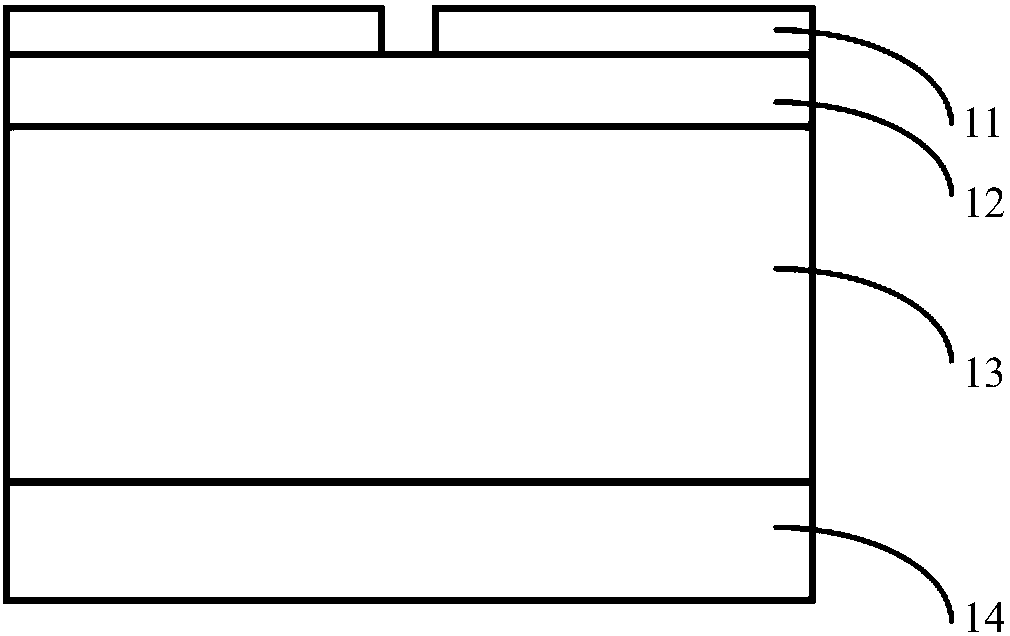

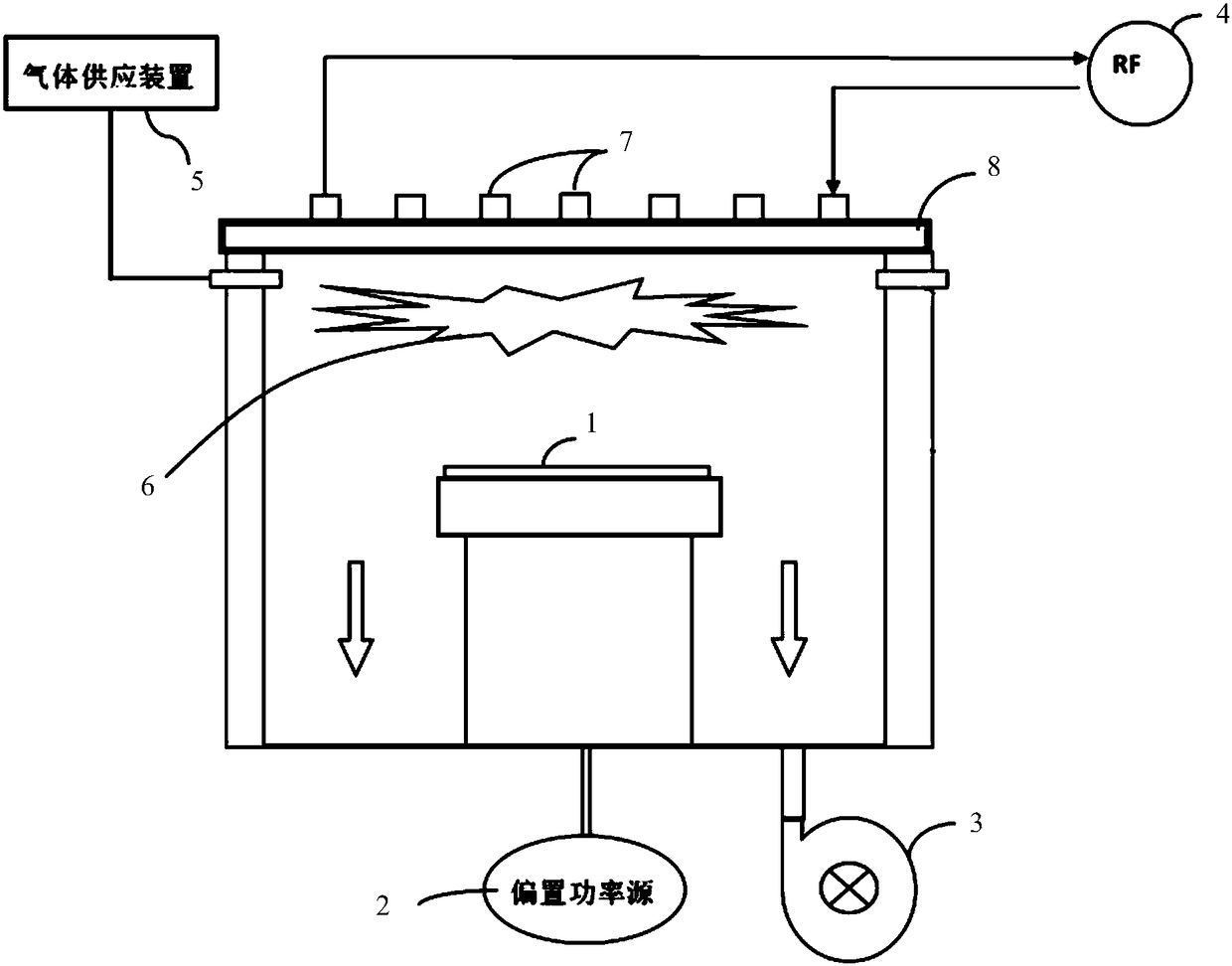

[0041] The invention discloses a method for etching a substrate. The structure of the substrate 1 etched by the etching method is as follows: figure 2 As shown, it includes a photoresist mask layer 11 , a dielectric antireflection layer 12 , a carbon hard mask layer 13 and a silicon oxide layer 14 . The etching method is carried out in a plasma processing device, and the plasma processing device is an inductively coupled plasma processing device or a capacitively coupled plasma processing device. For ease of description, image 3 An inductively coupled plasma reaction device is shown, including a vacuum reaction chamber, the vacuum reaction chamber includes a substantially cylindrical side wall made of metal material, an insulating window 8 is arranged above the side wall of the reaction chamber, and above the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More