FPGA based Displayport signal generating device and method

A signal generation and signal protocol technology, applied in static indicators, instruments, etc., can solve problems such as the inability to meet the special rate and custom rate of low-power devices, the inability to support 3840x216060Hz ultra-high resolution, and the increase in manufacturing costs. Improve test efficiency and test reliability, improve production efficiency and product qualification rate, and the effect of high integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In the following description, numerous specific details are given in order to provide a more thorough understanding of the present invention. It will be apparent, however, to one skilled in the art that the present invention may be practiced without one or more of these details. In other examples, some technical features known in the art are not described in order to avoid confusion with the present invention.

[0030] In order to thoroughly understand the present invention, detailed steps and detailed structures will be provided in the following description, so as to illustrate the technical solution of the present invention. Preferred embodiments of the present invention are described in detail below, however, the present invention may have other embodiments besides these detailed descriptions.

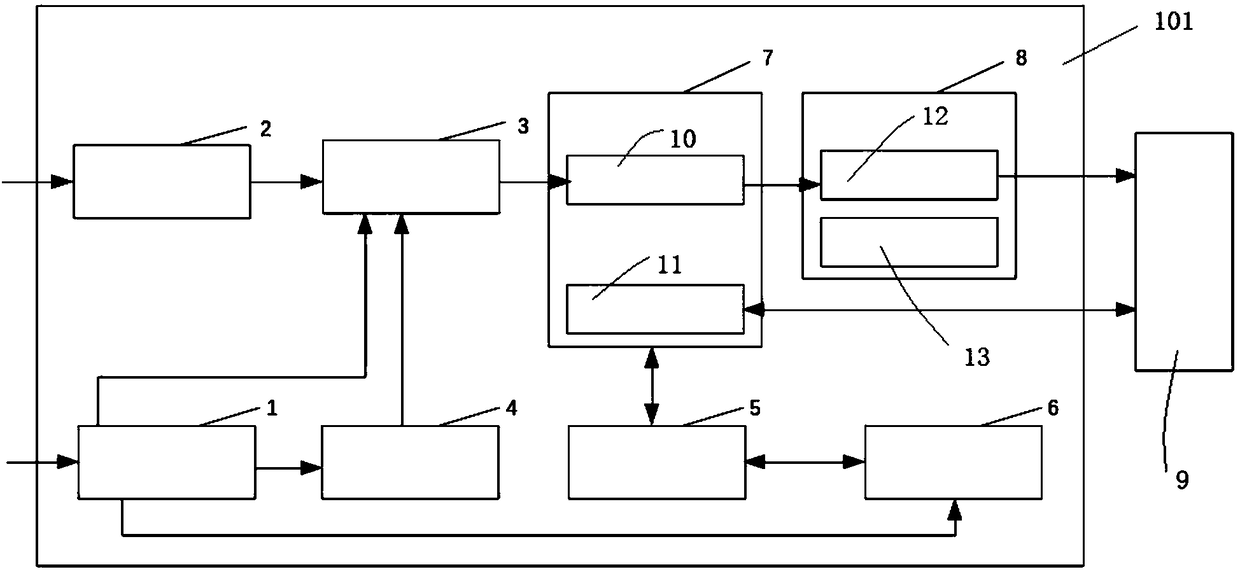

[0031] refer to figure 1 As shown, an FPGA-based Displayport signal generating device of the present invention includes an AXI Lite parallel image parameter receiving module ...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap