Patents

Literature

126 results about "Soft core processor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Control system and control method of satellite-borne microwave radiometer

InactiveCN101876699AHigh speedImprove reliabilityWave based measurement systemsControl systemData acquisition

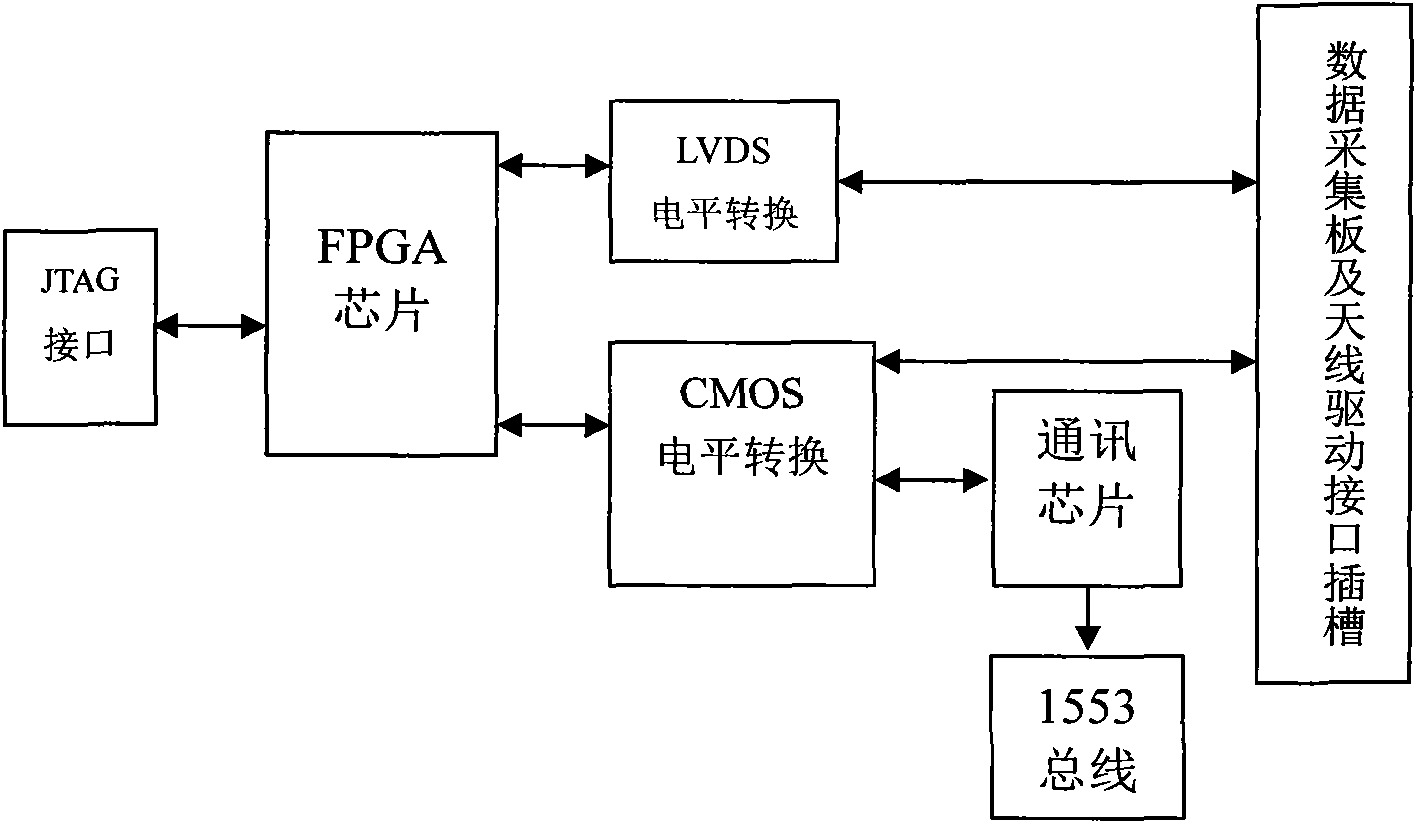

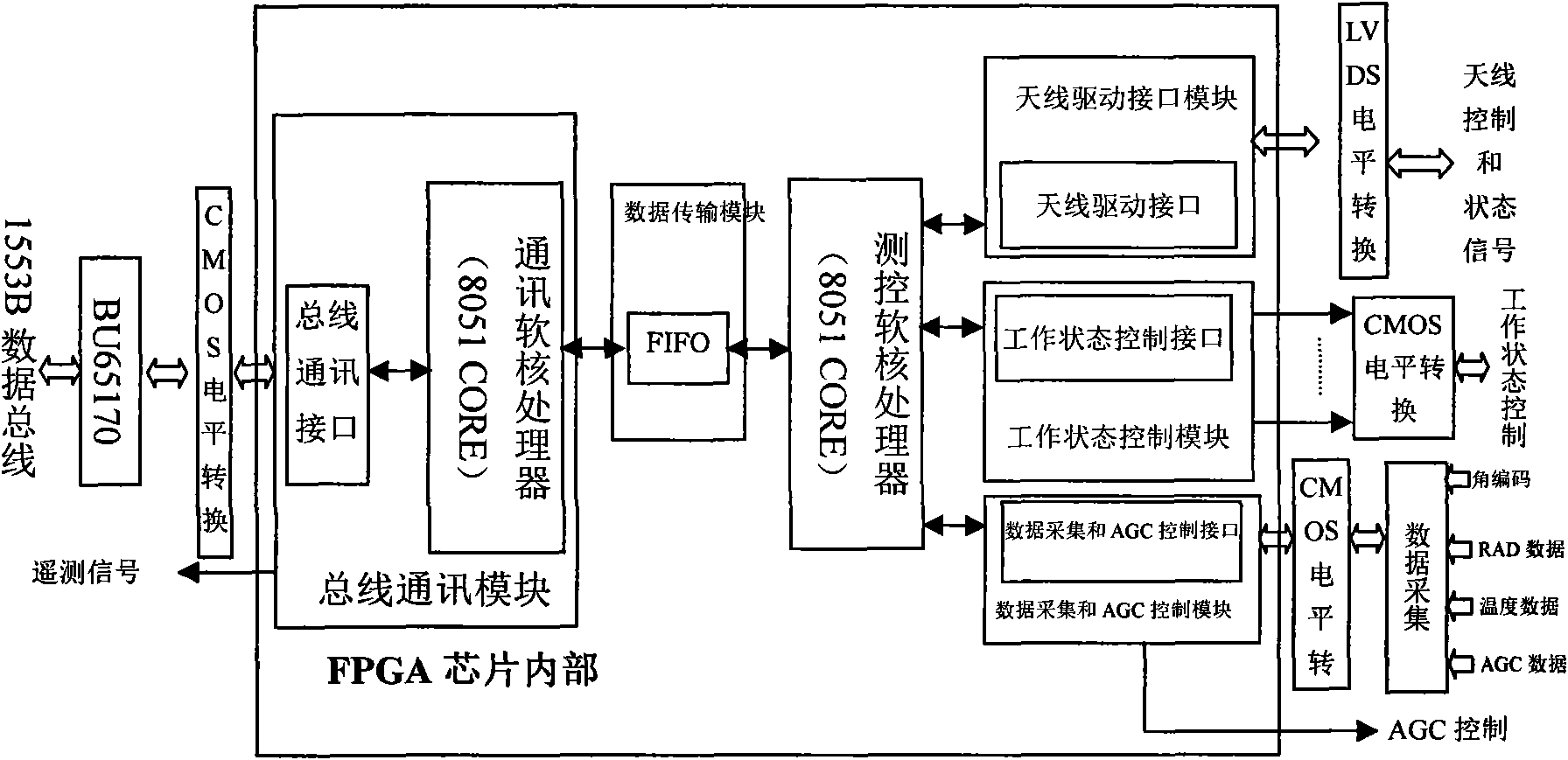

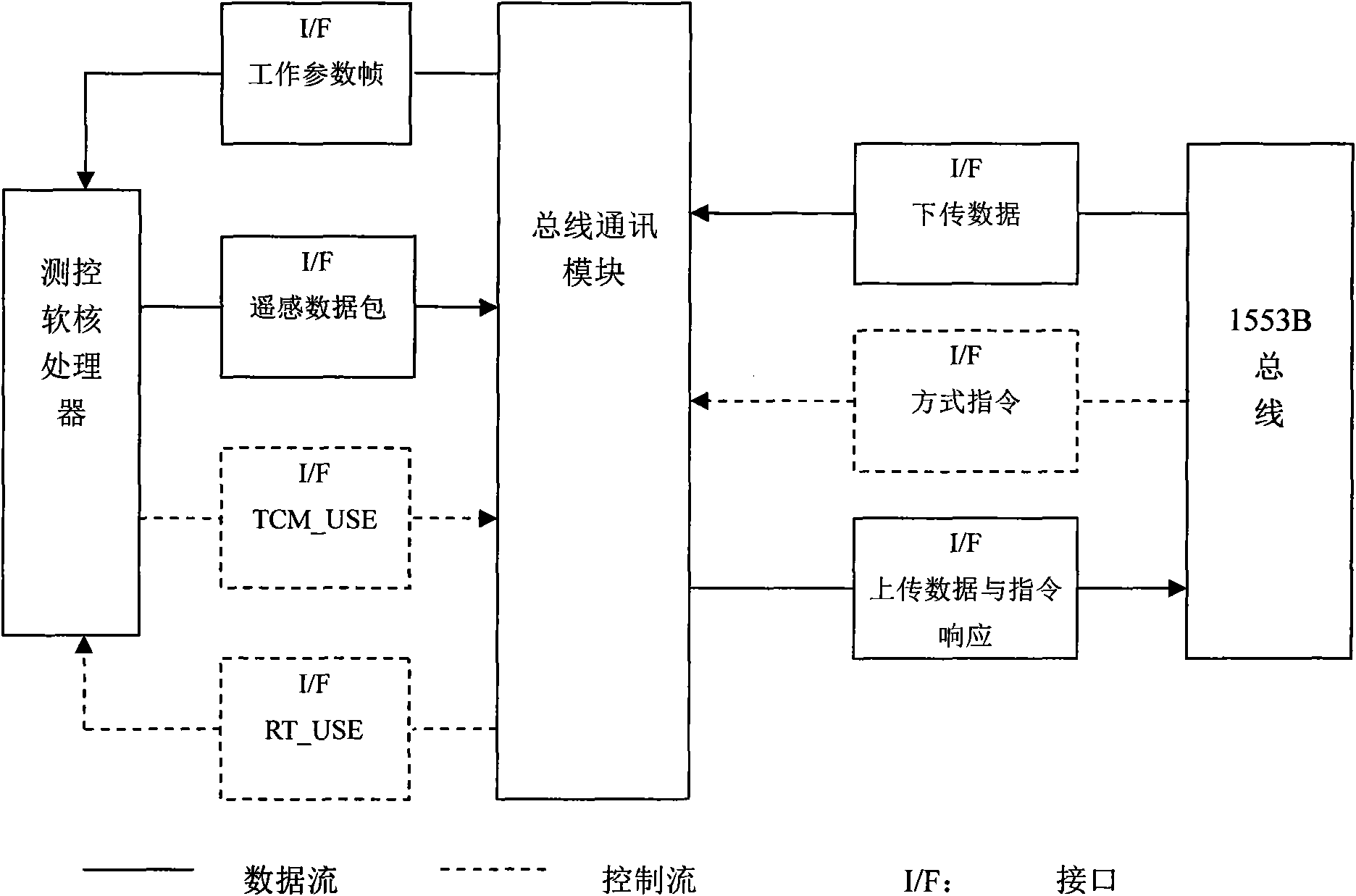

The invention provides a control system and a control method of an FPGA soft-core processor technique-based satellite-borne microwave radiometer. The control system comprises an FPGA chip, a communication chip, a level switching circuit, a data acquisition board interface and an antenna driving interface slot, wherein the FPGA chip is matched with the communication chip, the level switching circuit and a data acquisition board to realize the system control of the satellite-borne microwave radiometer and finish the system functions, such as data acquisition, remote measurement, RAD control, antenna control and bus communication, of the microwave radiometer. The control system adopts the FPGA chip to realize a control circuit of the satellite-borne microwave radiometer and increase the integration of the control circuit, and the formed system has a small volume and low power consumption, is suitable for data processing with a higher speed requirement, and has high reliability. Besides, because the programmability of an FPGA is high, only a program inside the FPGA is changed to ensure that the FPGA can be suitable for the control system of the microwave radiometer with different requirements.

Owner:CENT FOR SPACE SCI & APPLIED RES

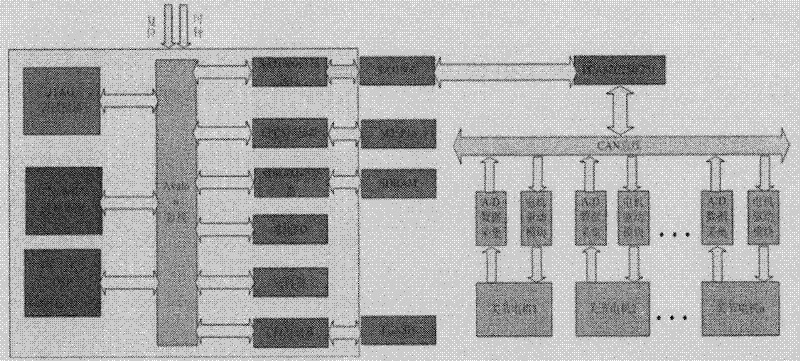

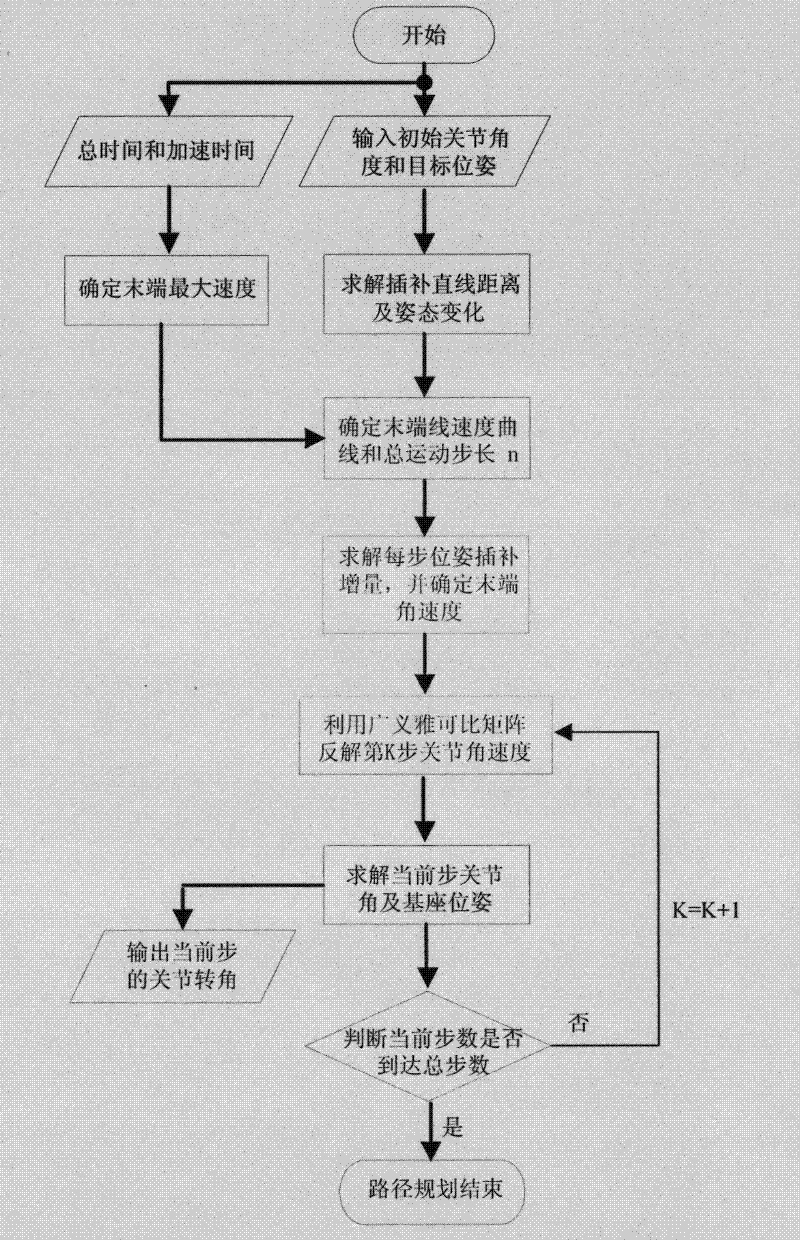

Embedded multinuclear main controller of modular robot based on FPGA (Field Programmable Gata Array)

InactiveCN102393656AReduce volumeReduce energy consumptionProgramme control in sequence/logic controllersDigital signal processingJoint Test Action Group

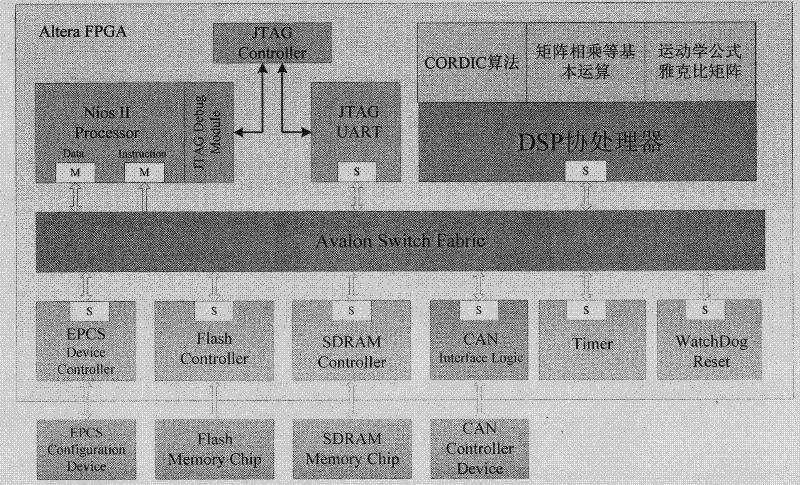

The invention discloses an embedded multinuclear main controller based on an FPGA (Field Programmable Gata Array) chip in the technical field of robot control. The main controller integrates two main modules, namely a Nios II soft core processor and a DSP (Digital Signal Processing) coprocessor, wherein the Nios II soft core processor communicates with a system clock module, a watchdog and resetting system module, a JTAG interface module, a CAN serial bus control module and a memorizer control module by an Avalon bus module; as a hardware computing core, the DSP coprocessor communicates with a Nios II soft core by the Avalon bus module; and the Nios II soft core is responsible for the movement planning of a robot and the communication of each controller at each joint, and the coprocessor is responsible for kinetic resolving. The embedded multinuclear main controller adopts the Nios II soft core as a communication core and the coprocessor as a computing core to realize the rapid and stable control and reduce energy consumption and the volume.

Owner:BEIJING UNIV OF POSTS & TELECOMM

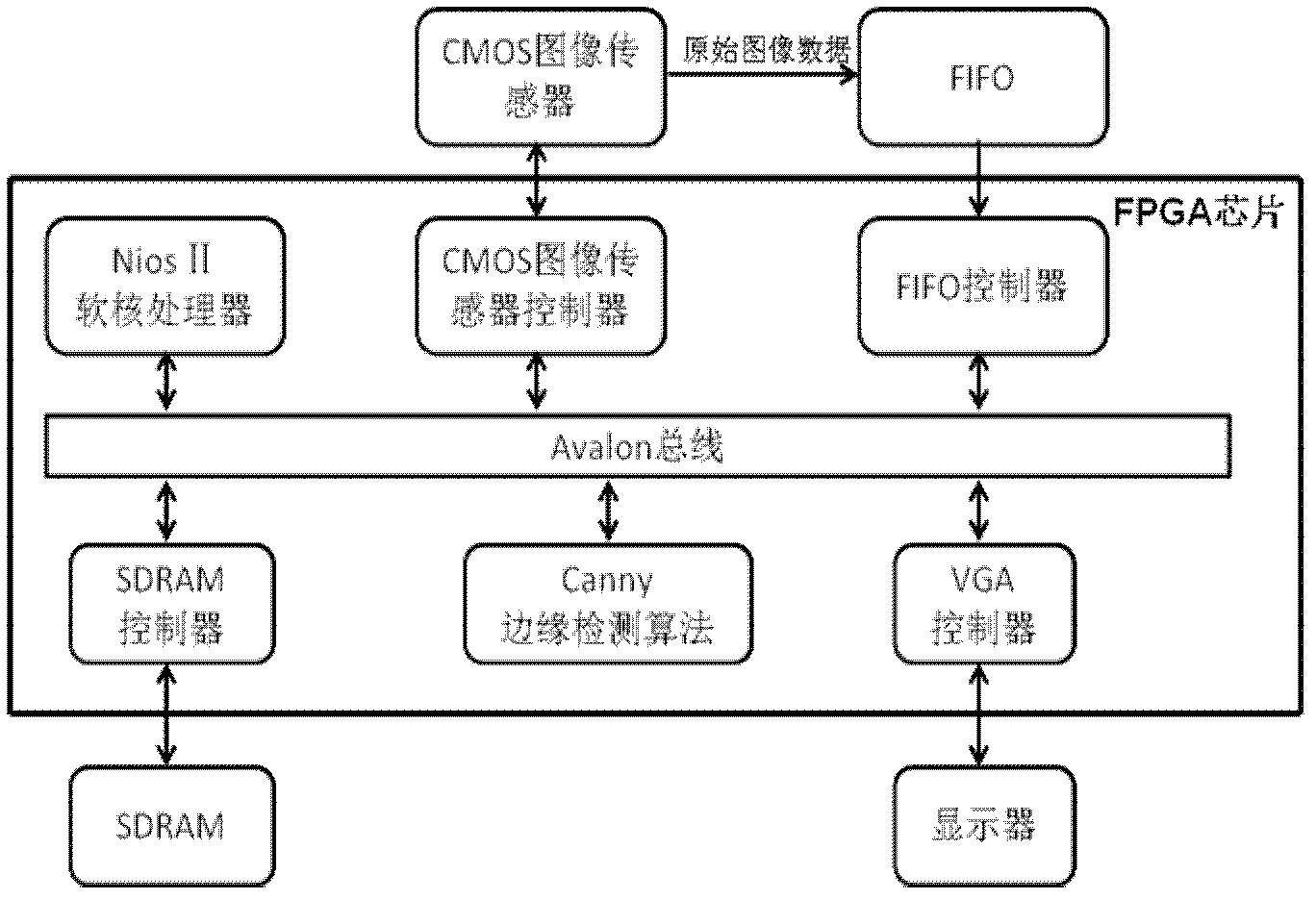

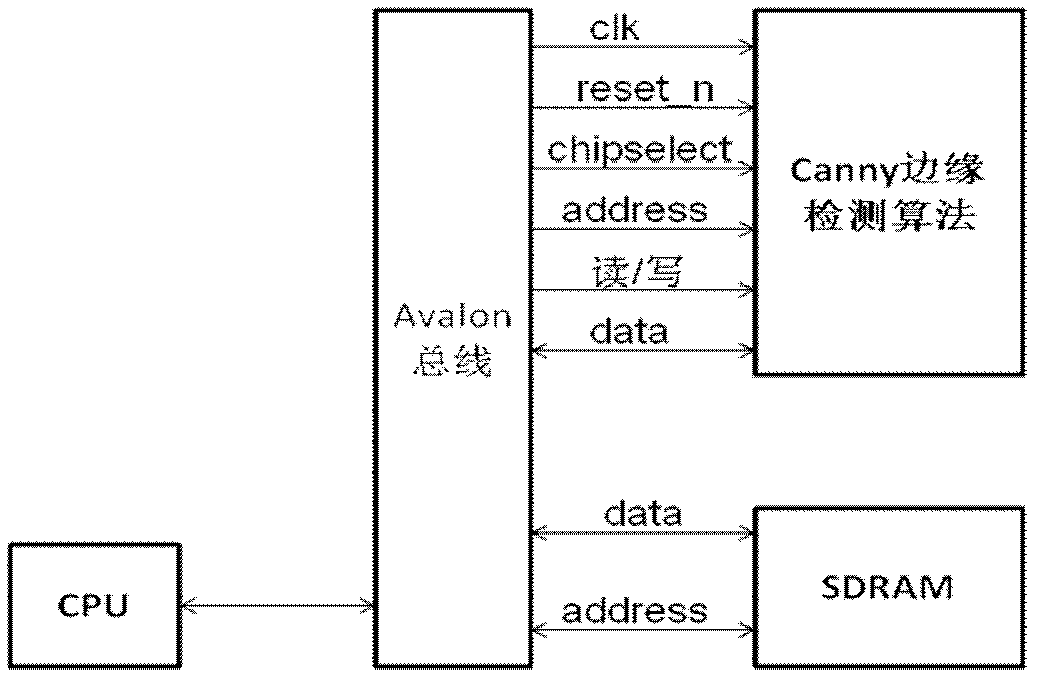

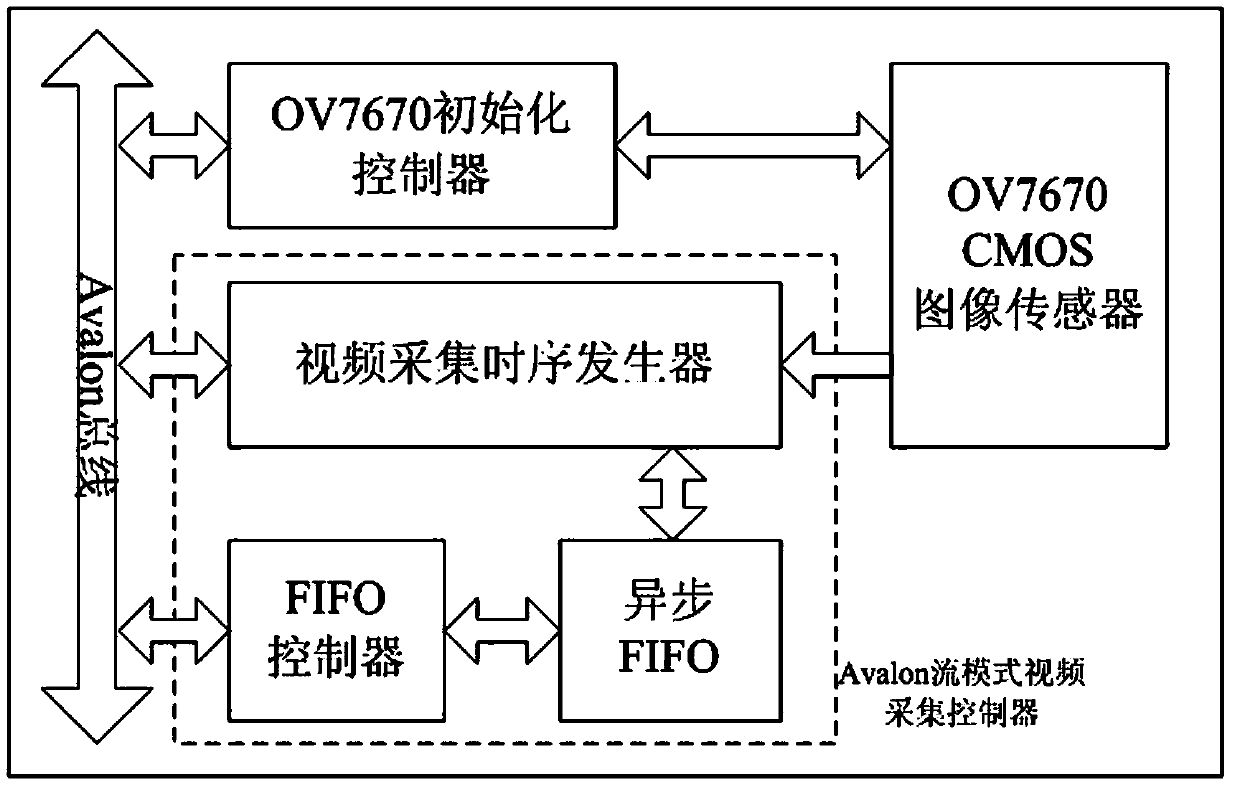

Image acquiring and processing method based on FPGA (field programmable gate array) serving as control core

InactiveCN102663758AImprove signal-to-noise ratioImprove detection accuracyImage analysisCMOSGraphics

The invention belongs to the field of image acquiring and processing, and particularly relates to an image acquiring and processing method based on an FPGA (field programmable gate array) serving as a control core. The method mainly includes building an image acquiring and processing SOPC (system on programmable chip) system comprising a Nios II soft-core processor module, a CMOS (complementary metal-oxide-semiconductor transistor) image sensing controller module, an FIFO (first in first out) controller module, an SDRAM (synchronous dynamic random access memory) controller module, a Canny edge detection algorithm module and a VGA (video graphic array) controller module. Firstly, images are acquired and then cached in the FIFO controller module; secondly, image data in the FIFO controller module are transmitted to an off-chip SDRAM chip by FPGA software and are stored in the off-chip SDRAM chip; thirdly, images in a memory are processed by means of an image processing algorithm, 'ping pong operation' is realized during processing, and the processing images are stored in the SDRAM again; and finally, the acquired edge images are displayed through a VGA interface after being processed.

Owner:BEIJING UNIV OF TECH

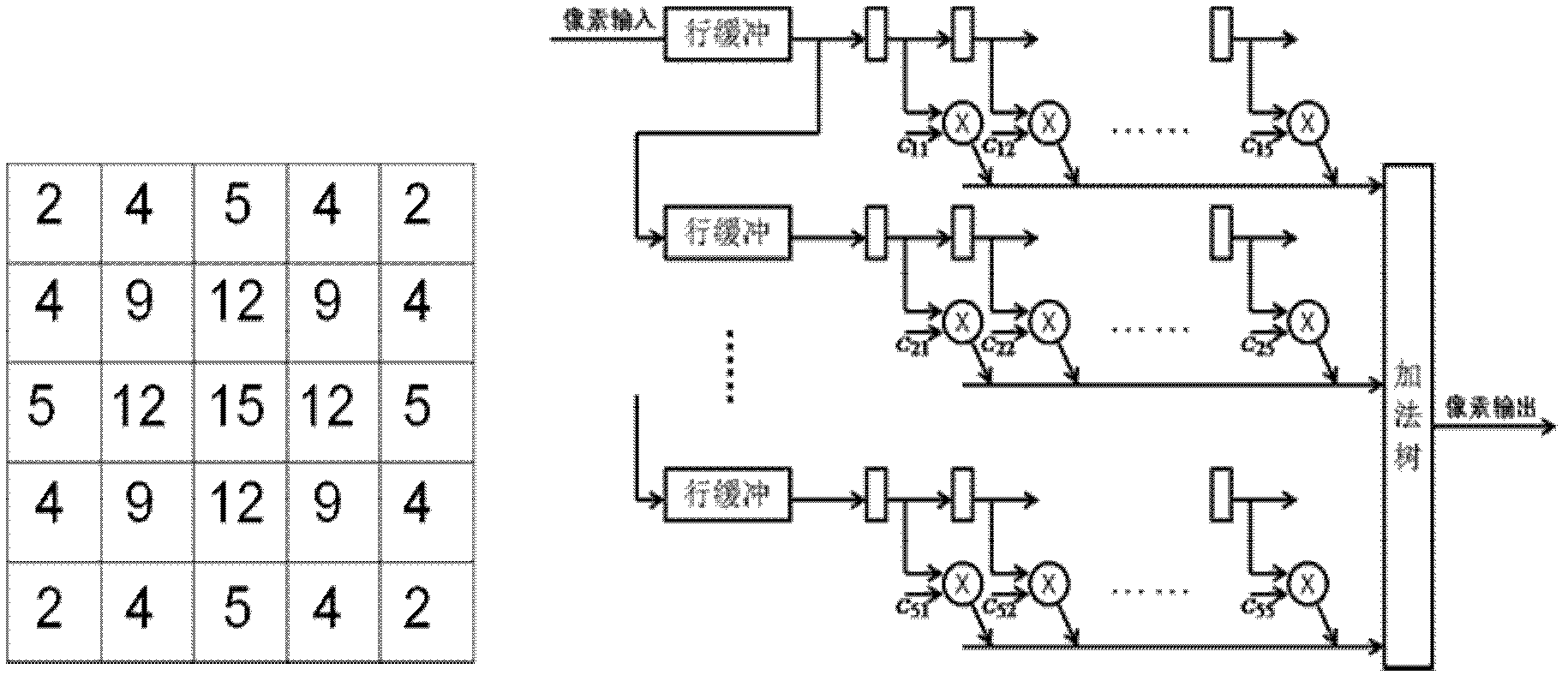

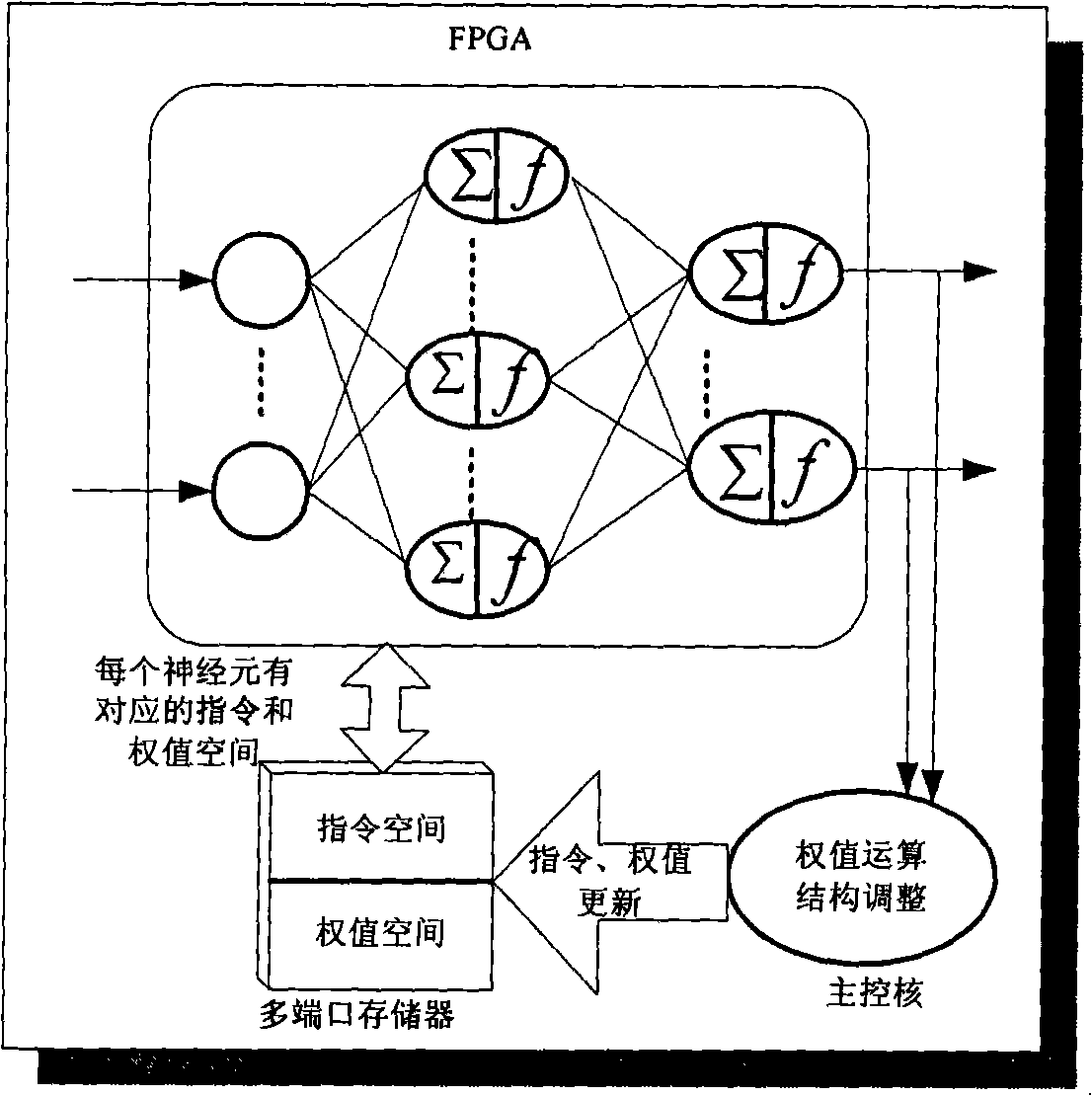

Feedforward neural network hardware realization method based on multicore technology

The invention discloses a feedforward neural network hardware realization method based on multicore technology, relating to a computer system based on a specific calculation model. The invention adopts an NIOS II soft core processor and utilizes Quartus II software in an FPGA development system thereof to build a multicore processor system, the number of processor cores is only limited by chip scale, each processor core can be independently programmed, and multiple processor cores can simultaneously run respective program and simulate the characteristics of nerve cells of any kind by performing programming of one single core; in the network studying process, the single cores calculate output amount in a parallel mode and finish the adjustment of corresponding weights and thresholds; the input and output of each single core are performed with data exchange via a multiport memory to stimulate feedforward neural network with any structure, which realizes the purposes of high speed, distribution and parallel calculation of the neural network.

Owner:王连明

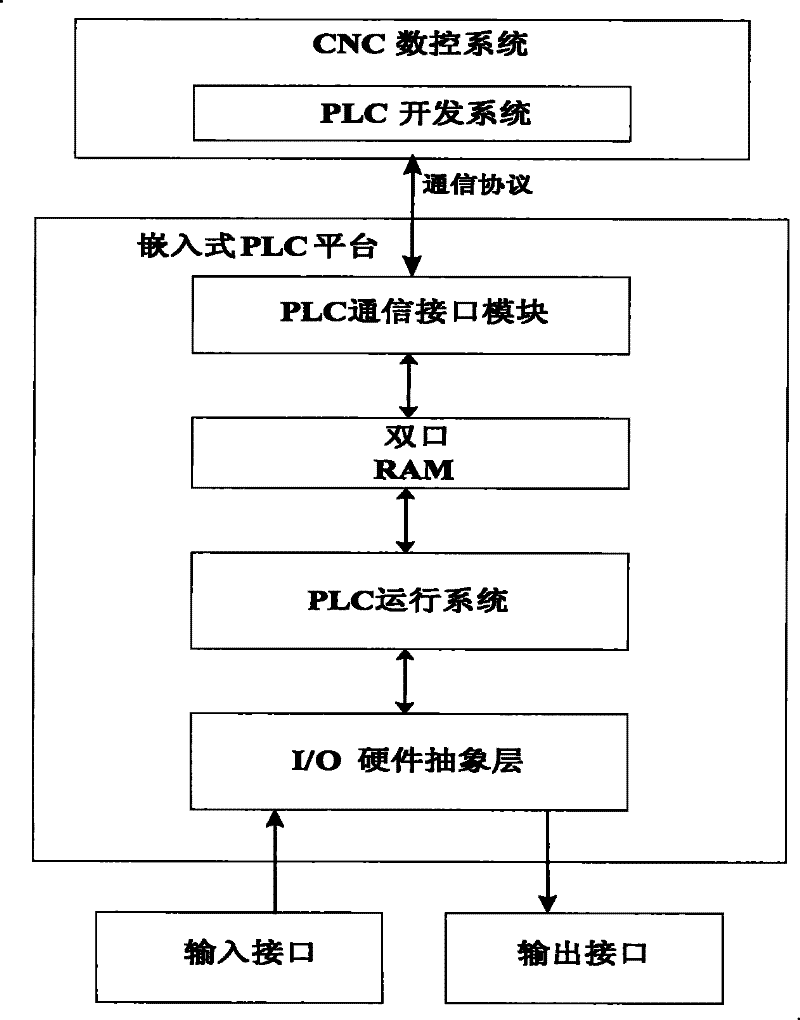

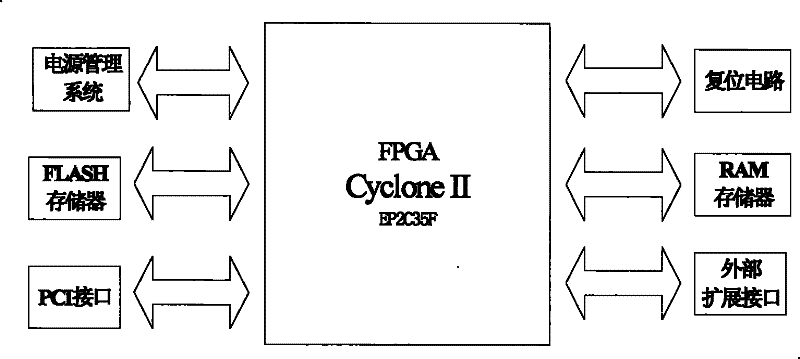

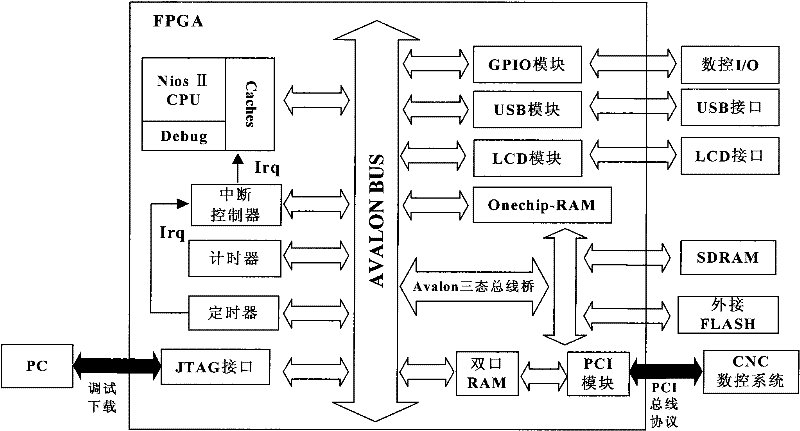

Numerical control system logic controller on basis of system on programmable chip and implementing method thereof

InactiveCN102331733AHighly integratedImprove reliabilityProgramme control in sequence/logic controllersProgrammable logic deviceProgrammable logic controller

The invention relates to an implementing method of a numerical control system programmable logic controller (PLC) on the basis of a system on a programmable chip, which comprises the following steps of: constructing an external circuit connected with an FPGA (Field Programmable Gate Array); constructing the system on the programmable chip on the FPGA, wherein the system on the programmable chip is used for operating the numerical control system PLC; clipping, transplanting and compiling a real-time operation system in the system on the programmable chip; and operating the PLC on the real-time operation system to realize control on peripherals. In the invention, due to the adoption of the design of the system on the programmable chip on the basis of the FPGA, the integration level and the reliability of a programmable logic device are improved; and due to the adoption of a technology on the basis of the SOPC (System On Programmable Chip), a soft core processor is internally realized for executing a PLC task, the processing speed of the PLC is improved, and the cost is reduced when the flexibility is ensured.

Owner:中国科学院沈阳计算技术研究所有限公司 +1

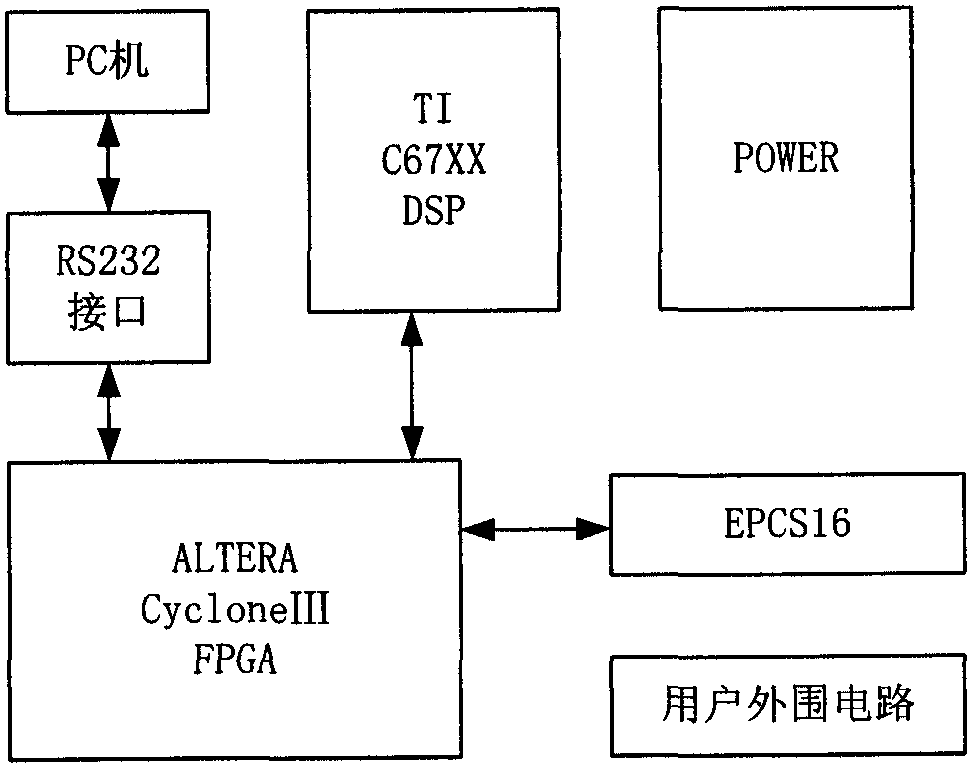

Program updating method for FPGA (Field Programmable Gate Array)/DSP (Digital Signal Processor) embedded system

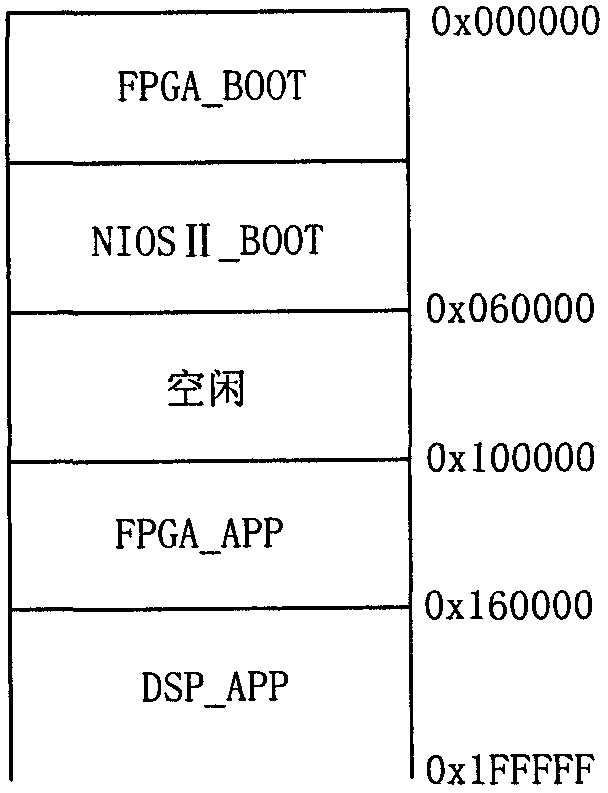

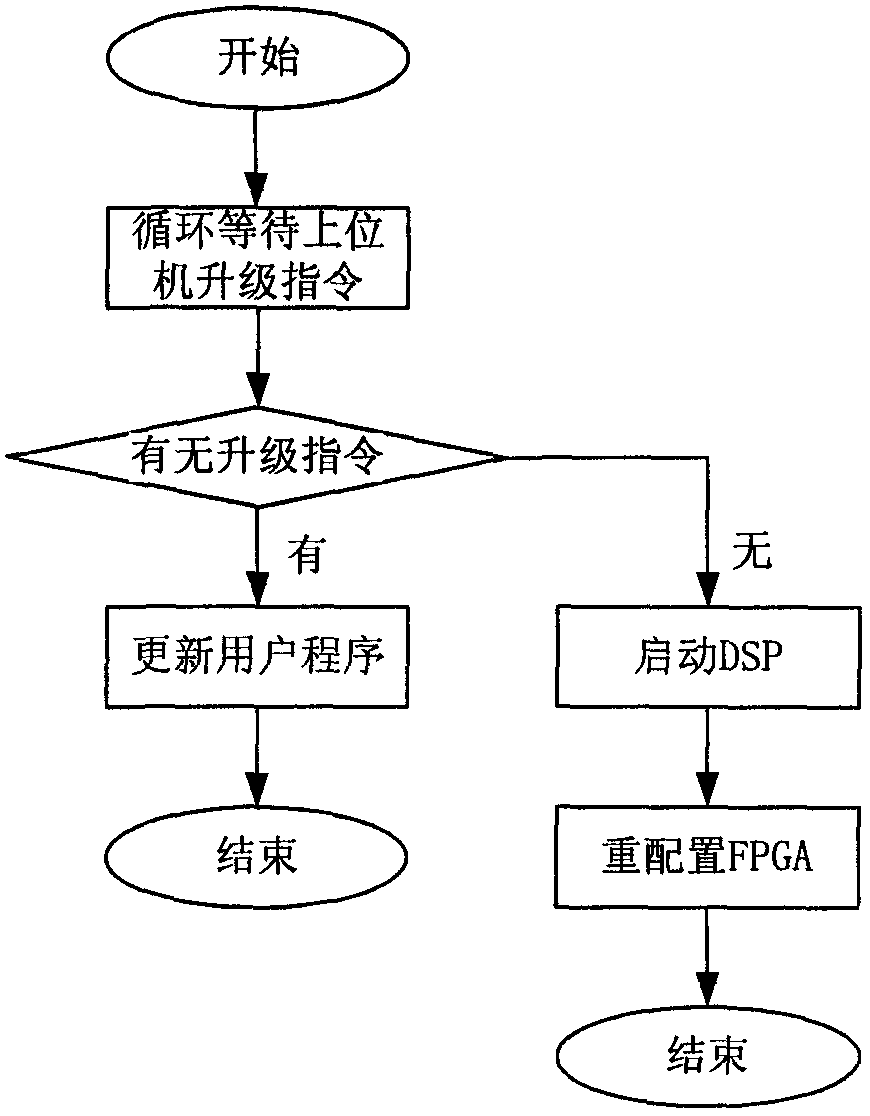

ActiveCN103019779AOvercome limitationsReduce volumeProgram loading/initiatingControl systemStructure of Management Information

A program updating method for an FPGA (Field Programmable Gate Array) / DSP (Digital Signal Processor) embedded system, based on a special active serial figuration chip EPCS (Electronic Propulsion Control System), builds communication with an upper computer through an embedded soft-core processor NIOS (National Institute of Open Schooling) II so as to control and finish updating of FPGA hardware figuration data and DSP application program data of users. Compared with the traditional embedded system with an FPGA / DSP+FLASH structure, the method reduces the board level PCB wiring complexity and the system volume, and satisfies requirements for updating the FPGA hardware figuration data and the DSP application program data when a JTAG (Joint Test Action Group) interface is invisible after this kind of products are assembled.

Owner:BEIJING RES INST OF TELEMETRY +1

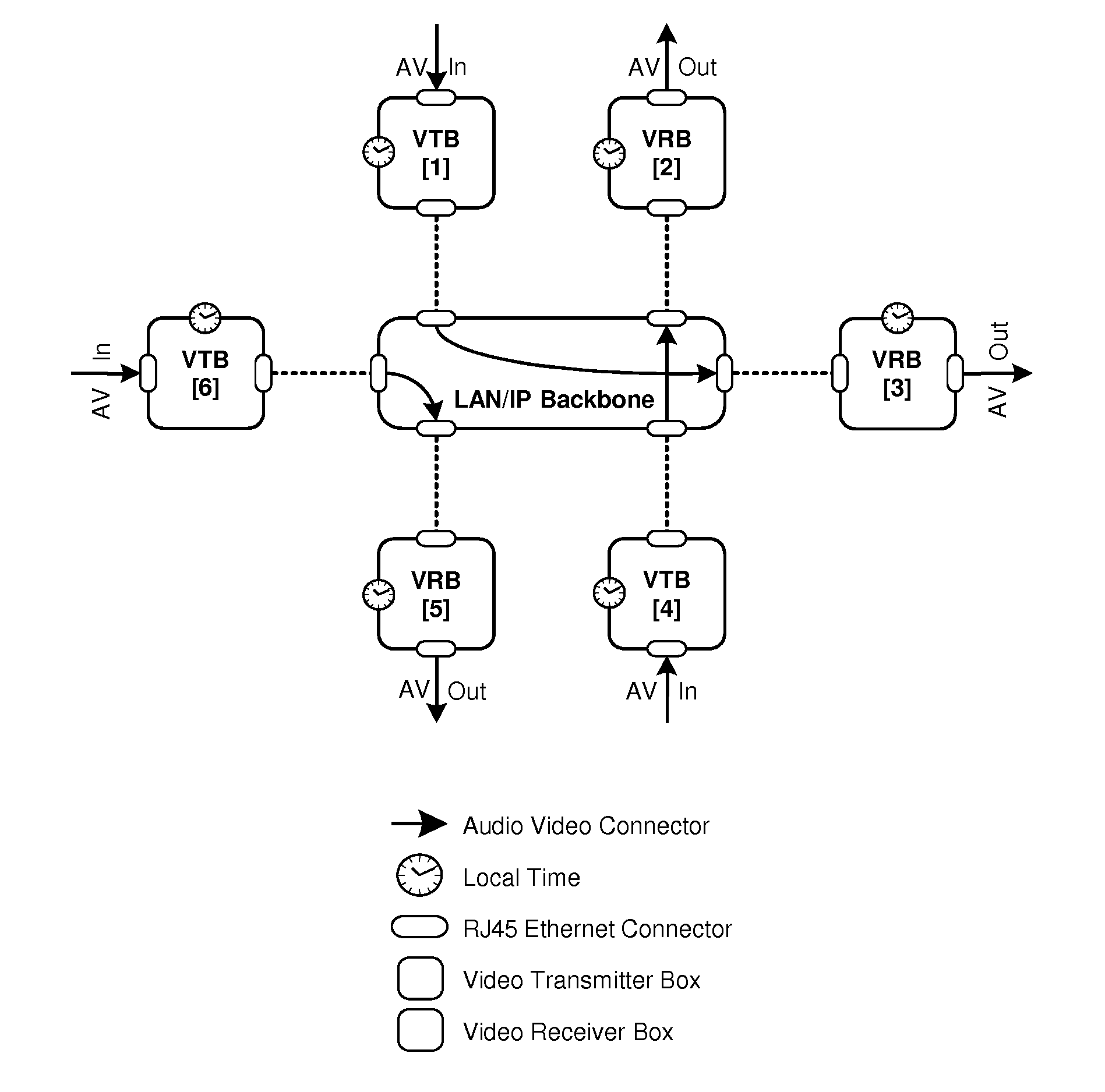

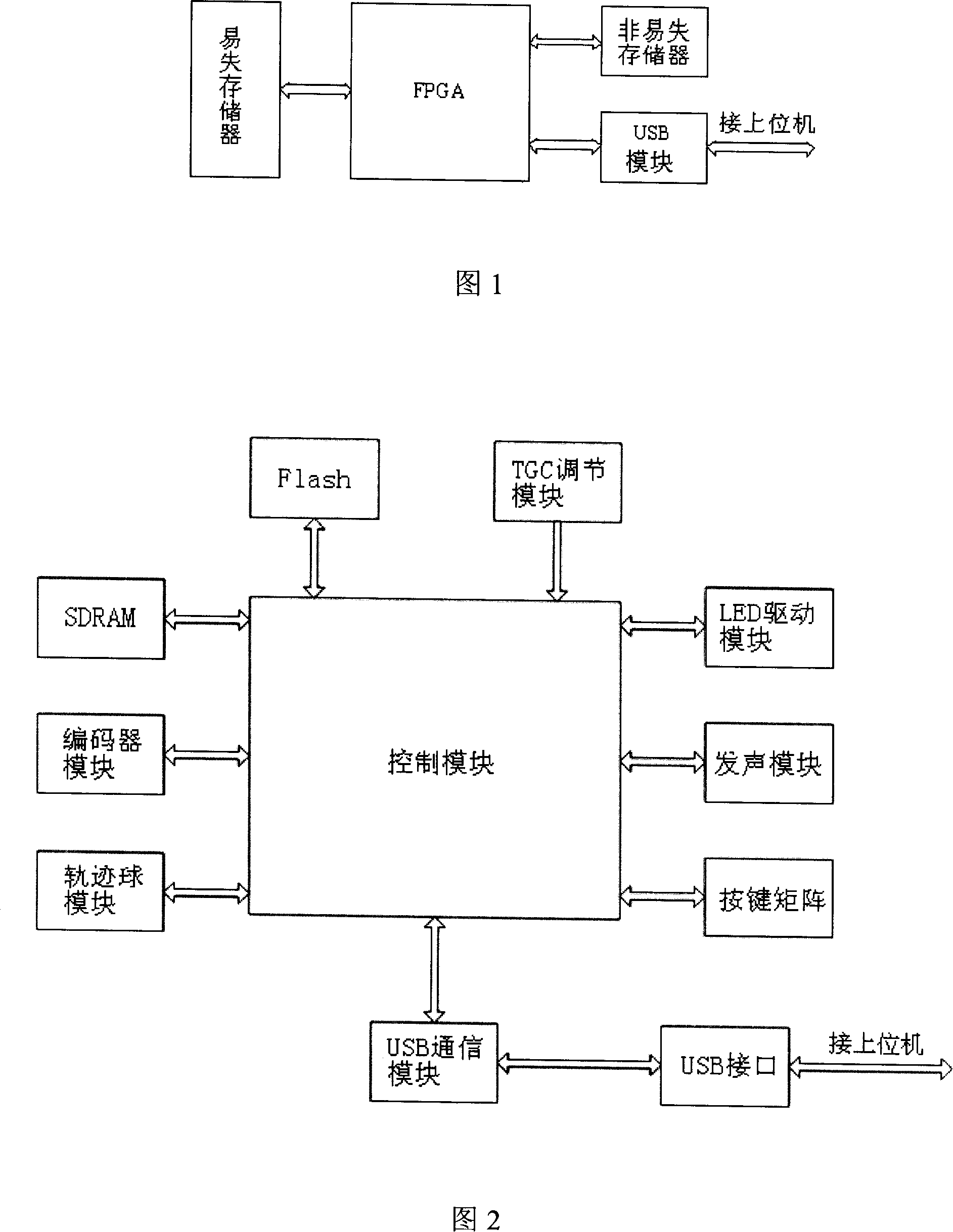

USB interface control panel on-line update method

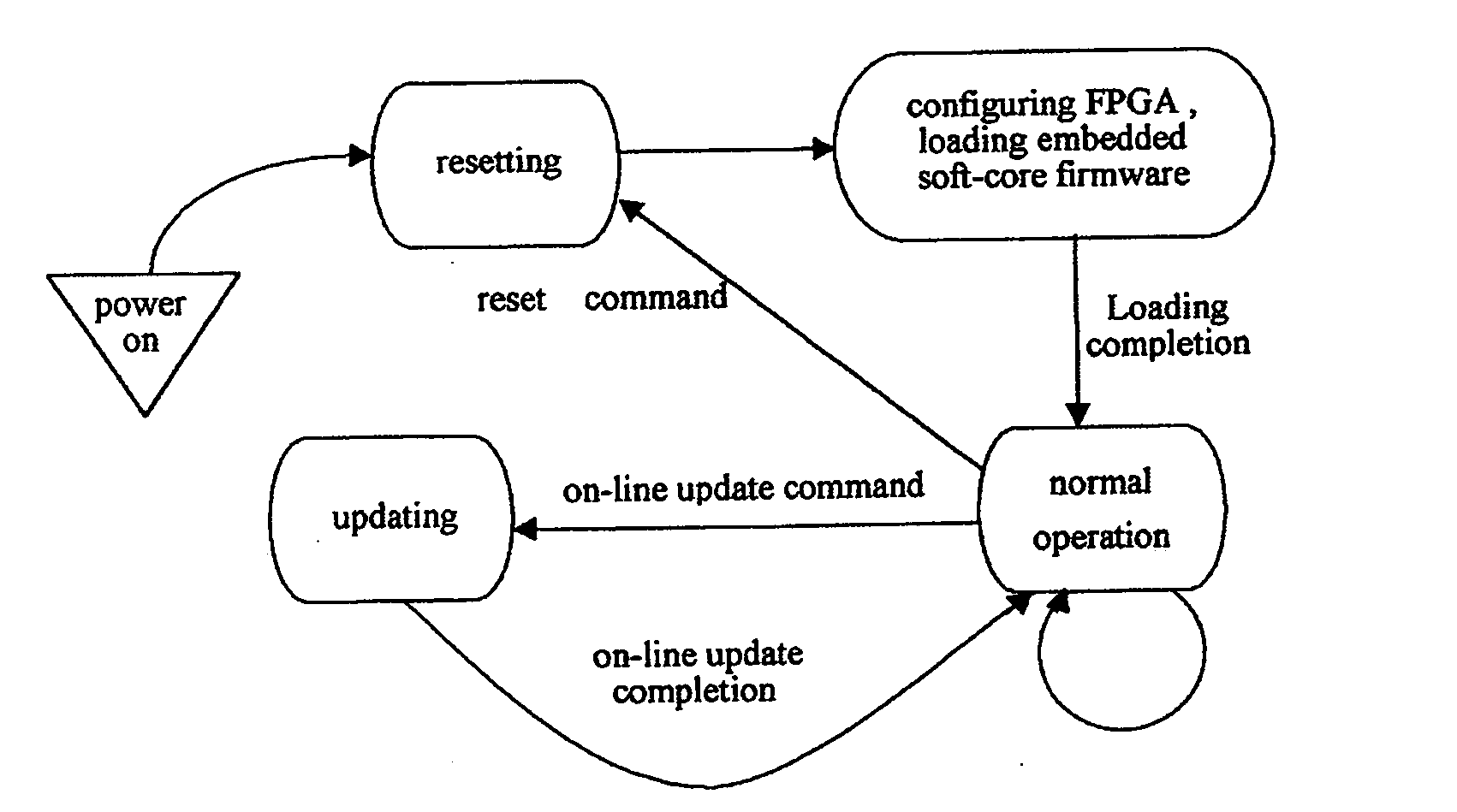

InactiveUS20080052700A1Improve abilitiesSpecific program execution arrangementsMemory systemsUSBData storing

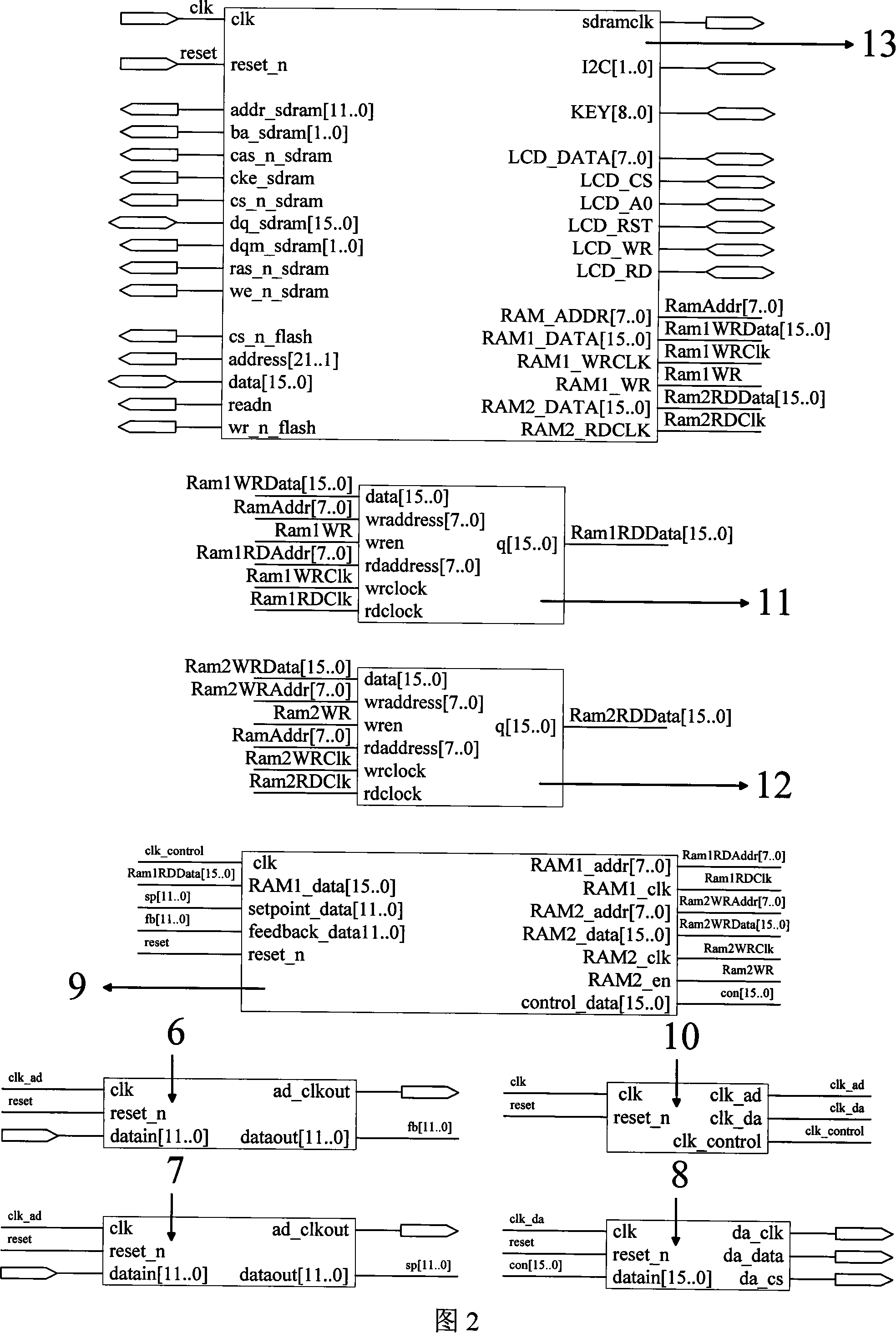

The present invention relates to a USB interface control panel on-line update method, comprising steps of: the embedded soft-core processor, after receiving through USB module the on-line update command from the host computer, receiving update data sent from the host computer, and storing the update data into the volatile memory of the embedded soft-core processor; erasing the original embedded soft-core processor firmwares and / or FPGA configuration files stored in the non-volatile memory; writing the update data stored in the volatile memory into the non-volatile memory by means of programming. The present invention uses USB interface to realize the on-line updating of the control panel in the medical equipment and the like, wherein the control panel is capable of completely updating the embedded soft-core processor firmwares and / or FPGA hardware configuration files under the control of the host and without bringing interference to the normal operation by users.

Owner:SHENZHEN MINDRAY BIO MEDICAL ELECTRONICS CO LTD

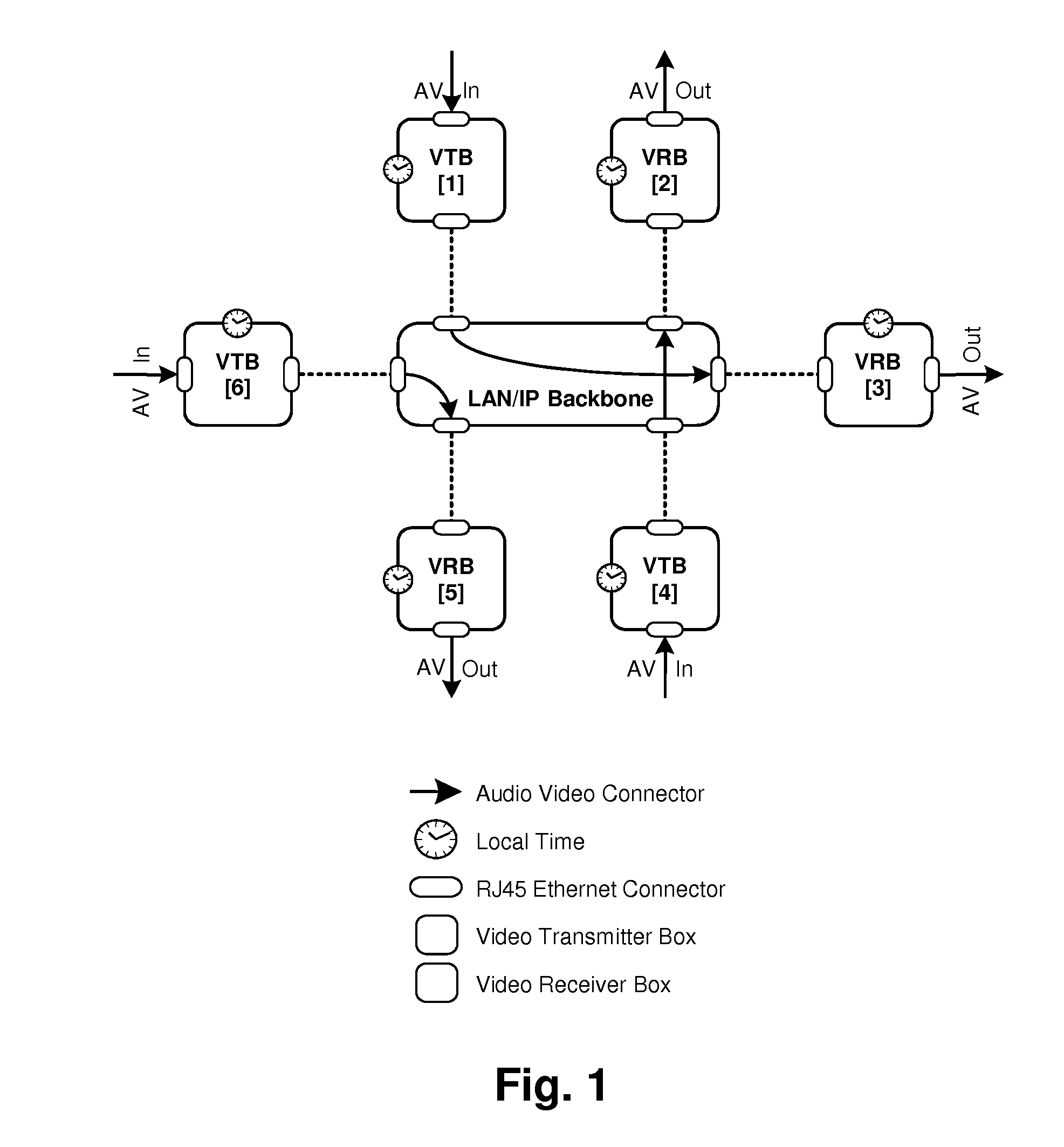

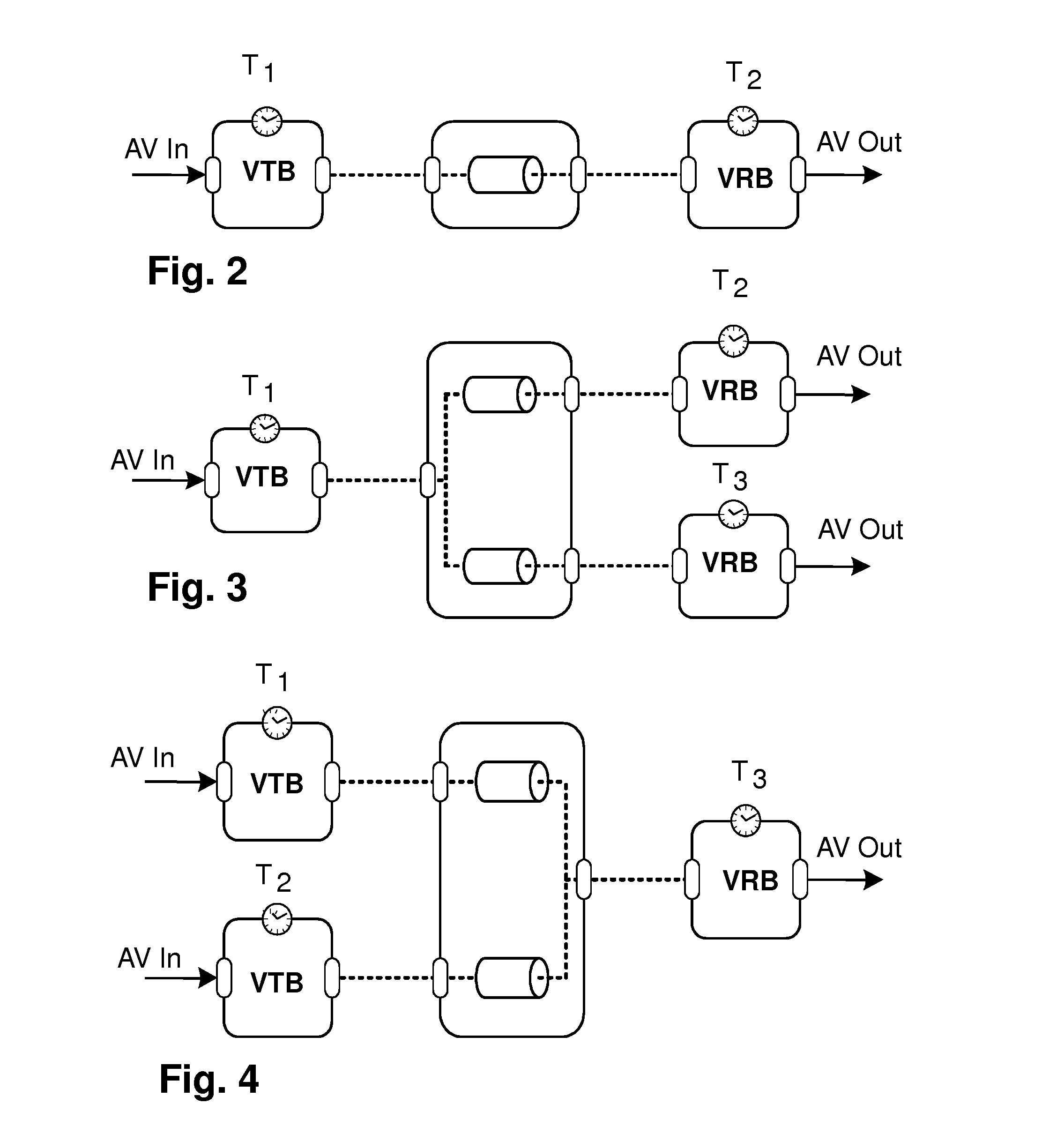

High definition video/audio data over IP networks

InactiveUS20110122877A1Analogue secracy/subscription systemsData switching by path configurationStructure of Management InformationNetwork management

The system transmits High Definition (HD) video / audio data, e.g. a JPEG2000-compressed video stream multi-channel audio stream, over a packet switching network, e.g. an Ethernet or IP network. Both the transmitter unit VTB and the receiver unit VRB feature a modular structure consisting of a base module or baseboard common to both units and one or more exchangeable adapter cards attached to or inserted into the baseboards to perform selected functions. The basebord is unitary, i.e. identical for both the VTB and the VRB; its components are activated depending upon the baseboard being in a VTB or a VRB. Each card is unique and earmarked and serves a specific purpose, e.g. for video coding and decoding, SMPTE processing, clocking / re-clocking, audio embedding / extraction. Upon inserting a card into a baseboard, the earmark is identified and the baseboard configured as transmitter or receiver baseboard. Functions in the baseboard can be implemented in Field Programmable Gate Arrays (FPGAs) and the network management, configuration, and / or control of the transmitting and / or receiving processes be performed by a softcore processors. This inventive combination of modular hardware / software results in a cost-effective, reliable, and fast system for transmitting large data volumes over packet switching networks.

Owner:BAROX KOMMUNIKATION

A full algorithm cryptographic card based on PCI-E interface and an encryption method thereof

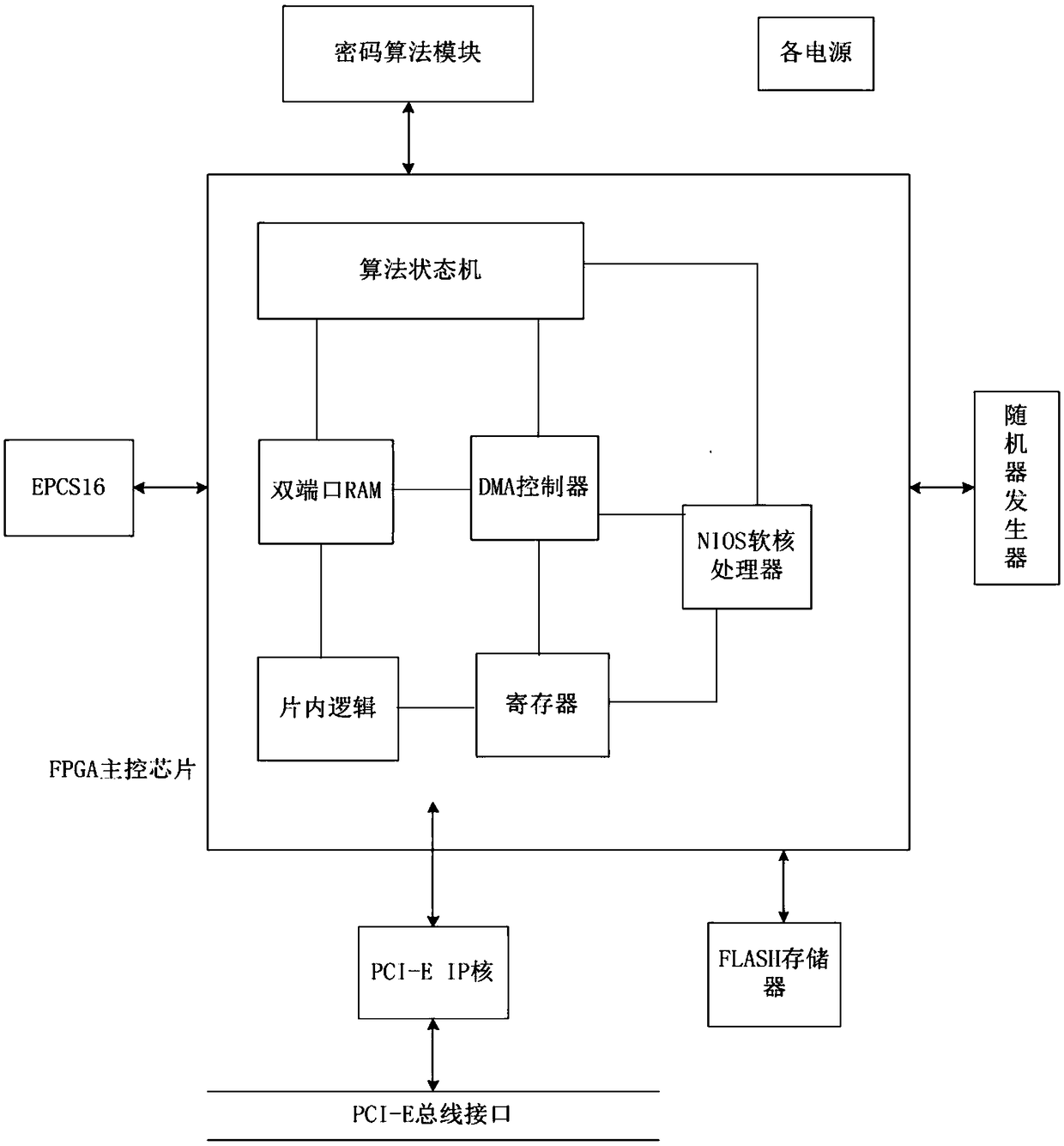

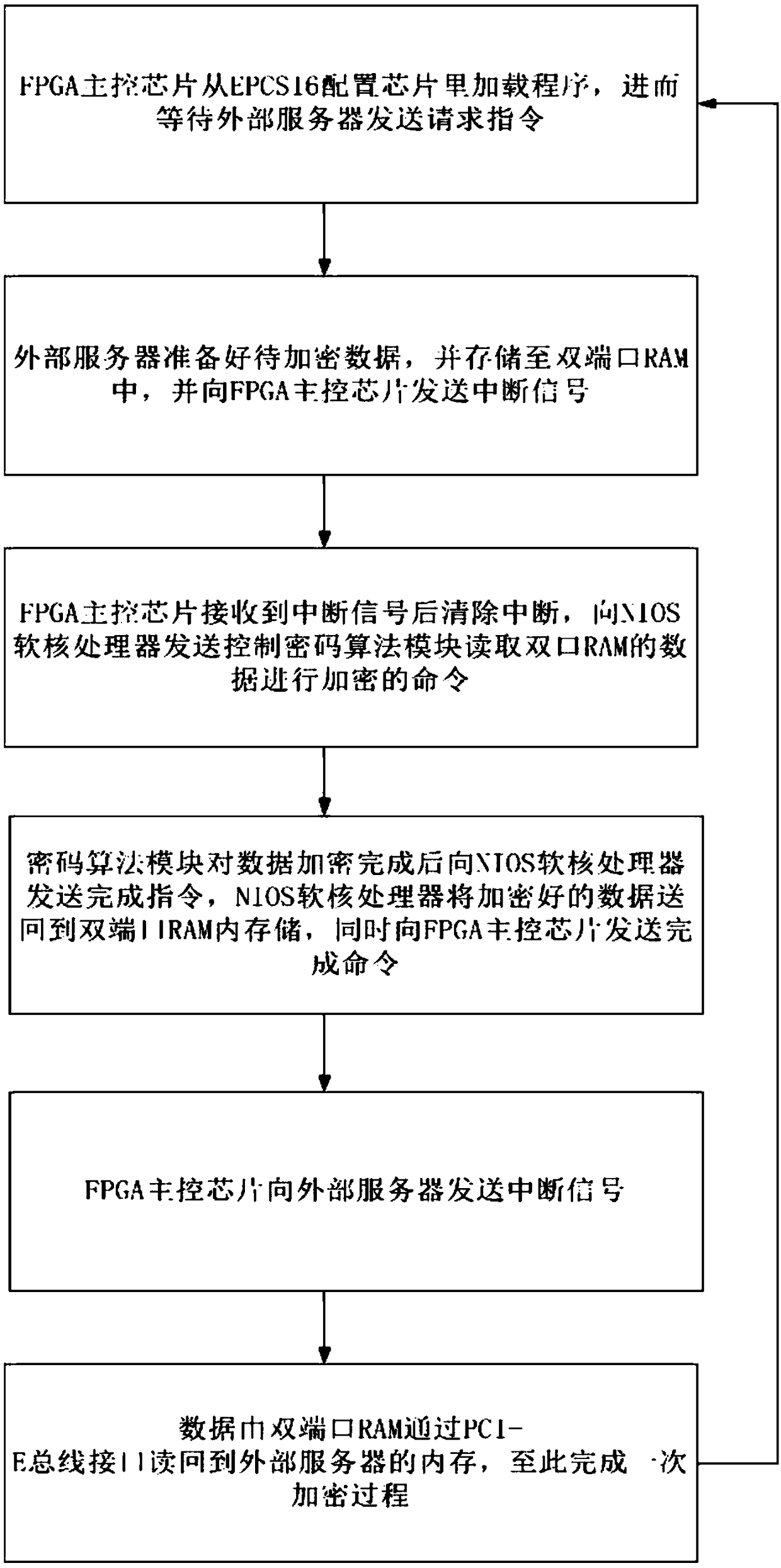

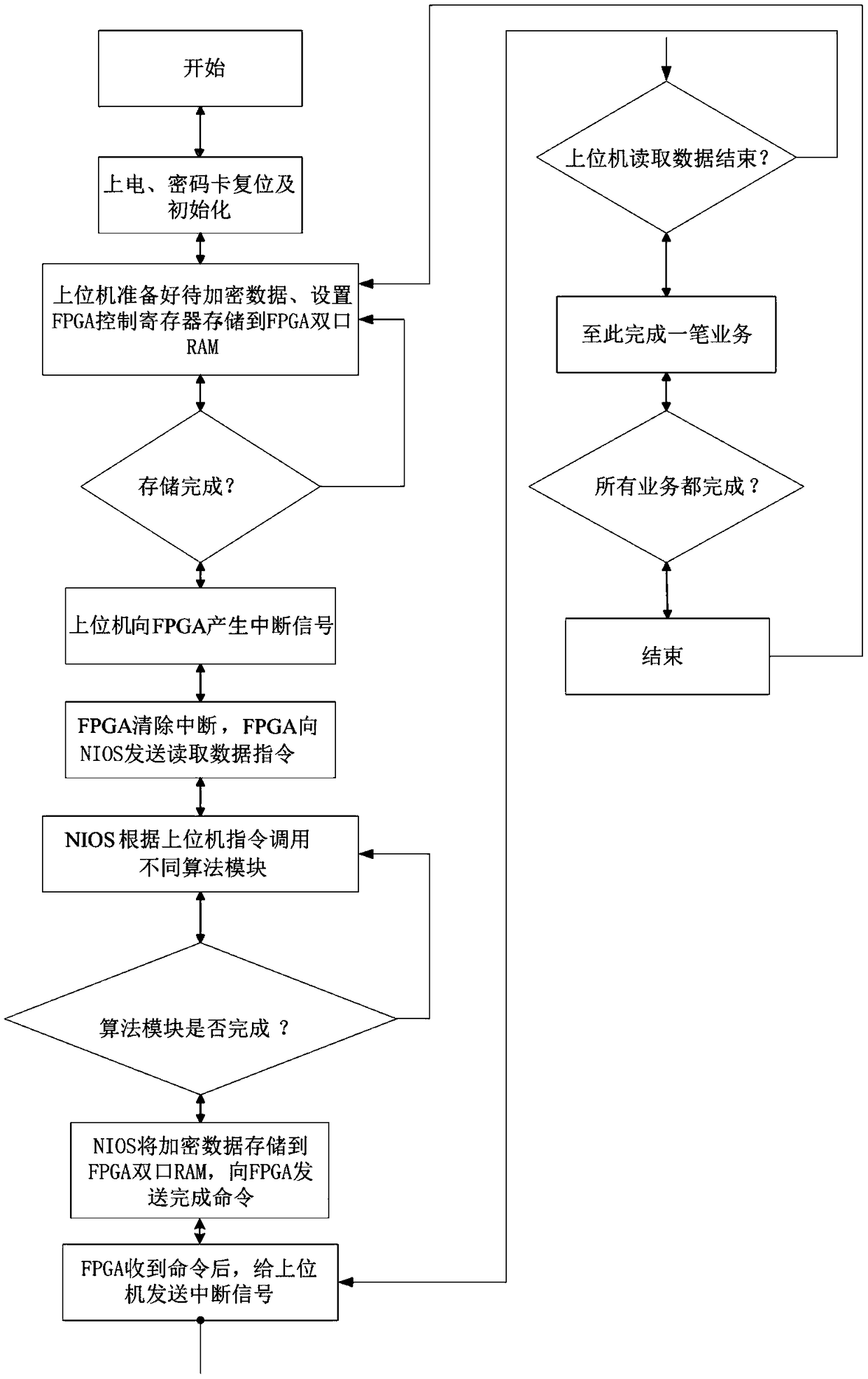

InactiveCN109145568AImprove security strengthImprove securityDigital data authenticationEnergy efficient computingAlgorithmic State MachineSERCOS interface

The invention discloses a method based on PCI-E interface full algorithm cryptographic card, including: a cryptographic algorithm module, a FLASH memory, a PCI-E bus interface, a random numb generator, and an FPGA master control chip with NIOS soft core processor, wherein a PCI-E IP core and an algorithm state machine are integrated in the FPGA master control chip. The cryptographic algorithm module comprises a symmetric key encryption SM4 algorithm chip, a symmetric key encryption SM1 algorithm chip and an asymmetric key encryption SM2 algorithm chip. The invention also discloses an encryption method of the cipher card. The invention provides a high-performance full-algorithm cryptographic card, which simultaneously reduces the complexity of hardware circuit and energy consumption, improves the key operation speed, and the cryptographic card adopts a home-made cryptographic algorithm, so that the user's key is most securely protected.

Owner:西安得安信息技术有限公司

On-line updating method for USB interface control panel

InactiveCN101131648AChange propertiesProgram loading/initiatingSoftware deploymentMachine controlUSB

This invention discloses a kind of USB interface control board online refresh method which includes the following steps: A. the embedded soft kernel processor receives the refresh command through the USB module and then fetches the refresh data sent by the epistemic machine and storages it in the embedded soft kernel processor's volatile memory; B. erase the original embedded soft kernel processor firmware or the FPGA allocation document in the non-volatile memory; C. program the original embedded soft kernel processor firmware or the FPGA allocation document in the volatile memory to the non- volatile memory. This invention uses the USB interface to refresh the control board if the medicine device and the control board can refresh the embedded soft kernel processor firmware or the FPGA hardware allocation absolutely through the epistemic machine control at the station of no influence to the user's normal use.

Owner:SHENZHEN MINDRAY BIO MEDICAL ELECTRONICS CO LTD

High speed servo controller with parallel processing structure based on FPGA

InactiveCN101251753AFast operationIncrease flexibilityNumerical controlParallel processingComputer science

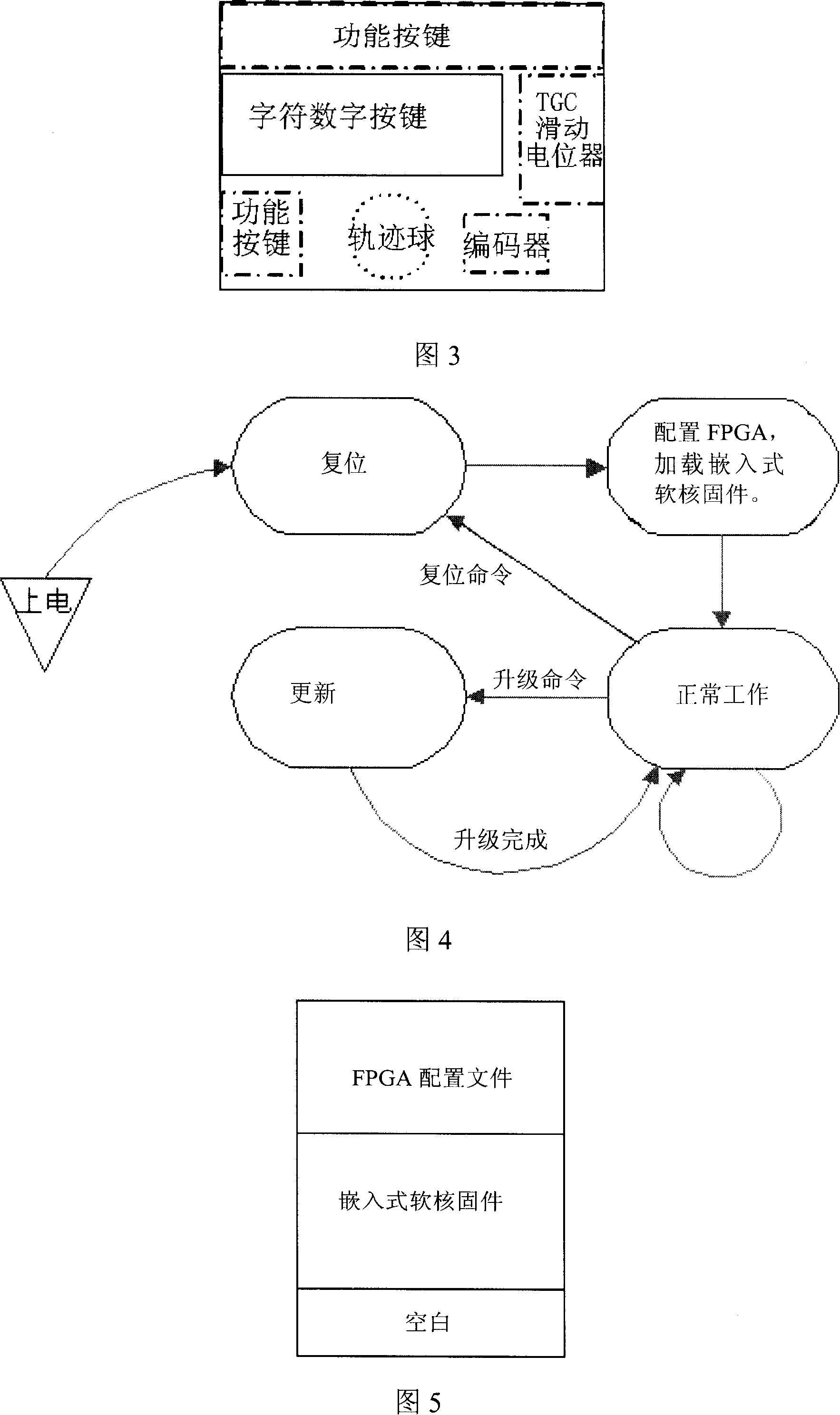

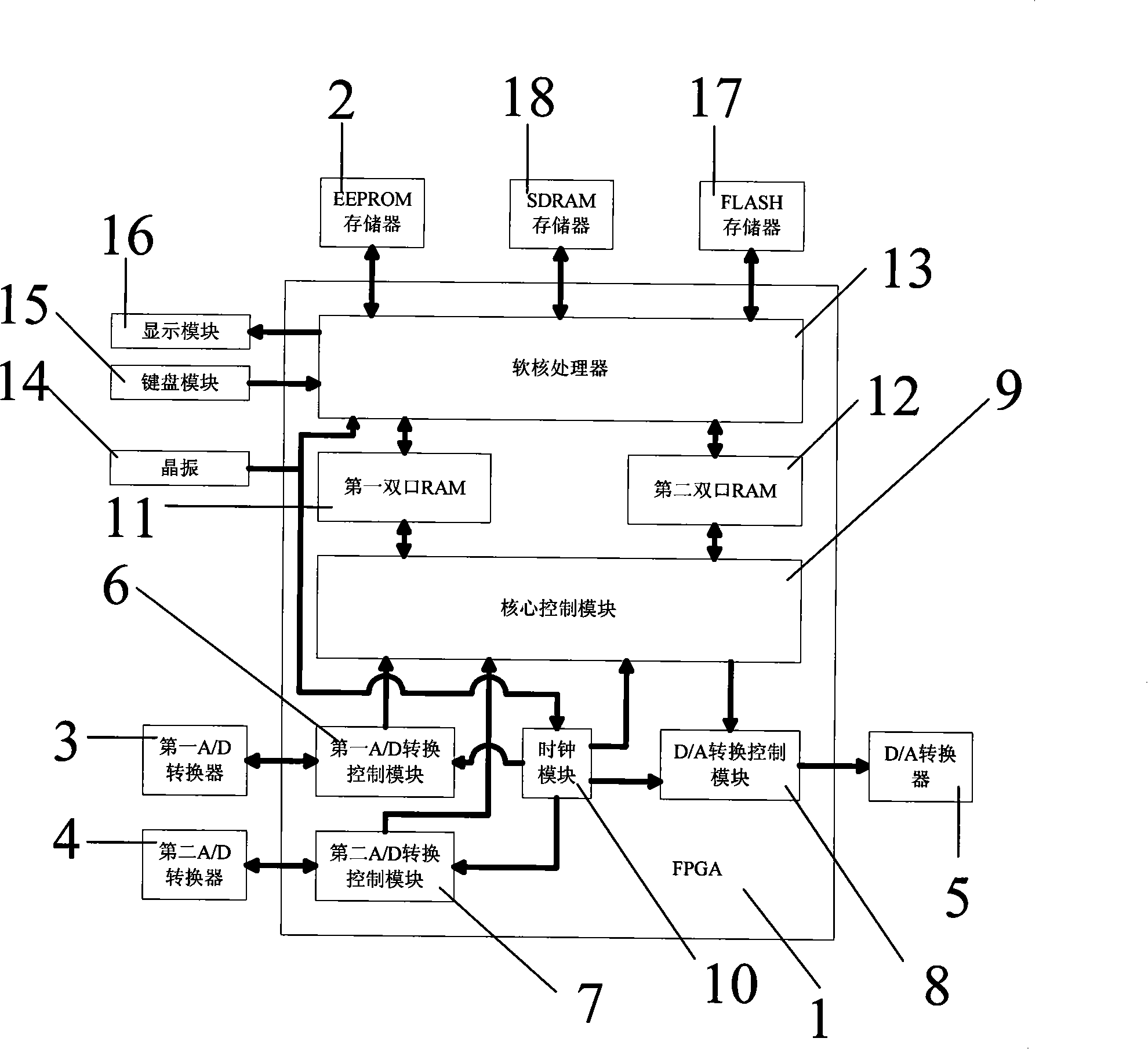

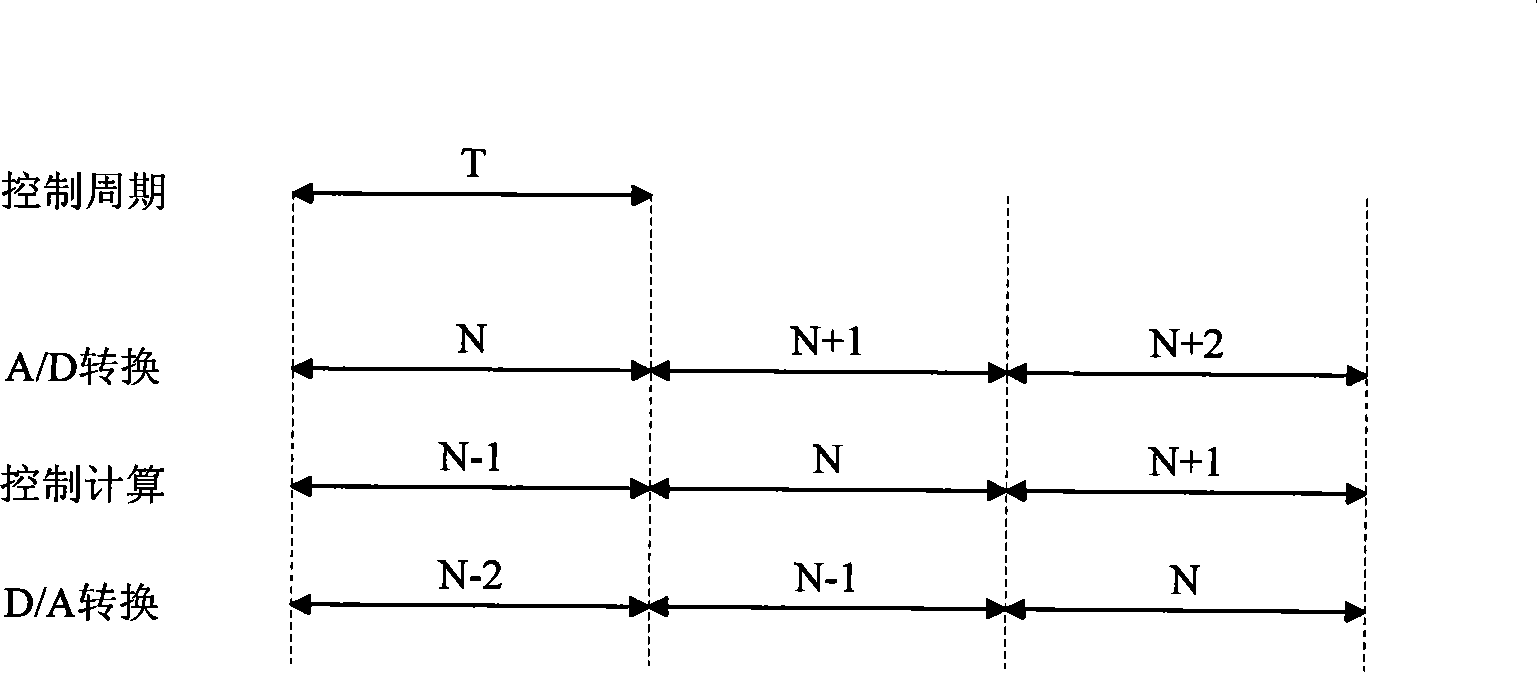

The present invention discloses a high-speed servo controller which is based on FPGA and has a parallel processing structure. The present invention comprises a field programmable gate array (FPGA), two A / D converters, a D / A converter, a crystal oscillator, a keyboard module, a display module, a FLASH memory, an SDRAM memory and an EEPROM memory, wherein the field programmable gate array comprises two A / D conversion control modules, a D / A conversion control module, a kernel control module for controlling calculation, a clock module, two dual-port RAMs and a soft-core processor. The servo controller can realize that the hardware realization of PID control calculation, as well as the pipeline realization parallel processing of A / D conversion, control calculation and D / A conversion, remarkably shortens control period, realizes the monitoring of the soft-core processor to the kernel control module as well as man-computer interaction, has extremely fast computing speed and high flexibility, can be widely applied to servo control systems in the industrial automation field, and is wide in application scope.

Owner:ZHEJIANG UNIV

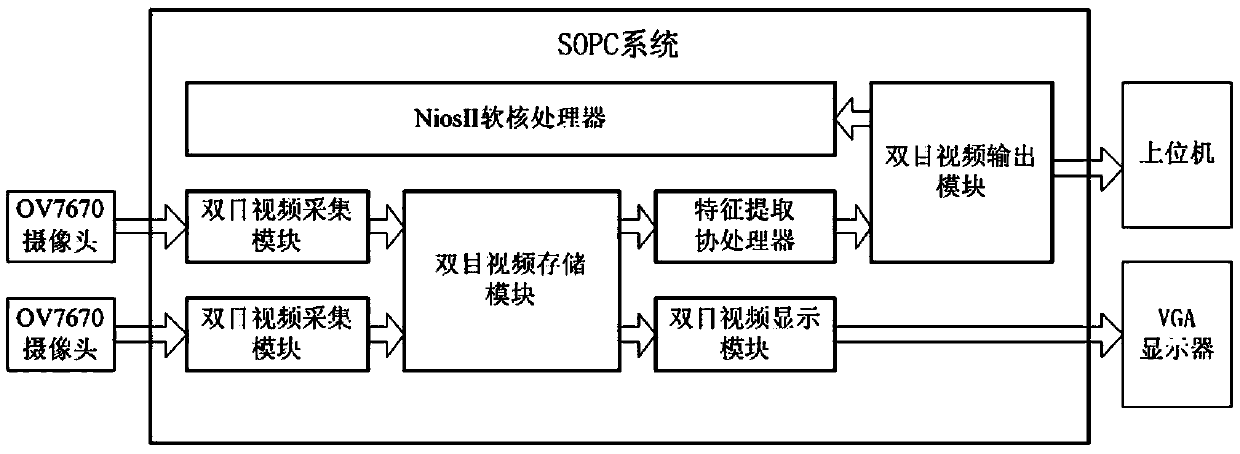

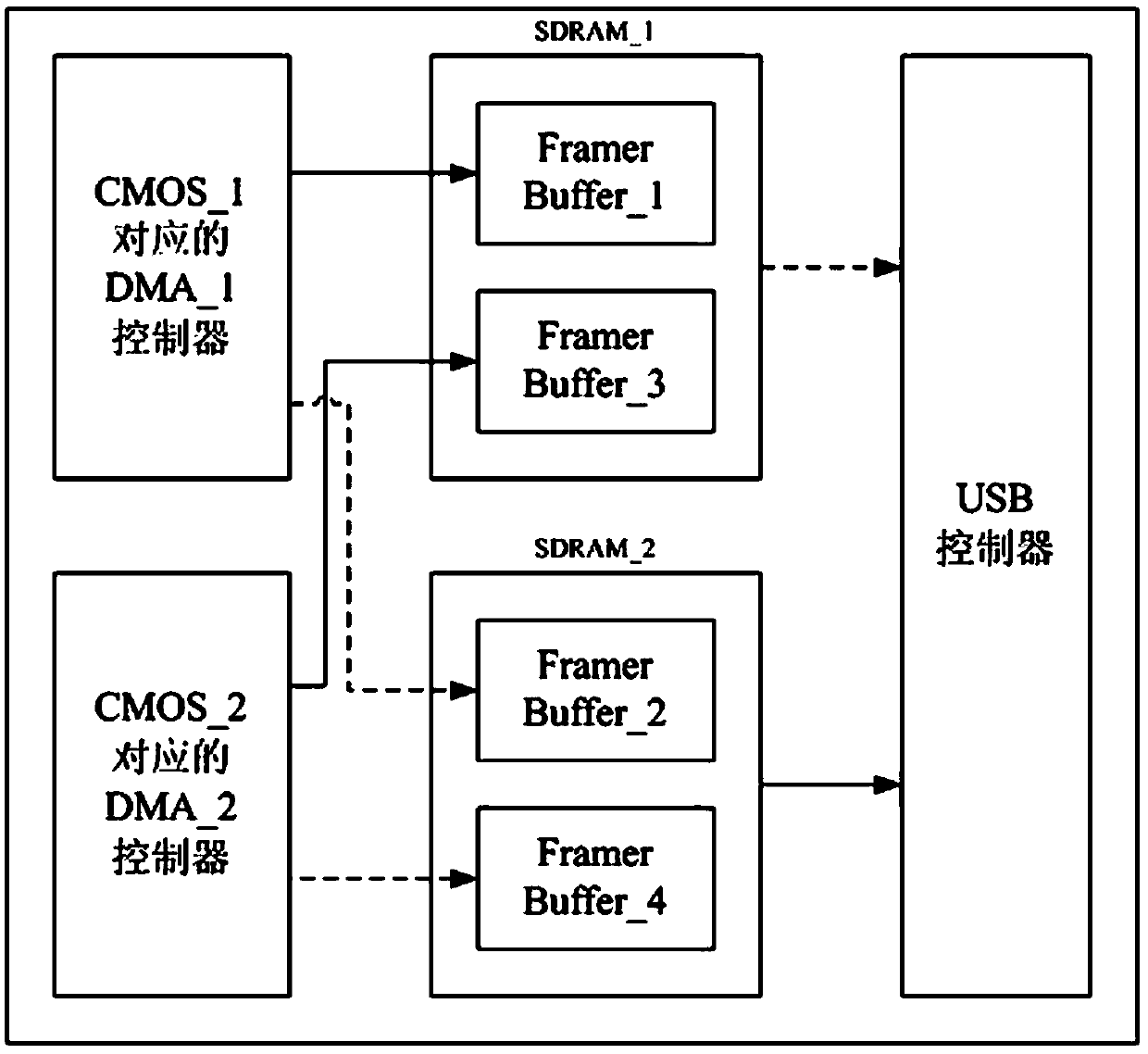

Binocular video splicing device based on SOPC and binocular video splicing method

ActiveCN103442180ASolve seam problemsTelevision system detailsColor television detailsCMOSVideo storage

The invention provides a binocular video splicing device based on an SOPC. The binocular video splicing device comprises an SOPC system making a NiosII soft-core processor as a core, wherein a pair of CMOS imaging sensors are connected with a pair of binocular video acquisition modules respectively through FPGA ports; the binocular video acquisition modules are connected with a binocular video storage module; one path of the output end of the binocular video storage module is connected with a binocular video output module through a feature extraction co-processor, and the other path of the output end of the binocular video storage module is connected with a binocular video display module; the binocular video output module is further respectively provided with the NiosII processor and an upper computer, and the binocular video display module is further connected with a VGA displayer. According to a binocular video splicing method, feature points are roughly matched through a Euclidean distance method, then partial mismatching points are extracted by means of a KNN method, a homograph matrix is calculated by the adoption of a RANSAC method at last, and real-time splicing for single-frame binocular video data is achieved through cylinder space conversion and linear weighing fusion.

Owner:GUILIN UNIV OF ELECTRONIC TECH

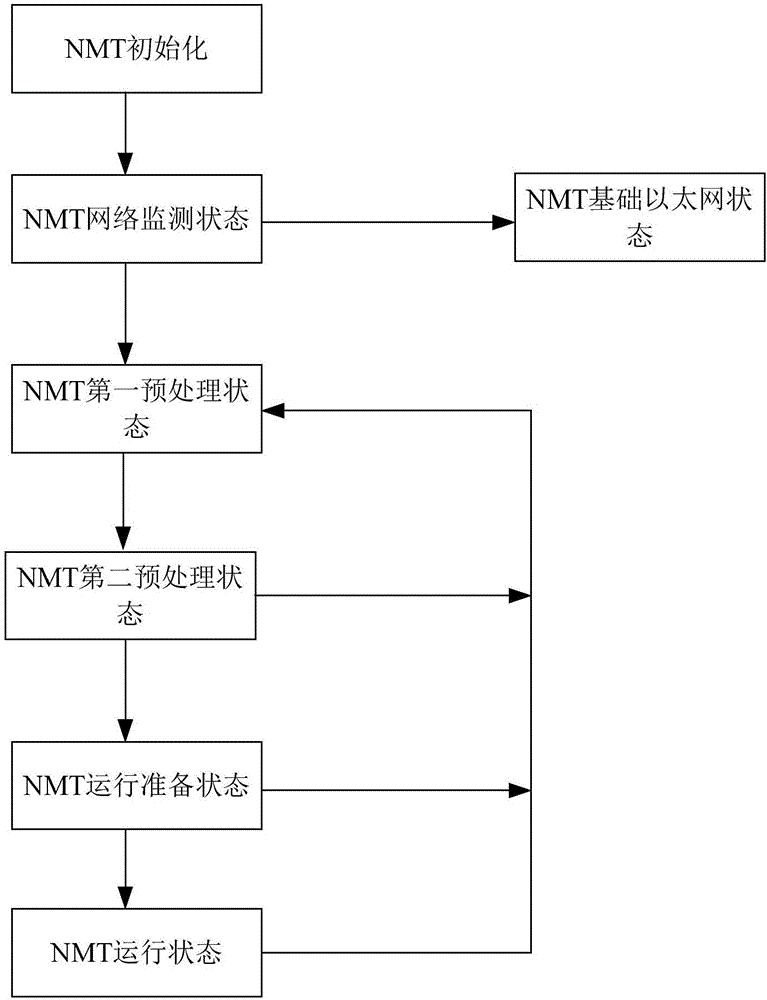

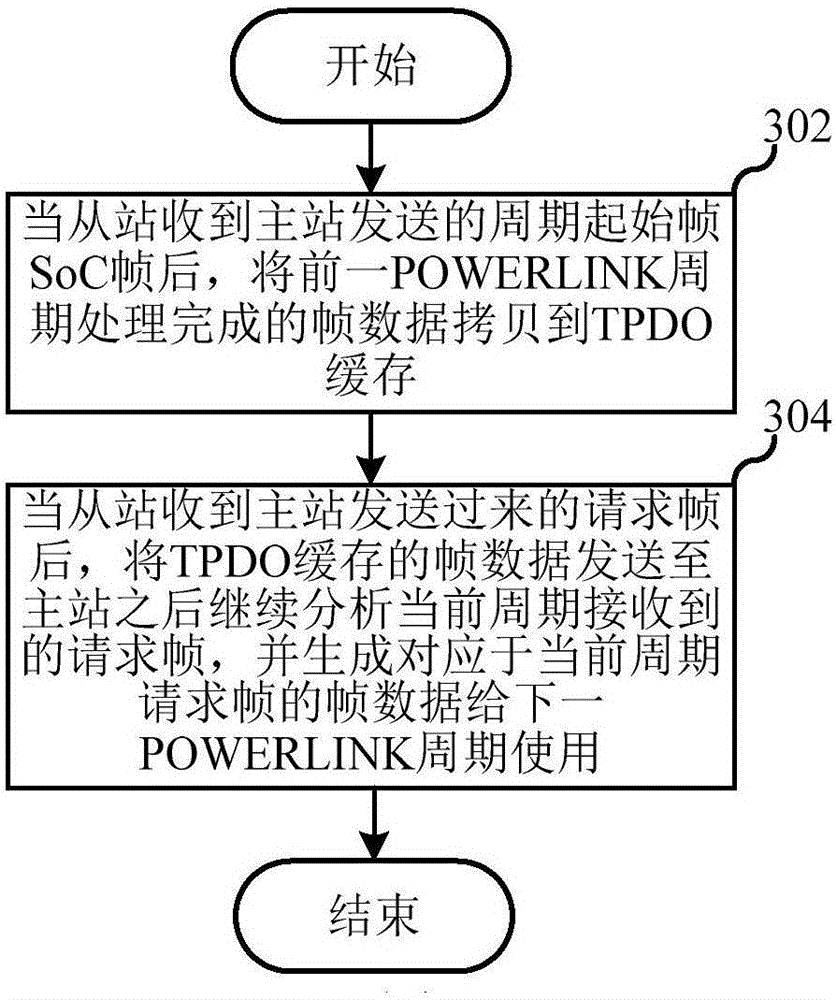

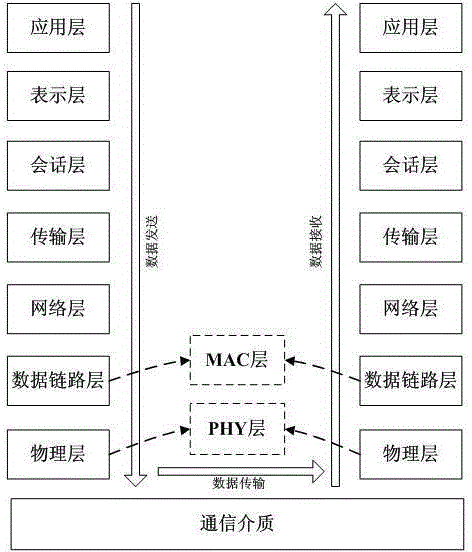

POWERLINK communication protocol hardware realization method

The invention relates to the technical field of industrial Ethernet communication protocols, and discloses a POWERLINK communication protocol hardware realization method. In the embodiment of the invention, the method comprises steps: a data link layer and a physical layer interface of the POWERLINK communication protocol are realized based on any one chip selected from the following: a programmable logic device, a custom hardware chip and a semi-custom hardware chip; and the application layer of the POWERLINK communication protocol is realized based on any one mode selected from the following: a soft core processor, an embedded processor, and a general processor. POWERLINK master station equipment or slave station equipment obtained by adopting the realization method has a high data transmission response capability, high-speed and high-precision industrial field control requirements are met, the expansibility is more flexible, any object dictionary and any number of slave stations can be supported, the cost performance is good, and software and hardware are easy to realize and maintain.

Owner:SHANGHAI STEP ELECTRIC +1

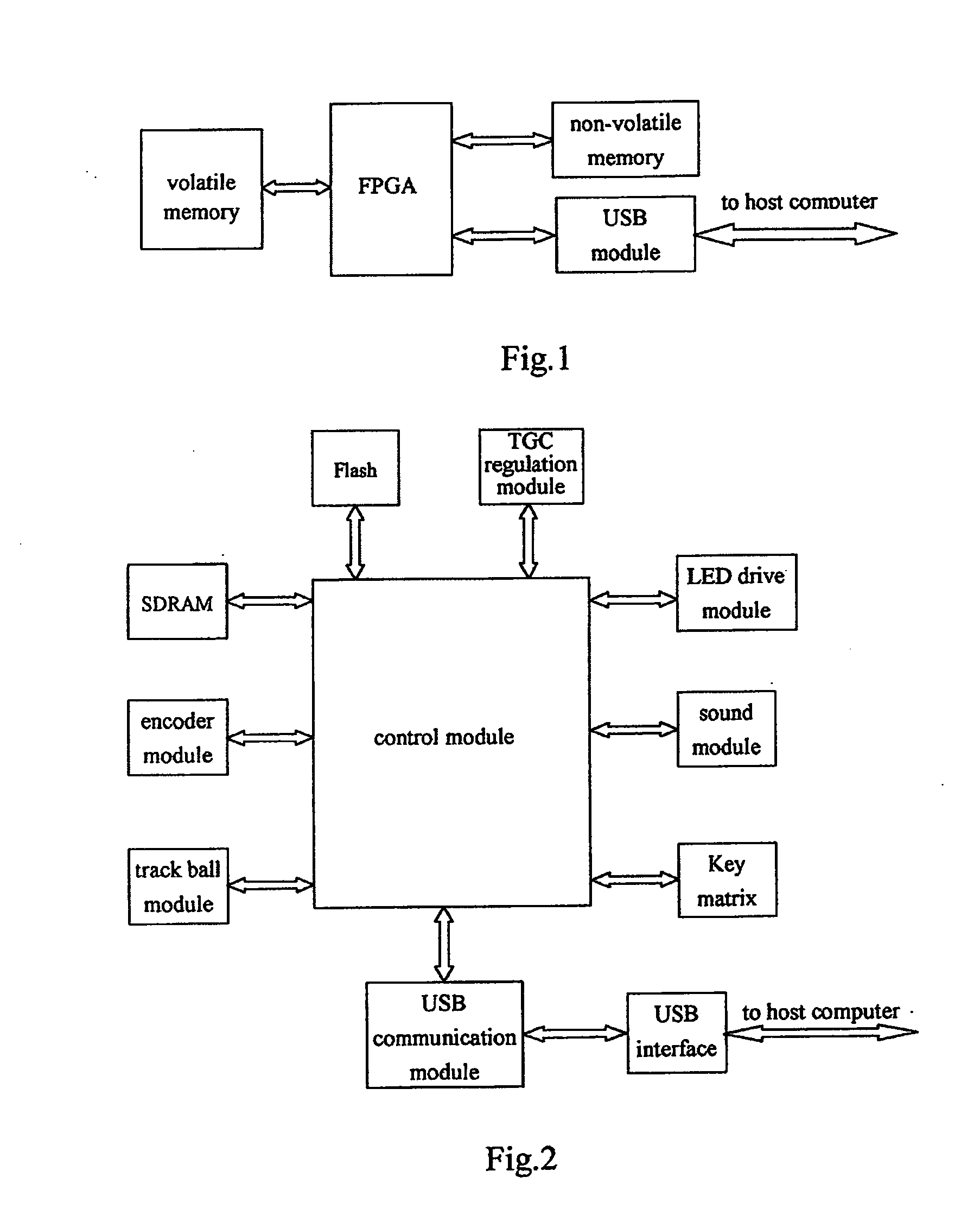

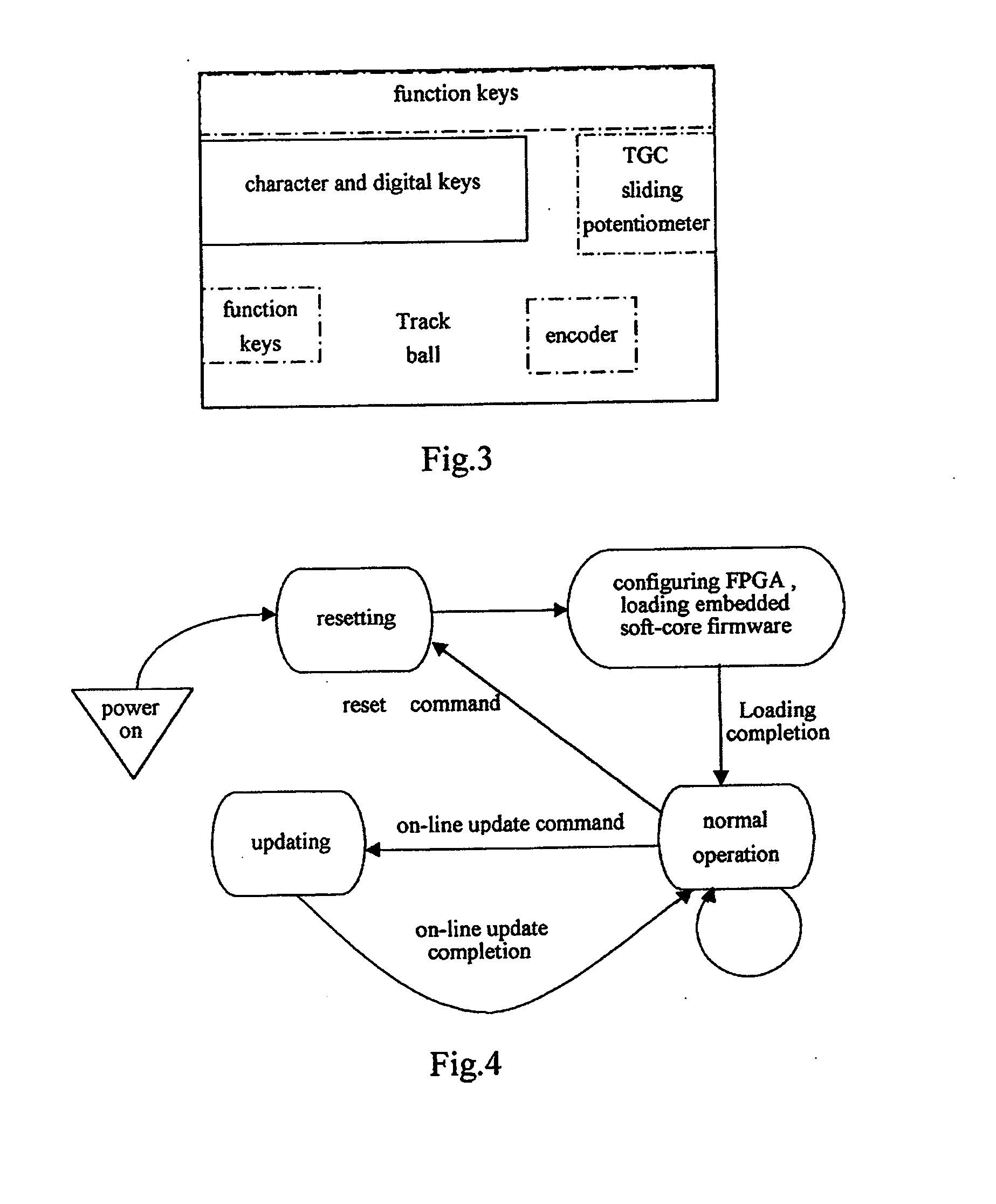

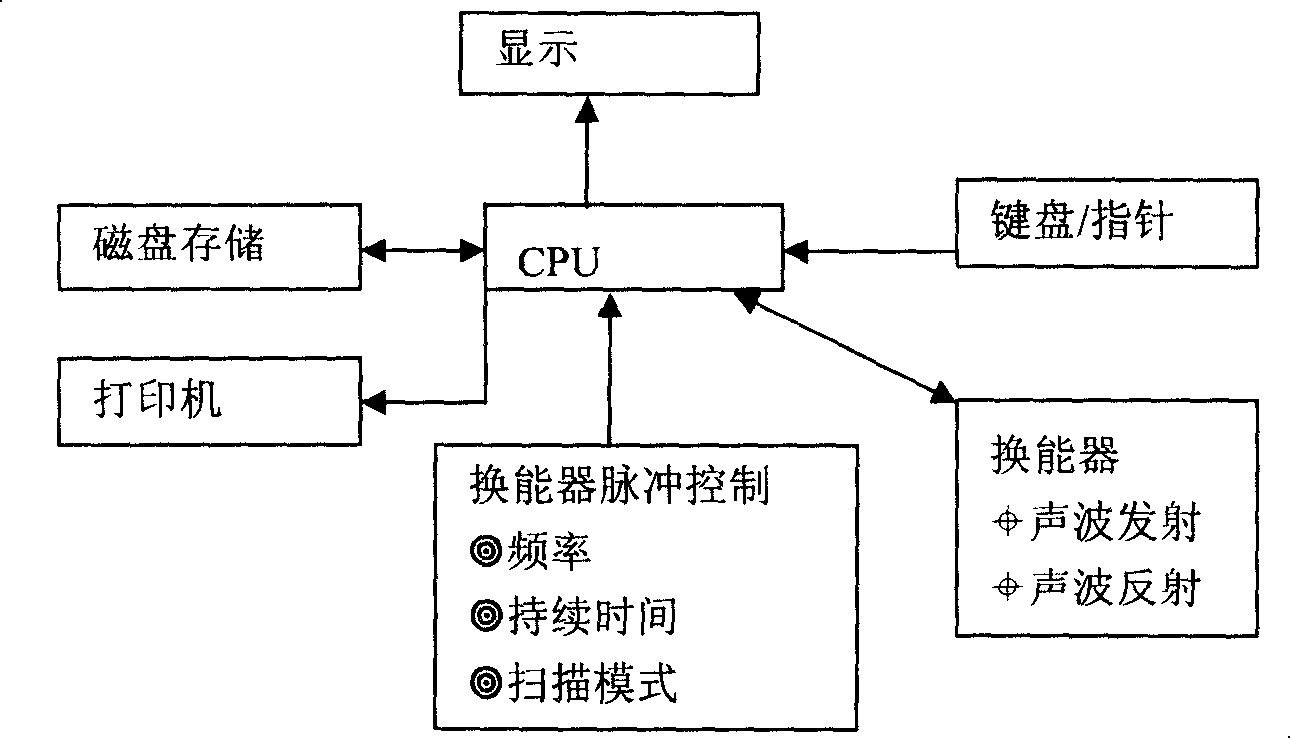

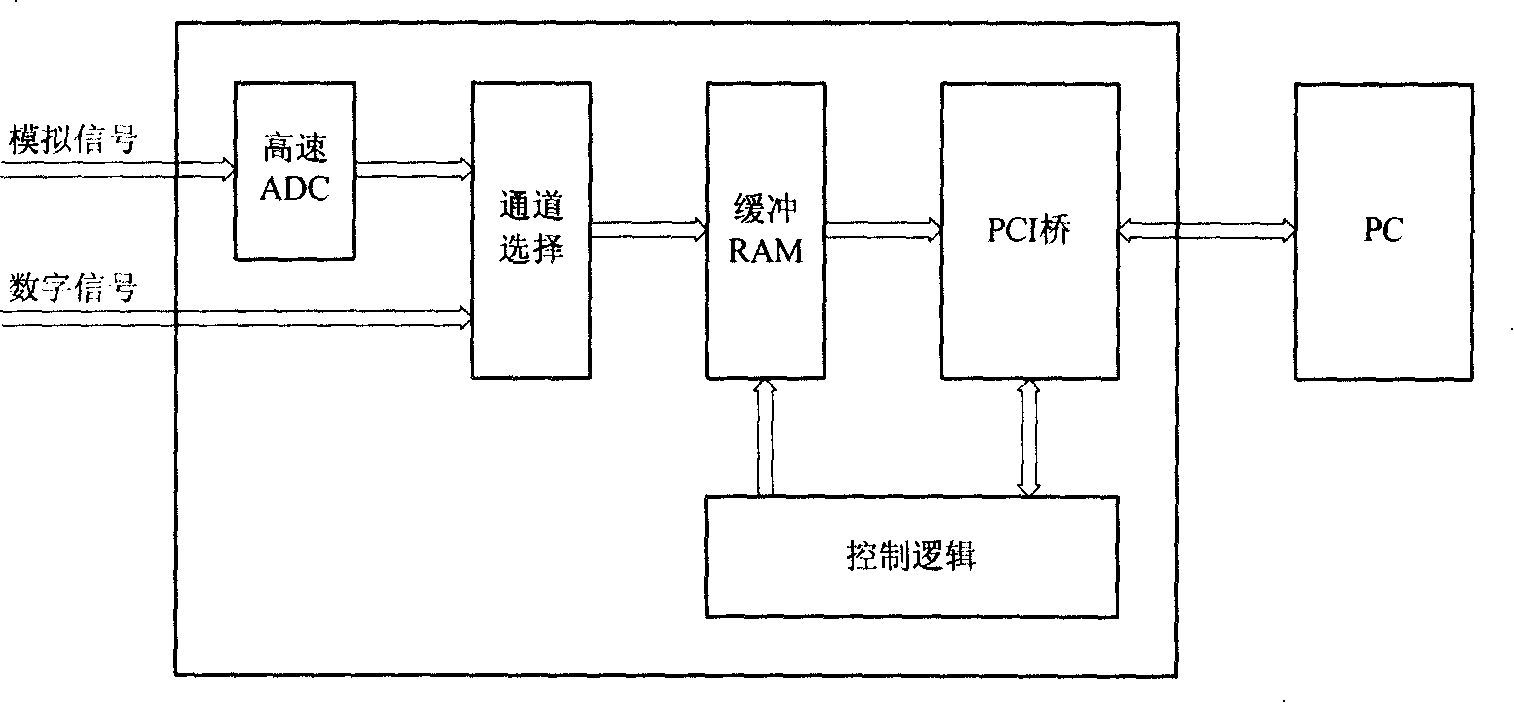

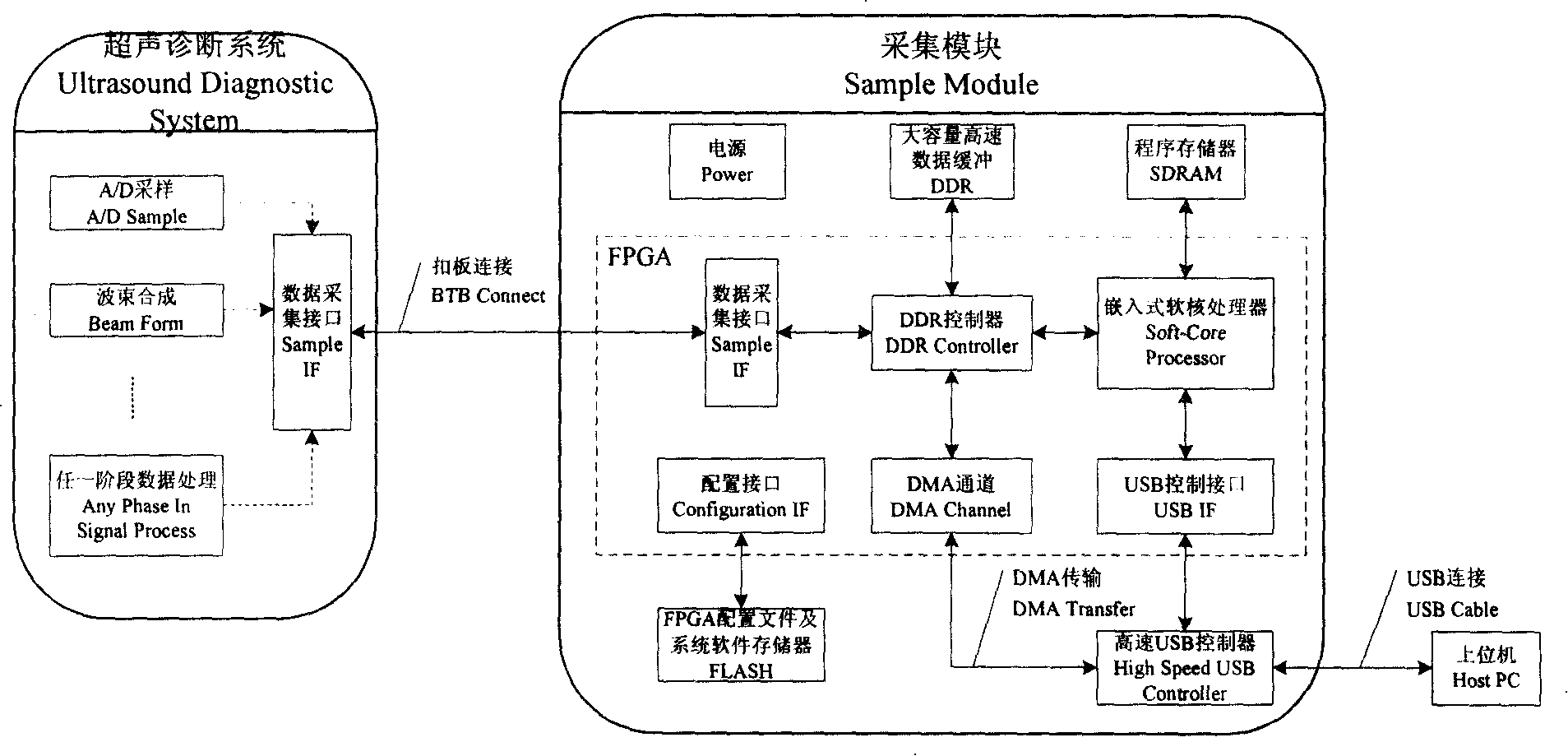

Method and apparatus for gathering ultrasonic diagnosis system high-speed radio-frequency echo wave data

InactiveCN101185580ARealize acquisitionRealize transmissionUltrasonic/sonic/infrasonic diagnosticsWave based measurement systemsSonificationData acquisition

Owner:SHENZHEN MINDRAY BIO MEDICAL ELECTRONICS CO LTD

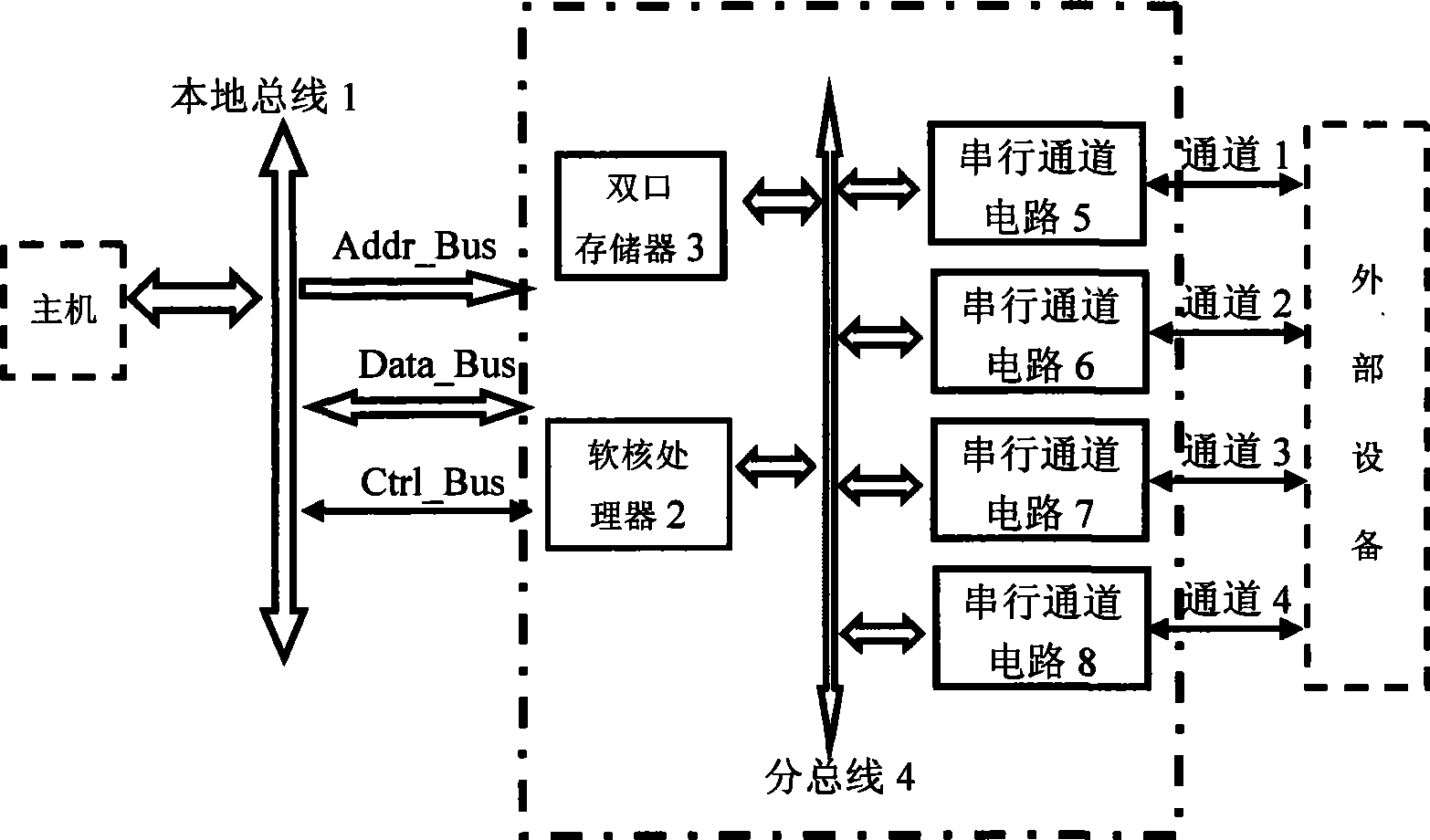

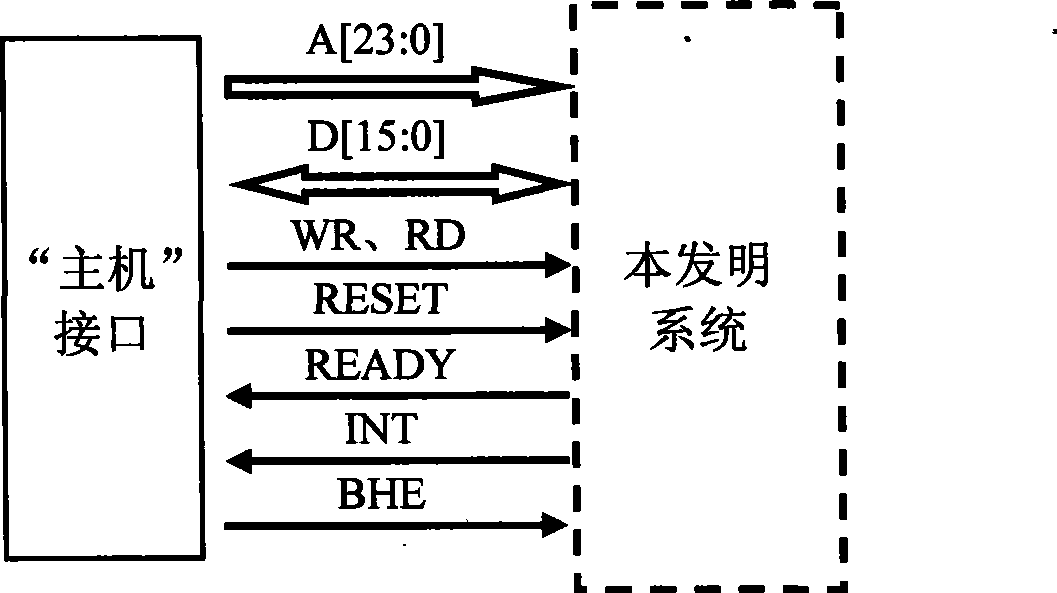

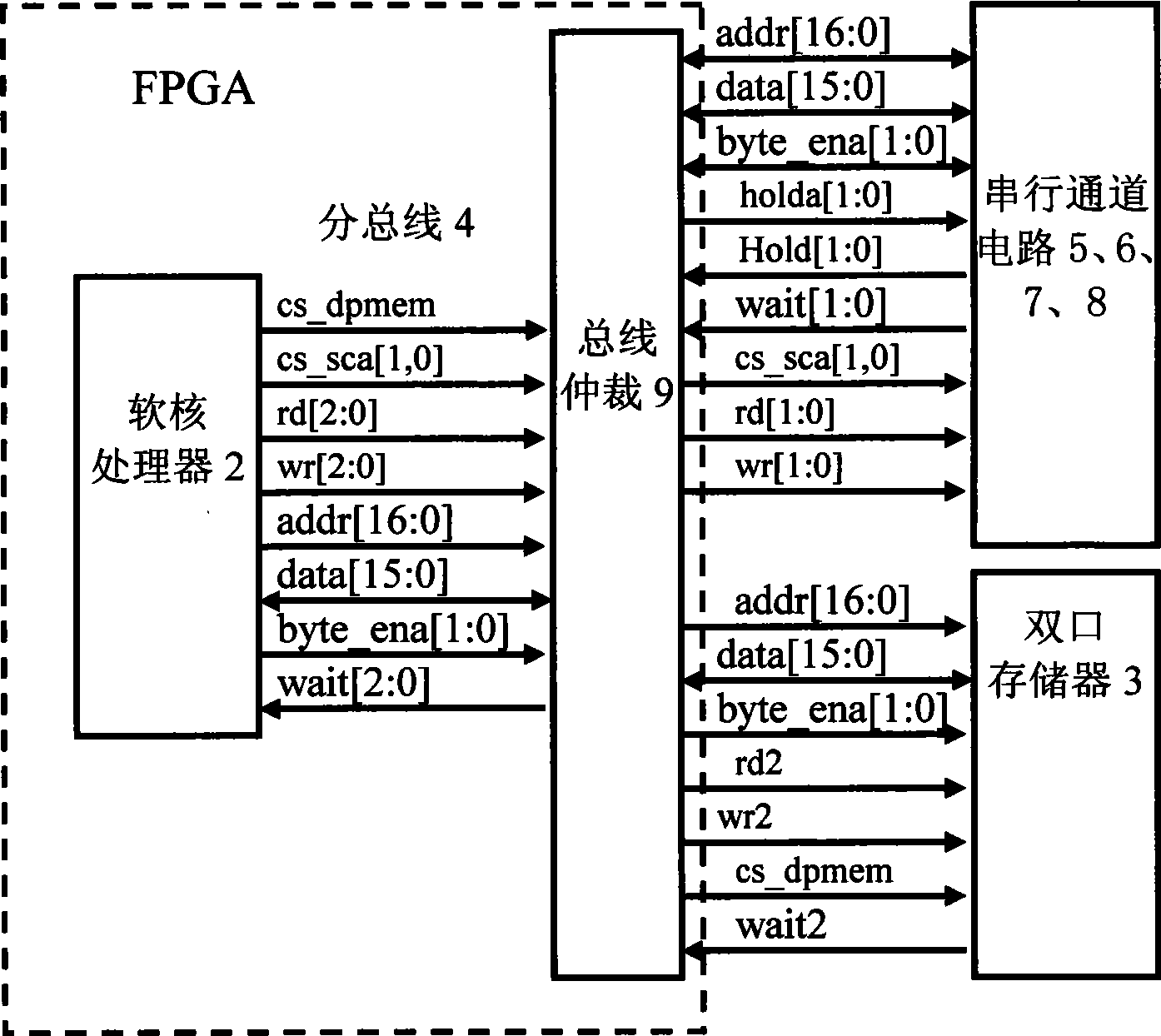

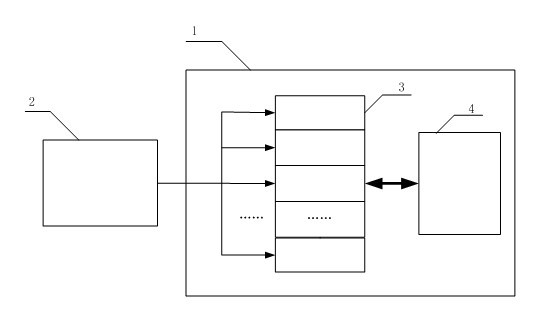

Modular communication control system

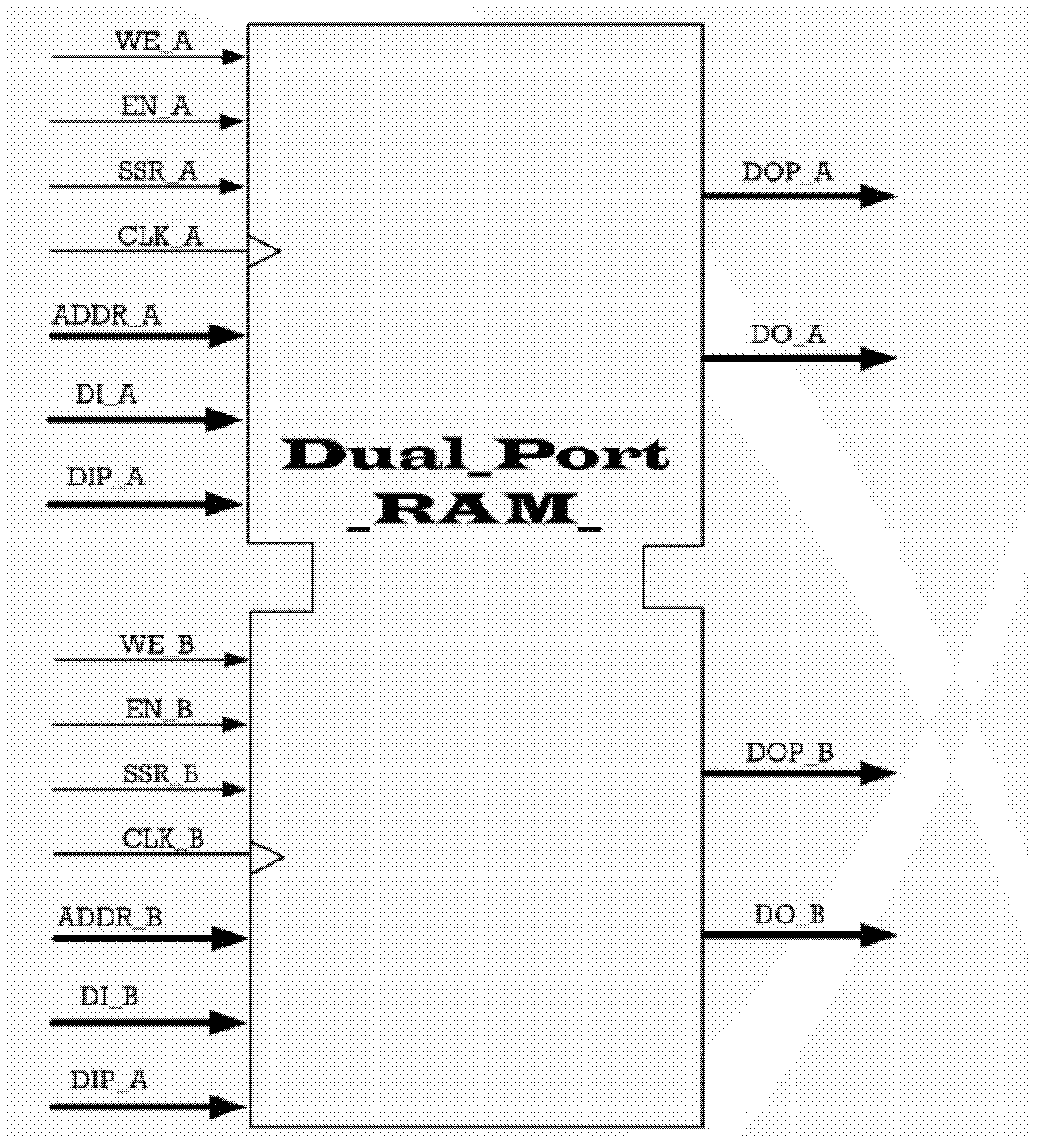

InactiveCN101436171ASimple external interfaceImprove work efficiencyElectric digital data processingControl systemModularity

The invention provides a modularized communication control system arranged between a host computer and external equipment. The system comprises a local bus, a double-port memorizer, a soft-core processor, a sub-bus and four serial channel circuits. The double-port memorizer and the host computer carry out bidirectional communication through the local bus; the soft-core processor reads information of the double-port memorizer through the sub-bus and sends data to the external equipment through the four serial channel circuits; and the soft-core processor also reads data transmitted from the external equipment through the four serial channel circuits and stores the data in the double-port memorizer through the sub-bus. With the modularized communication control system, a designer can place a plurality of the modularized communication control systems on the local bus according to requirements and expands serial data channels with the number of multiple of four. The modularized communication control system improves the design efficiency of using one host computer to control a multiway serial communication passage.

Owner:THE 28TH RES INST OF CHINA ELECTRONICS TECH GROUP CORP

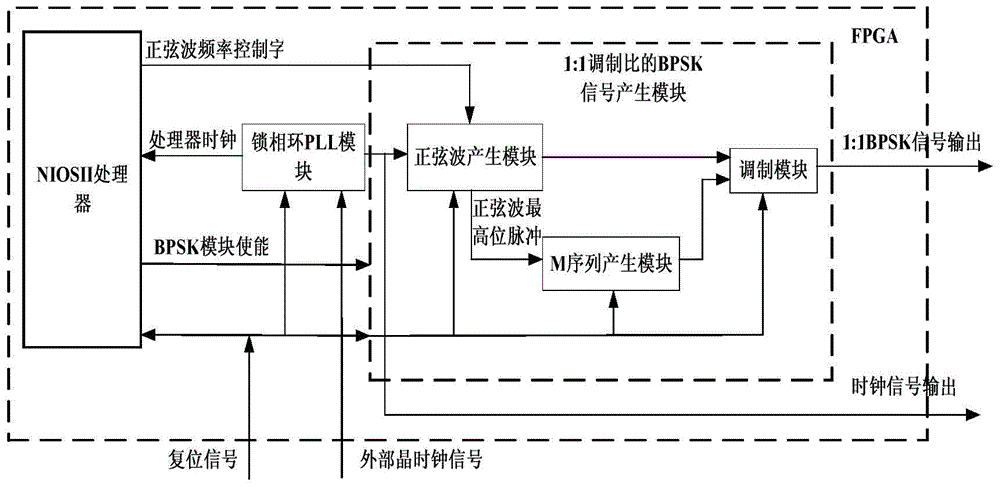

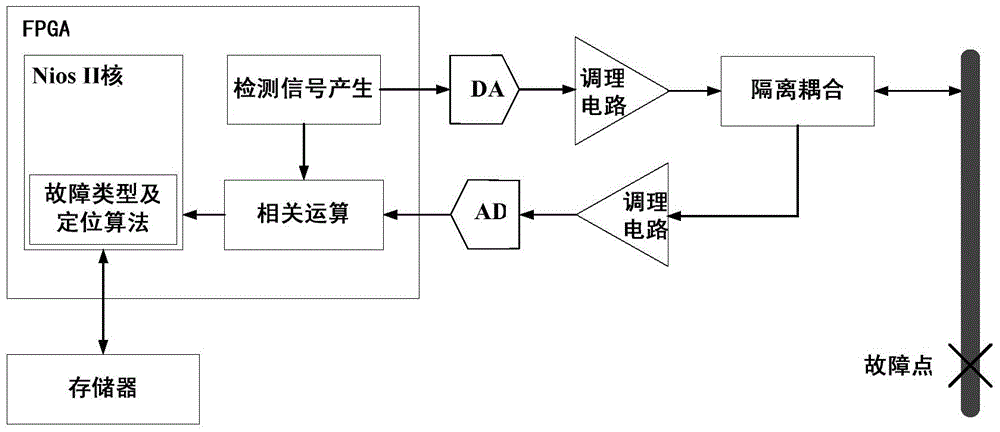

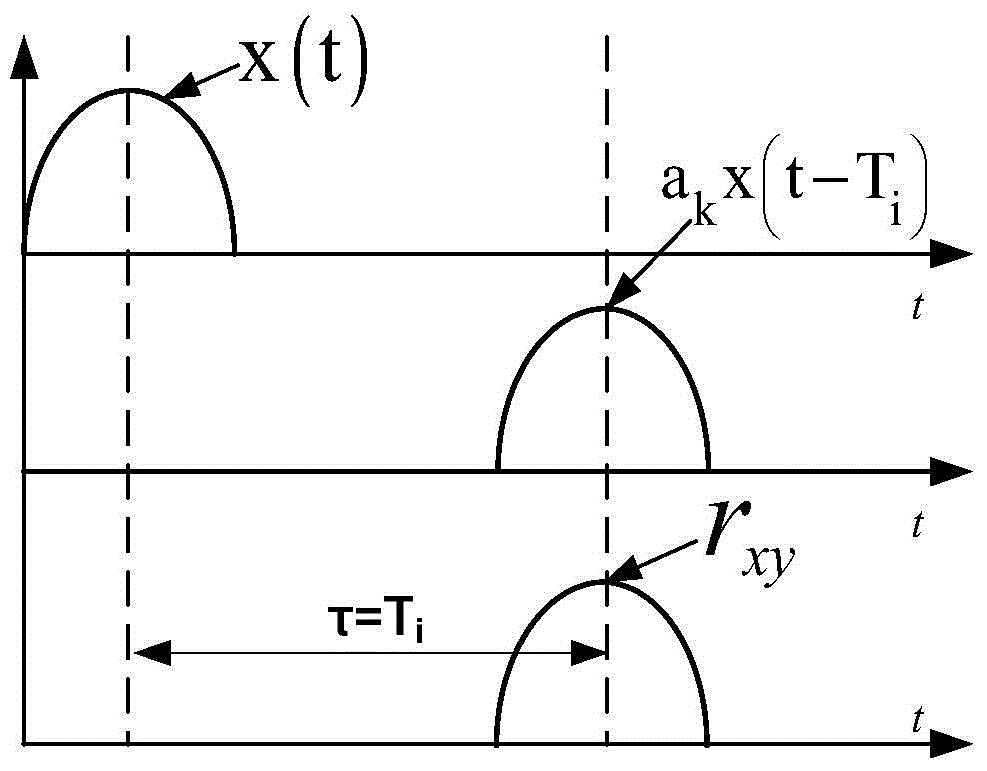

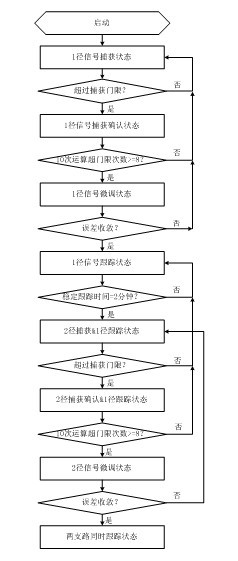

Cable fault on-line detecting and positioning device

InactiveCN104977504AOnline detection does not affectLow signal to noise ratioFault locationComputer moduleSoft core processor

The invention discloses a cable fault on-line detecting and positioning device. The device includes an FPGA module with an NIOS II soft core processor, a high-speed DA module, an isolation coupling module, a high-speed AD module and a conditioning circuit. The FPGA module provides clocks needed by all modules, generates a detection signal formed by modulation of an m sequence and sine waves, performs related operation processing of the detection signal and a reflection signal, and positions cable faults. The high-speed DA module is used for digital analog conversion of the detection signal generated by the FPGA module. The isolation coupling module isolates an output signal of the high-speed DA module and couples the output signal to a cable, and also isolates a reflection signal in the cable and couples the reflection signal to a detection positioning device. The high-speed AD module carries out analog-to-digital conversion of the reflection signal in the cable and then sends the signal to the FPGA module for processing. The conditioning circuit is used for conditioning the output signal of the high-speed DA module and an input signal of the high-speed AD module. The device has an on-line detection function, is high in positioning precision, and exhibits a high anti-interference capability.

Owner:SHANDONG INST OF AEROSPACE ELECTRONICS TECH

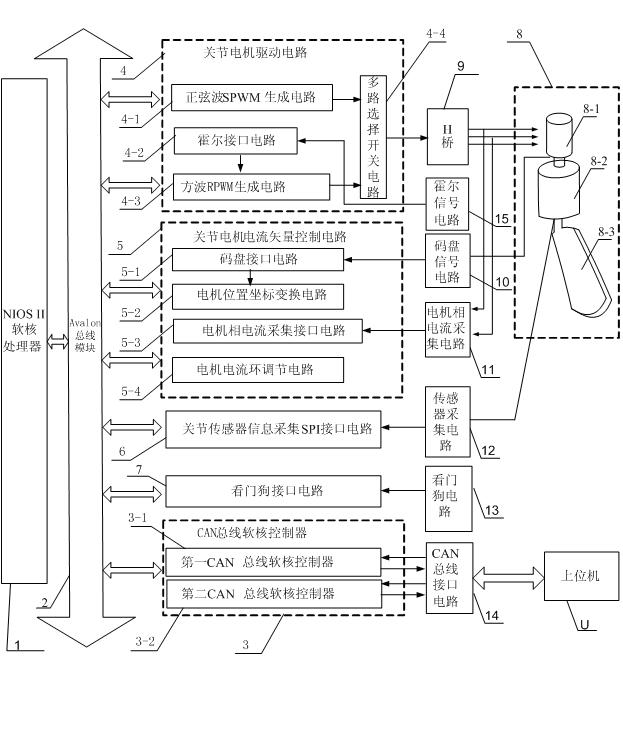

On-chip control system of digital articulation based on FPGA (Field Programmable Gate Array)

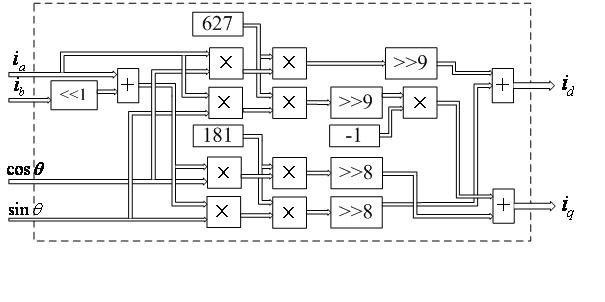

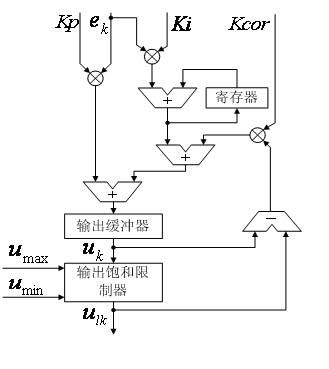

InactiveCN101819427AHighly integratedAchieve accessElectronic commutation motor controlVector control systemsDigitizationCurrent vector

The invention relates to an on-chip control system of a digital articulation based on an FPGA (Field Programmable Gate Array), relating to the field of robots and solving the problem that the traditional robot articulation control system has low integrated level. The on-chip control system comprises an NIOSII soft-core processor, an Avalon bus module, a CAN bus soft-core controller, an articulation motor driving circuit, an articulation motor current vector control circuit and an articulation sensor information acquisition SPI (Single Program Initiation) interface circuit, wherein the communication end of the NIOSII soft-core processor is respectively connected to the communication ends of the CAN bus soft-core controller, the articulation motor driving circuit, the articulation motor current vector control circuit and the articulation sensor information acquisition SPI interface circuit through the Avalon bus module. The invention is suitable for the controllers of the mechanical arm articulations.

Owner:HARBIN INST OF TECH

Global navigation satellite system (GNSS) receiver system based on delay locked loop (DLL)-Rake tracking loop

InactiveCN102176026AEfficient separationEliminate the effects ofSatellite radio beaconingRadio transmissionCarrier signalDelay-locked loop

The invention discloses a global navigation satellite system (GNSS) receiver system based on a delay locked loop (DLL)-Rake tracking loop, which belongs to the field of positioning navigation. The system comprises a baseband processing chip module and a GNSS radio frequency processing chip module, wherein the baseband processing chip module consists of correlator modules of 12 channels and a MicroBlaze soft core processor module; the correlator modules of each channel read GNSS digital intermediate frequency signals from the GNSS radio frequency processing chip module, and transmit an accumulative correlation value, obtained by two branches, of a satellite signal and original measured values to the MicroBlaze soft core processing module; and the MicroBlaze soft core processor module controls the correlator modules according to the accumulative correlation value, regulates carrier loops and code loops of the correlator modules to make the system work in different states, and calculates position, velocity and time (PVT) information according to the measured values. The system improves the positioning accuracy and satellite capturing velocity of a GNSS receiver.

Owner:张淑芳 +4

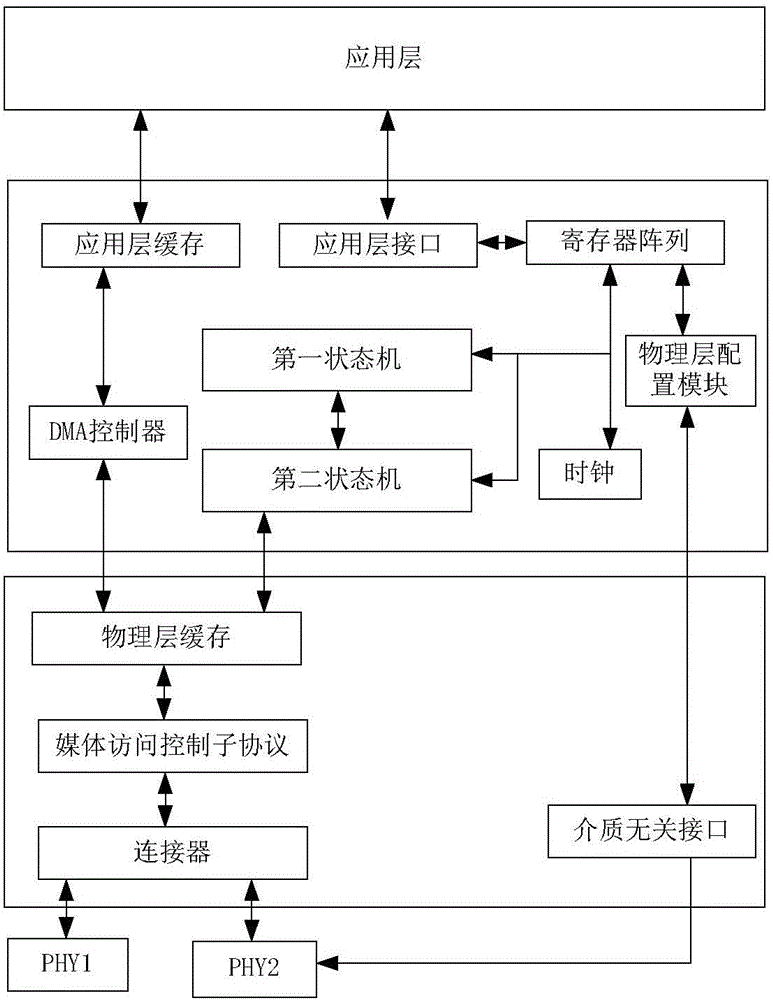

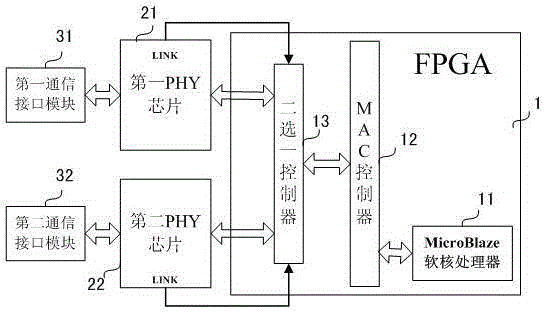

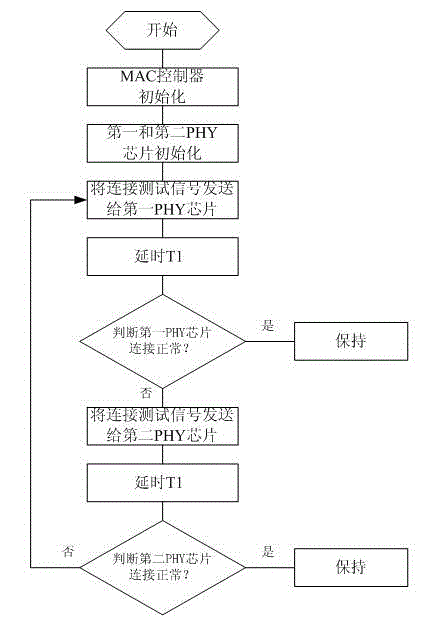

Dual-network switching device based on FPGA (field programmable gate array) and dual-network switching method thereof

The invention discloses a dual-network switching device based on a FPGA (field programmable gate array). The dual-network switching device comprises a FPGA chip, a first PHY (physical layer) chip, a second PHY chip, a first communication interface module and a second communication interface module, wherein the FPGA chip comprises a MicroBlaze soft core processor, an MAC (measurement and control) controller and an alternative controller; the MicroBlaze soft core processor is electrically connected with the MAC controller in a bidirectional manner; the MAC controller is electrically connected with the alternative controller in the bidirectional manner; the alternative controller is electrically connected with the first and the second PHY chips in the bidirectional manner respectively; the alternative controller is used for selectively connecting the MAC controller to one of the first and the second PHY chips; the first and the second PHY chips are respectively connected with the first and the second communication interface modules electrically in the bidirectional manner in a one-to-one correspondence manner. The invention further discloses a method for performing dual-network switching on the dual-network switching device based on FPGA. Dual-network switching is realized through hardware, so that communication instantaneity is improved.

Owner:中国船舶集团有限公司第七一一研究所

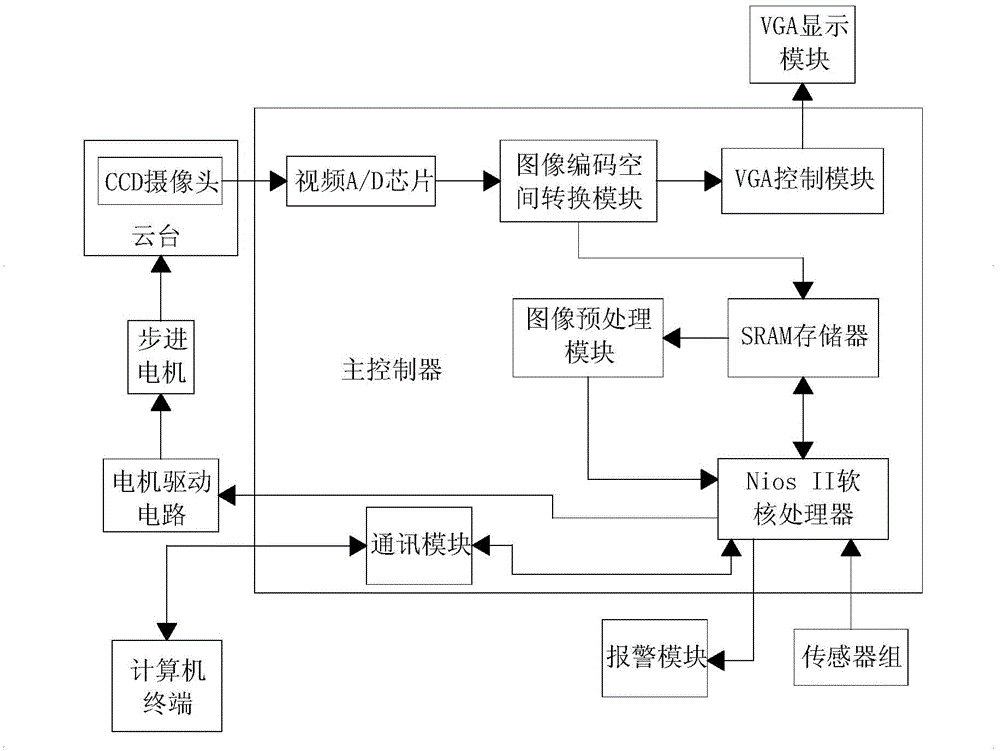

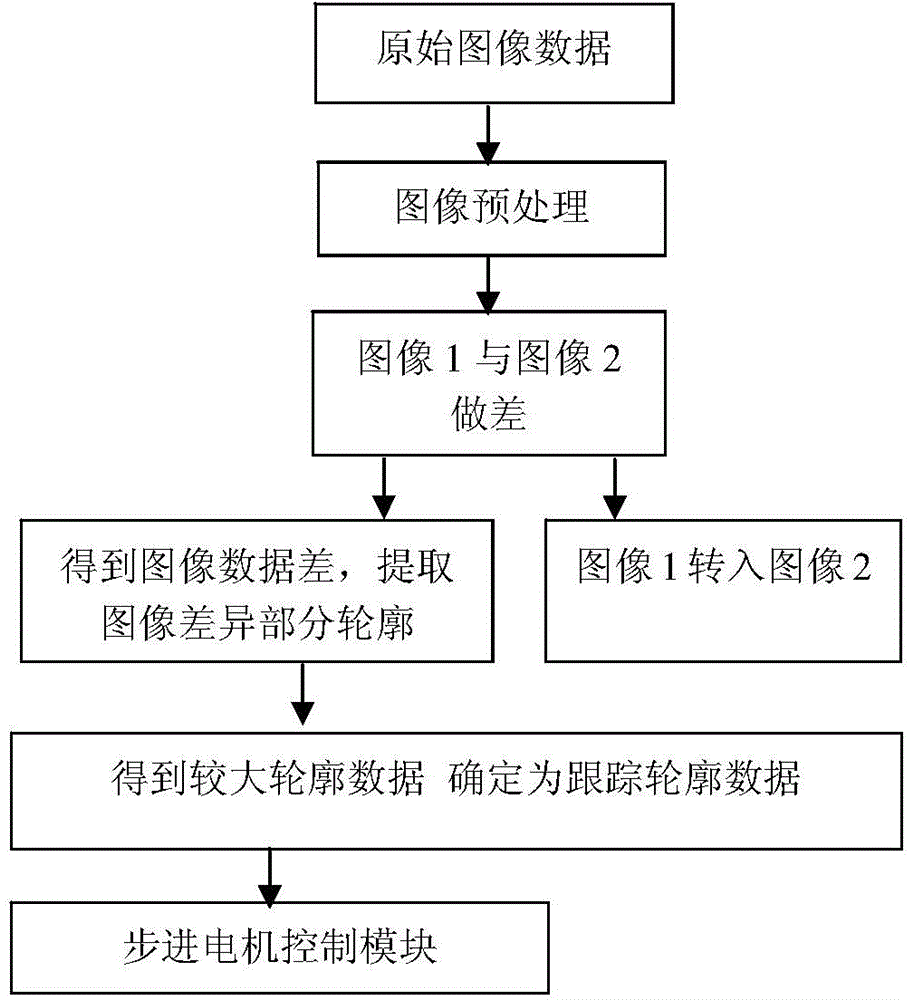

Indoor intelligent video monitoring system based on SOPC

InactiveCN104935886AEasy to upgradeSupport remote network monitoringClosed circuit television systemsBurglar alarmVideo monitoringCyclone

The invention discloses an indoor intelligent video monitoring system based on SOPC, comprising a CCD camera, a holder, a stepping motor, a motor-drive circuit, a sensor group, a master controller combined by a Nios II soft core processor and a Cyclone II, a VGA display module, an alarm module and a computer terminal. The indoor intelligent video monitoring system is a platform for tracking an object and alarming by basing on a robot vision technology of the SOPC technology and the sensor technology, and is capable of alarming according to the setting values of temperature, humidity, smog and people activity and transmitting the alarm information to the remote user. The indoor intelligent video monitoring system based on the SOPC is a monitoring system which can finish the mission in the short time according to the user customization, can support the remote network monitoring, and is applicable to the household, the shopping mall and the library.

Owner:NINGXIA UNIVERSITY

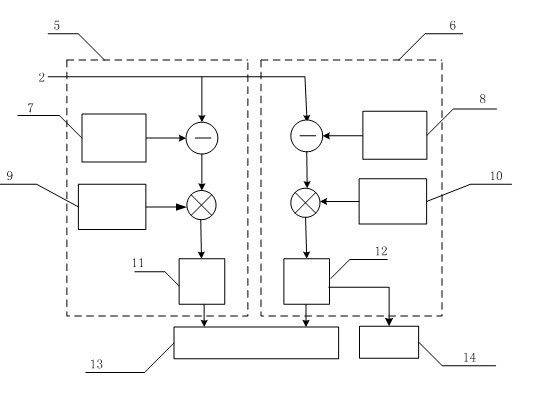

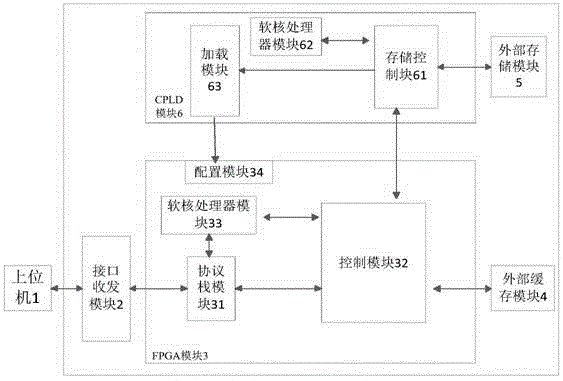

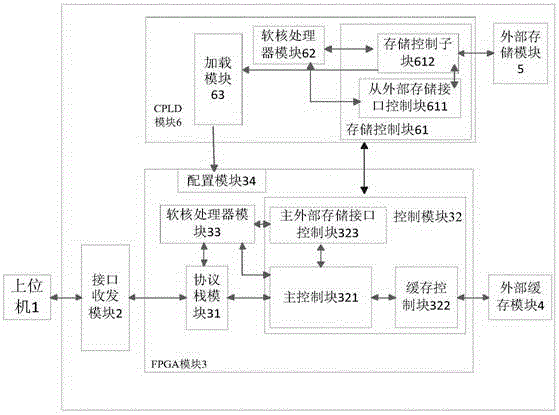

FPGA (Field Programmable Gate Array) multi-mirror upgrading-loading method and device based on soft-core processor

ActiveCN105573789ARemote upgrade time shortenedMeet diversityProgram loading/initiatingSoftware deploymentExternal storageComputer module

The invention discloses an FPGA (Field Programmable Gate Array) multi-mirror upgrading-loading method based on a soft-core processor. A single FPGA way is adopted, and the soft-core processor and control modules are embedded inside to implement an interface function; a program file caching function is implemented; and a chip scale interconnected bus interface function is implemented together with a CPLD (Complex Programmable Logic Device). The upgrading-loading method is implemented by an FPGA and the CPLD. The invention also discloses an FPGA multi-mirror upgrading-loading device based on the soft-core processor. The device comprises an upper computer, an interface receiving-transmitting module, an FPGA module, an external caching module, an external storage module and a CPLD module. Through adoption of the FPGA multi-mirror upgrading-loading method and device, FPGA multi-mirror rapid upgrading and flexible loading based on different application scenes are realized.

Owner:WUHAN JINGCE ELECTRONICS GRP CO LTD

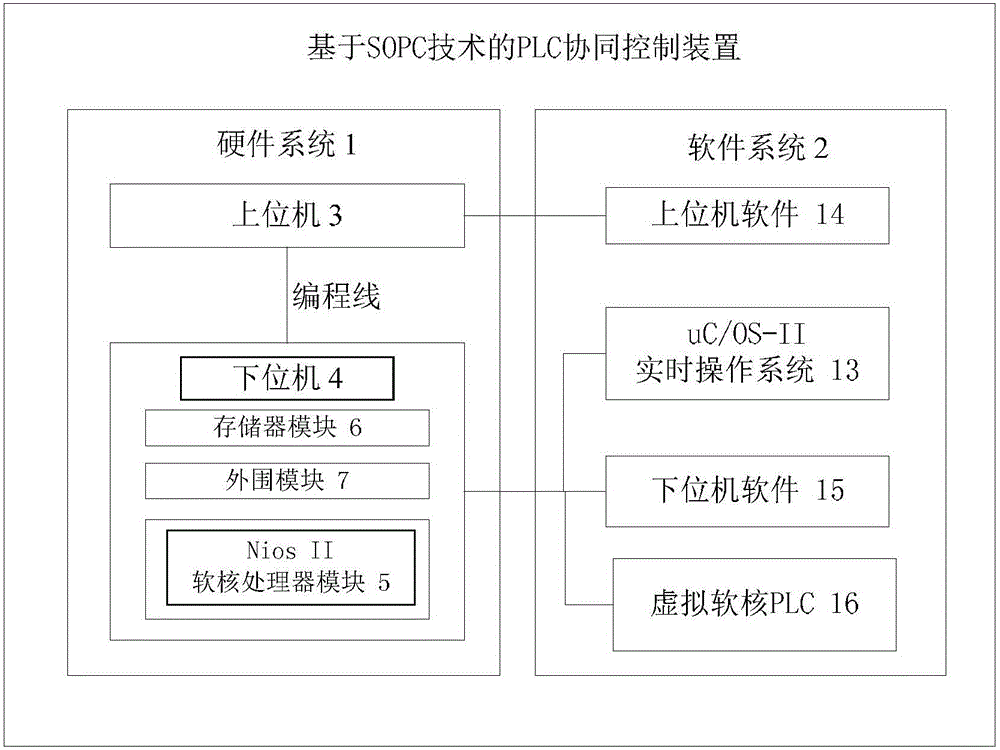

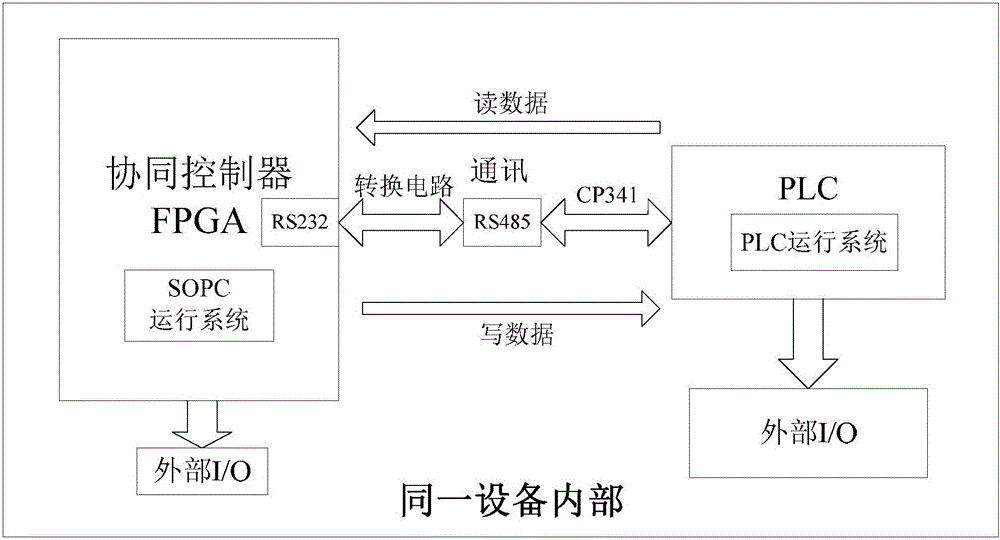

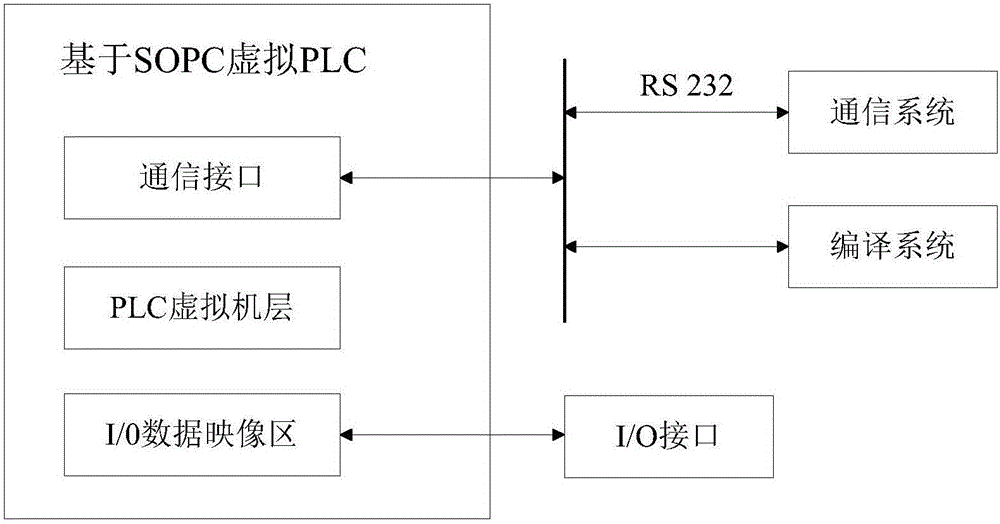

PLC cooperative control device based on SOPC technology

InactiveCN105137800AHigh densityIncrease or decrease quantityProgramme controlComputer controlOperational systemSoftware system

The invention relates to a PLC cooperative control device based on an SOPC technology. The device comprises two parts, a hardware system and a software system. The hardware system comprises an upper computer and a lower computer. The upper computer is formed by a Nios II soft core processor module, a memory module and a peripheral module, wherein the Nios II soft core processor module is composed of a CPU module, a TIMER0 module, a TIMER1 module, an UART module and a JTAG module. The software system comprises an embedded uC / OS-II real-time operating system, upper computer software, lower computer software and a virtual soft core PLC. The PLC cooperative control device is high in modifiability and transportability; the uC / OS-II real-time operating system is added, the operation real-time performance of the system is ensured, customized IP cores can be compiled according to specific requirements, and the required specific functions can be added freely; in addition, the number of I / O ports can be conveniently increased or reduced, so that the system is high in expansion and maintenance performance.

Owner:CHINA TOBACCO ZHEJIANG IND

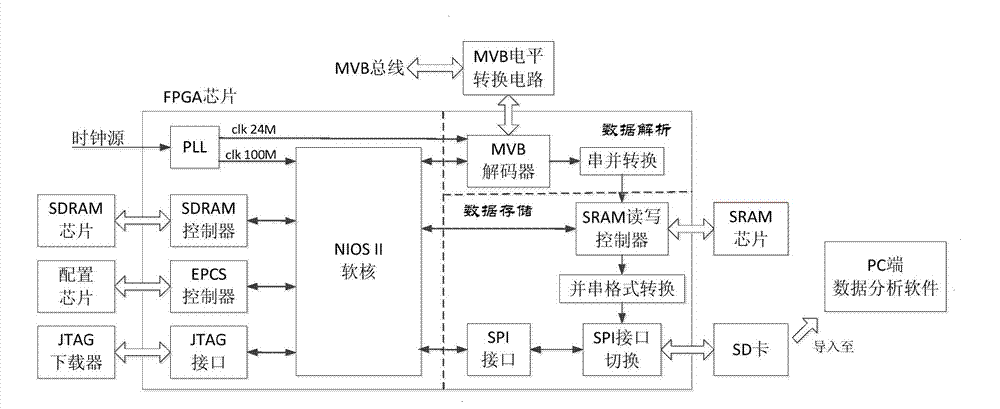

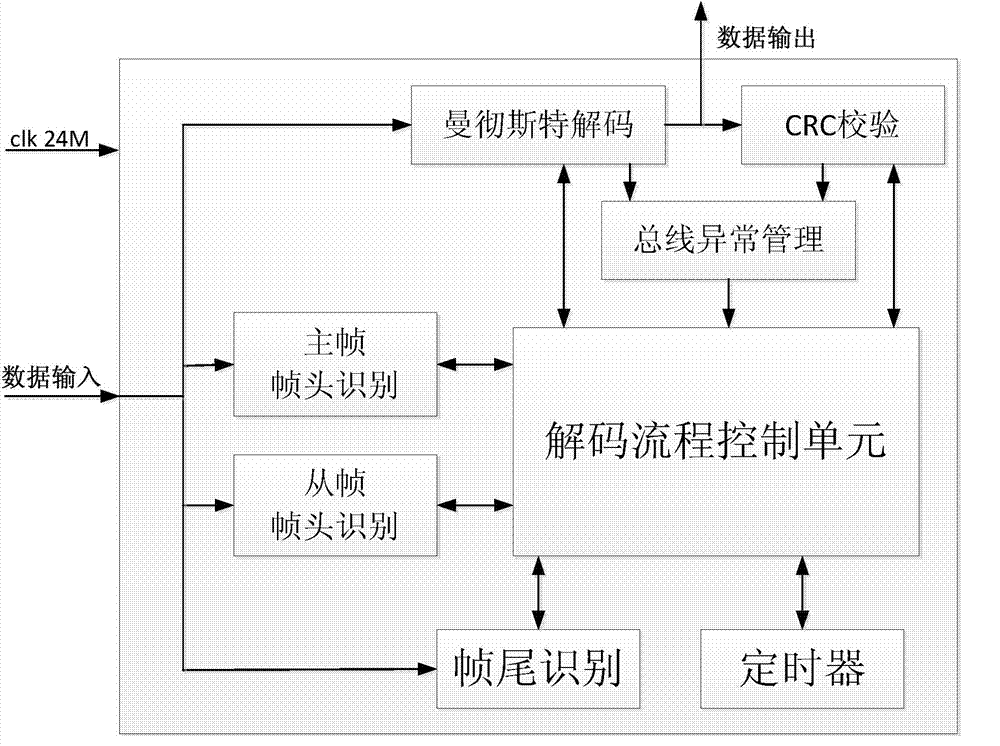

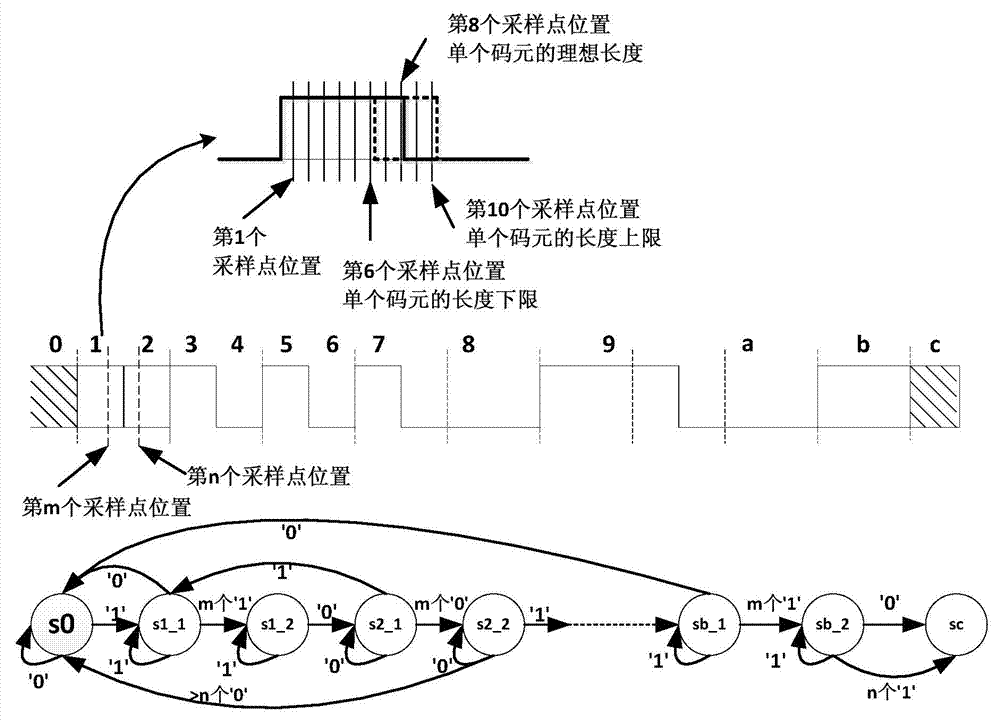

MVB (Multifunction Vehicle Bus) bus decoding and on-vehicle recording system based on SOPC technology

ActiveCN104282054AParsing is intuitiveImprove reliabilityRegistering/indicating working of vehiclesFrequency multiplierFpga chip

The invention relates to an MVB (Multifunction Vehicle Bus) bus decoding and on-vehicle recording system based on an SOPC technology. The system comprises an FPGA chip, an EPCS serial FLASH chip, an SDRAM chip, an SRAM chip, an SD card and an MVB level switching circuit, wherein the FPGA chip comprises an NIOS-II soft-core processor, a phase-locked loop frequency multiplier, an MVB decoder, an SRAM read / write controller, an SPI switching module and an SPI; the NIOS-II soft-core processor is connected with the EPCS serial FLASH chip, the SDRAM chip, the phase-locked loop frequency multiplier, the MVB decoder, the SRAM read / write controller and the SPI; the MVB decoder is connected with the phase-locked loop frequency multiplier, the MVB level switching circuit and the SRAM read / write controller; and the SPI switching module is connected with the SPI interface, the SRAM read / write controller and the SD card. Compared with the prior art, the MVB bus decoding and on-vehicle recording system disclosed by the invention has the advantages of software and hardware integration, high reliability, convenience in operation, high real-time property and the like.

Owner:SHANGHAI JIAO TONG UNIV

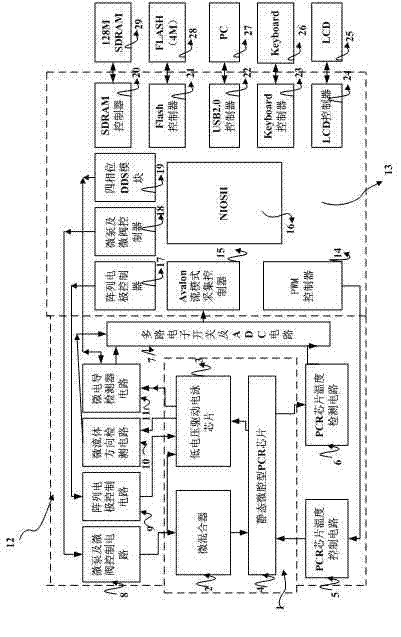

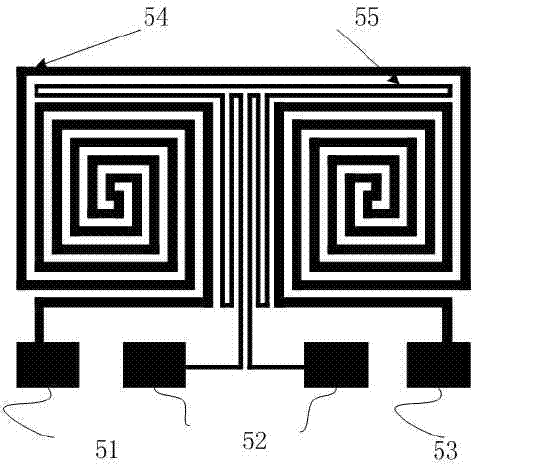

Chip level PCR-LVCE integrated system

InactiveCN103194383AReduce power consumptionHigh sensitivityBioreactor/fermenter combinationsBiological substance pretreatmentsTest sampleElectrophoresis

The invention discloses a chip level PCR-LVCE integrated system which comprises a chip level PCR-LVCE micro fluidic chip, a chip level PCR-LVCE detection and a control interface circuit as well as a chip level PCR-LVCE detection and control system based on an SOPC (system on programmable chip) technique; the integrated system achieves ionophortic separation and electrochemical detection of different components of to-be-measured test samples in NIOSII soft core processor control, to-be-analyzed test sample micro mixing of relevant interface circuit control, micro fluid liquid direction judgment in an LVCE chip and variation field intensity forming movements on an LVCE separation micro channel. The chip level PCR-LVCE integrated system provided by the invention has the advantages of rapidity, simplicity, convenience, high integrated degree and the like, can effectively improve the detection efficiency, are higher in expansibility, real-time property and safety compared with the prior art, and can be widely applied to the fields of biochemistry, medicine, environment, criminal investigation and the like.

Owner:HUBEI UNIV FOR NATITIES

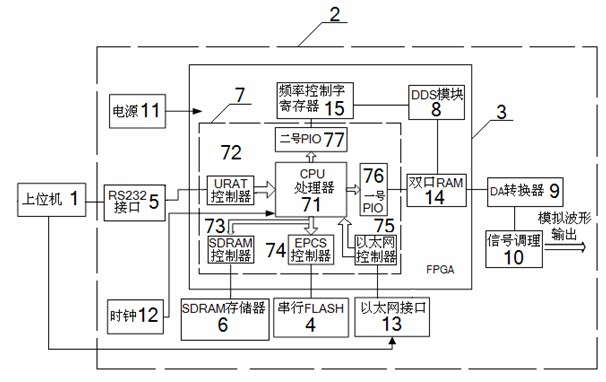

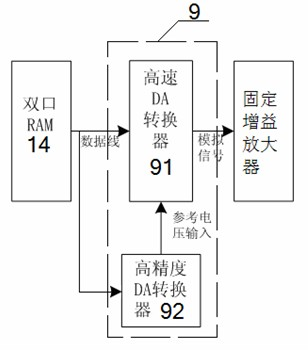

Hardware-in-the-loop generator and use method thereof

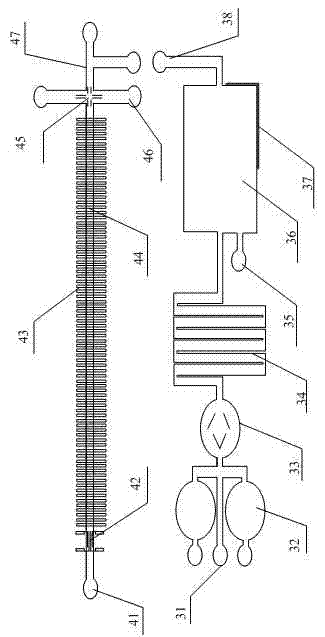

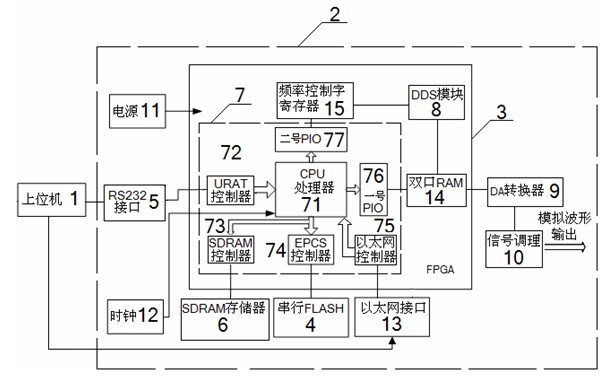

InactiveCN102426472AHigh precisionDirectly targetedSpecial data processing applicationsDigital function generatorsSignal conditioning circuitsRandom access memory

The invention discloses a hardware-in-the-loop generator which comprises a physical object part and a non-physical object part, wherein the non-physical object part is an upper computer loaded with waveform design simulation software; the physical object part is a lower computer; the lower computer comprises a D / A (Digital / Analogue) converter circuit, a signal conditioning circuit and an FPGA (Field Programmable Gate Array) chip in which an NiosII soft core processor is embedded; when the hardware-in-the-loop generator is in use, the non-physical object part can be used for calling an automatic mode by manual operation or program to set parameters of simulation waveform; if the displayed simulation waveform meets the requirement, module parameters are generated and transmitted to the lower computer and then are matched with an NiosII soft core processor and dual-port RAM (Random Access Memory) and DDS (Direct Digital Synthesizer) modules to transmit the processed digital signal to the D / A converter circuit; and finally, the processed digital signal is processed by the D / A converter circuit and the signal conditioning circuit to obtain a final signal. With the design, the hardware-in-the-loop generator disclosed by the invention has the advantages of higher precision, stronger intuitiveness, lower production cost, higher automatic degree and wide application range.

Owner:徐华中 +2

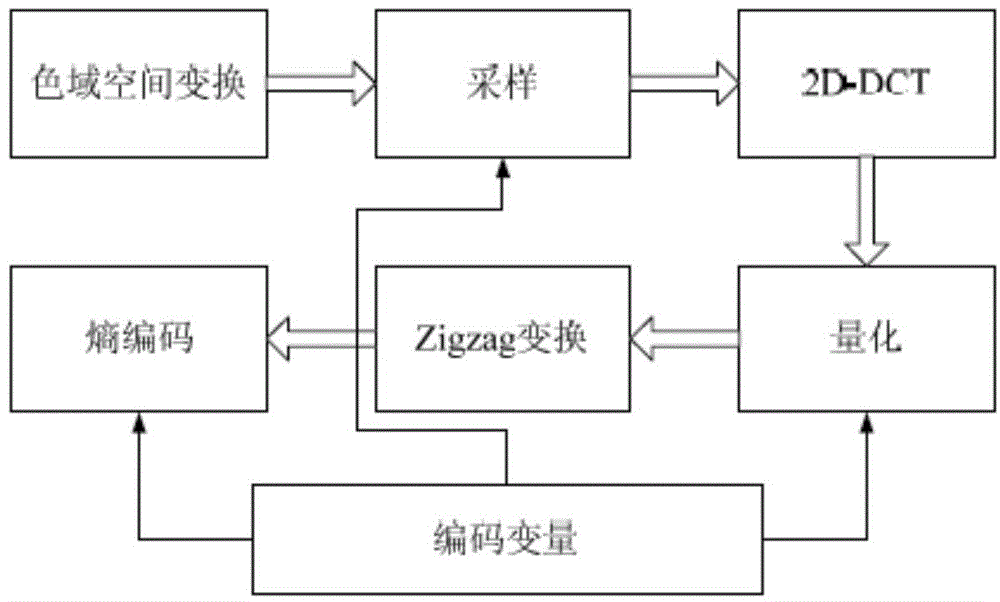

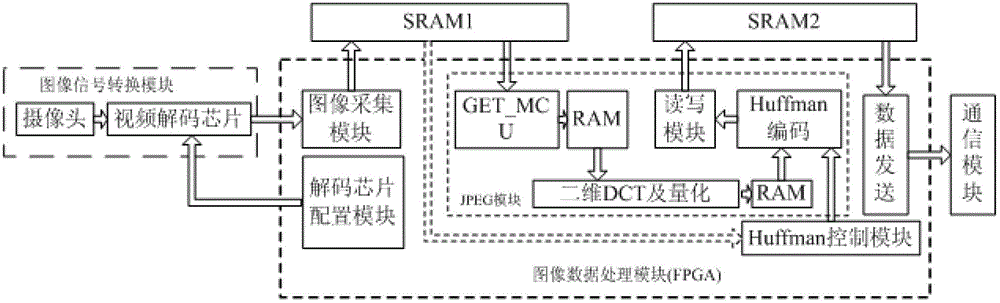

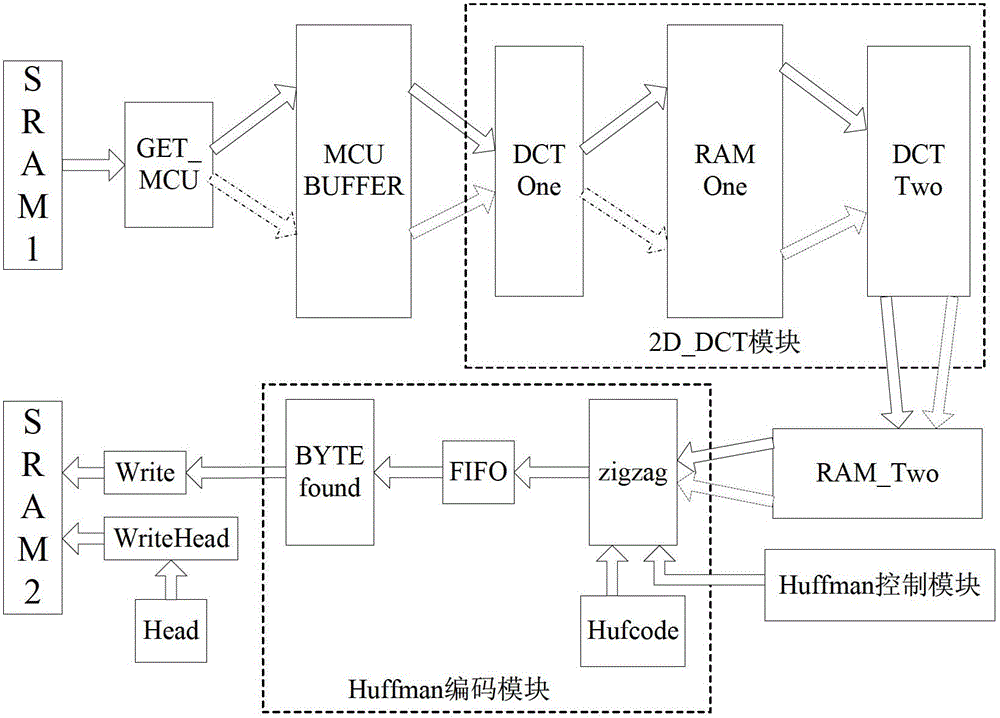

Variable-compression ratio image compression system and method based on FPGA

InactiveCN102724499AIncrease the compression ratioEasy to keepTelevision systemsDigital video signal modificationJPEGImaging data

The invention discloses a variable-compression ratio image compression system and an image compression method based on an FPGA (Field Programmable Gate Array), which are used for solving the technical problems of large consumption and bad transplantability of the existing image processing system. An image data processing module in the system adopts the FPGA as a core chip, so that the system has the advantages of high reliability and miniaturization; and the image compression method of the image compression system based on the FPGA comprises the following steps: parallelizing a JPEG (Joint Photographic Experts Group) algorithm, storing calculation results in the middle and used data into an RAM (Random Access Memory), an ROM (Read Only Memory) and an FIFO (First In First Out) composed of FPGA internal storage chips, so that a storage structure is optimized; optimizing DCT (Discrete Cosine Transform) to reduce the occupation of FPGA resources; and compressing an image at different compression ratios and better keeping information in an area of interest while the compression ratio is ensured. Any soft core processor or any hard core processor is not required to be embedded in the system, and occupies resources are less, so that the system is constructed through the low-terminal FPGA chip; and the system is high in cost performance and strong in transplantability.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

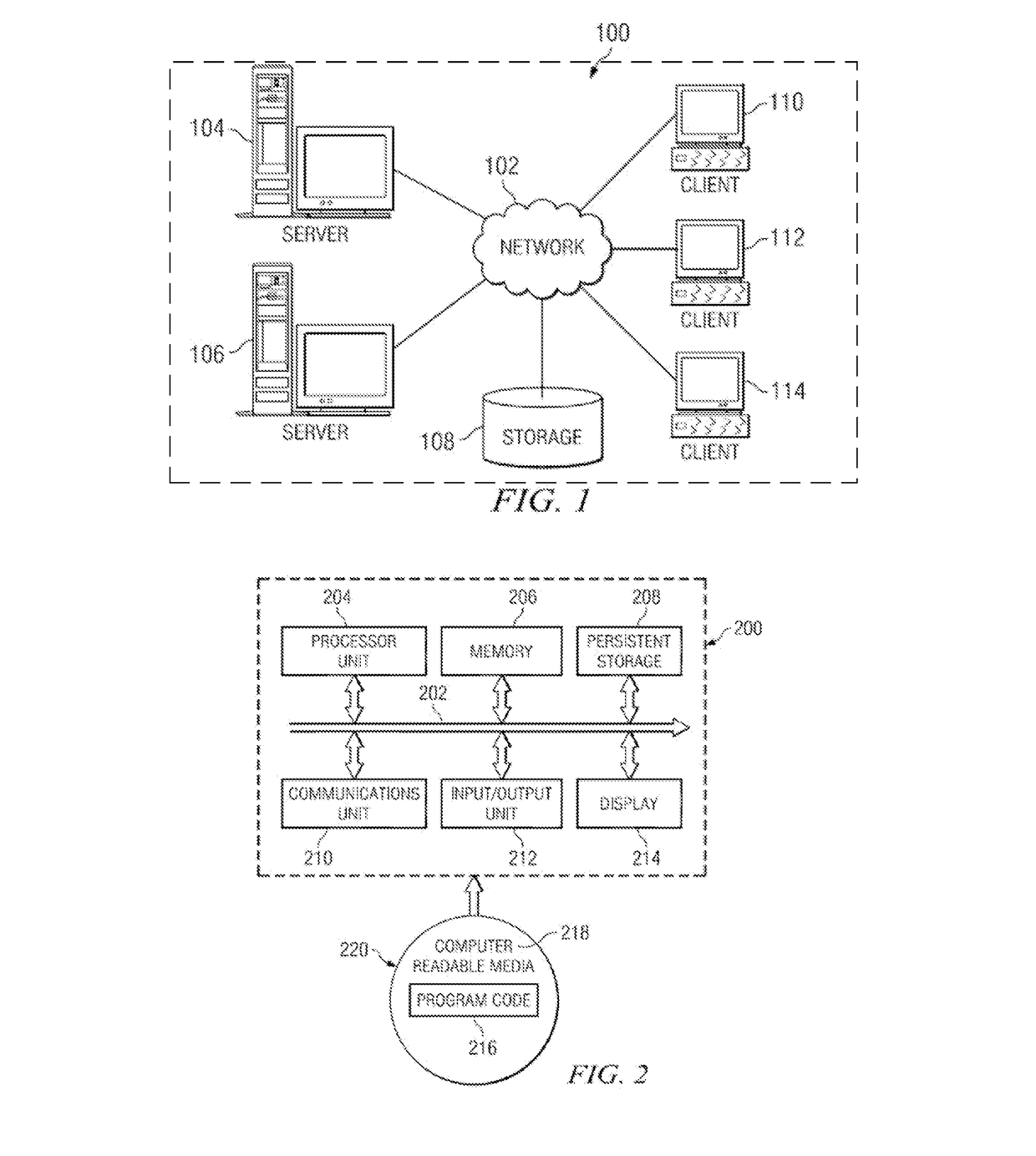

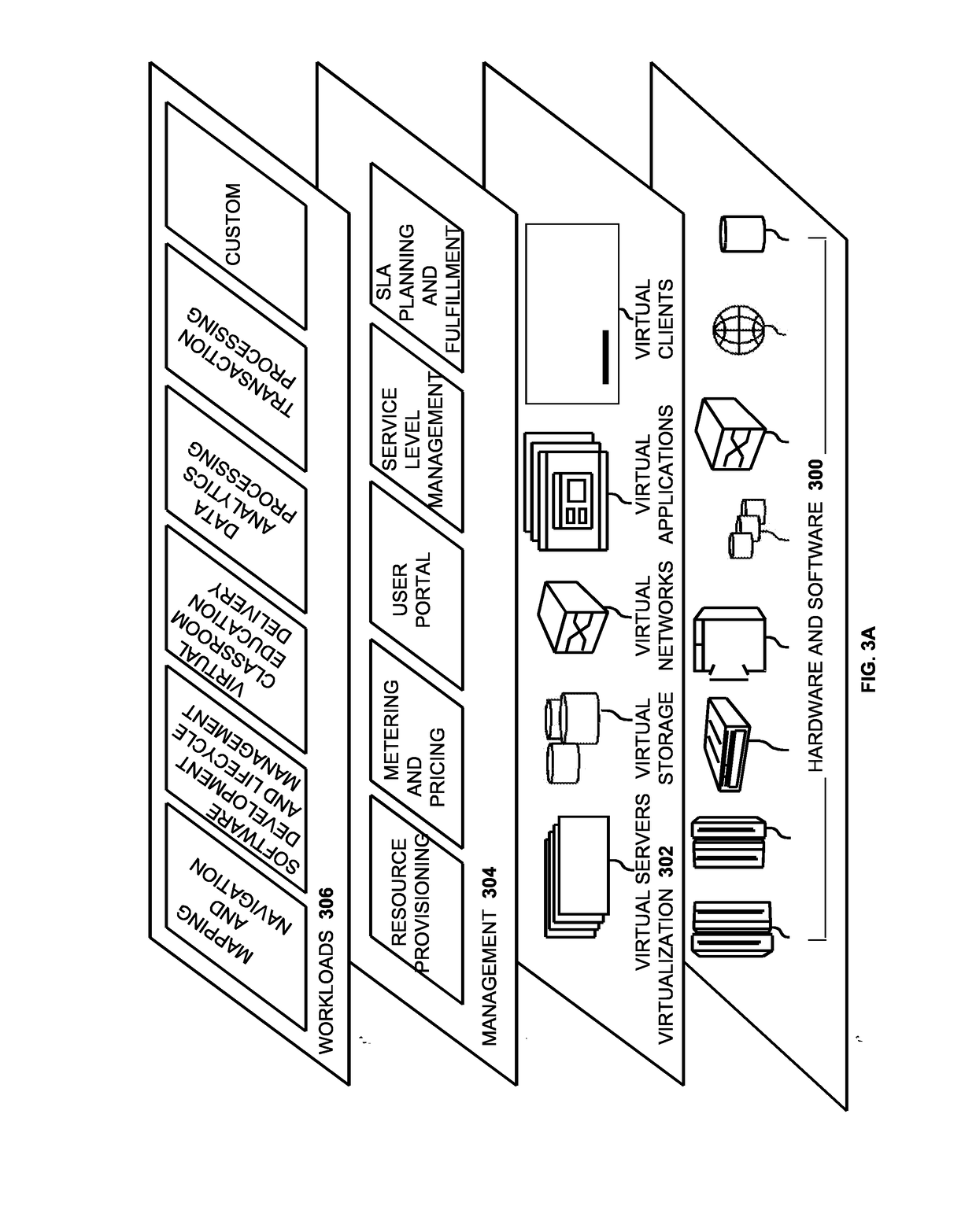

CPU obfuscation for cloud applications

ActiveUS20170091486A1Digital data protectionPlatform integrity maintainanceObfuscationDistributed Computing Environment

A cloud deployment system is used for obfuscating CPU operation codes in a set of machines operating in a distributed computing environment. A reprogrammable microcode replaces a hardware instruction set, the microcode layer containing a set of original operation codes. A first transform of the set of original operation codes produces a first set of transformed operation codes. A first transformed microcode is created which incorporates the first set of transformed operation codes instead of the original operation codes. An operating system and an application is compiled using the first set of transformed operation codes to produce a first cross compiled operating system and application. The first transformed microcode, the first cross compiled operating system and application are deployed to a respective first one of the set of machines, the first one of the machines equipped with a softcore processor.

Owner:IBM CORP

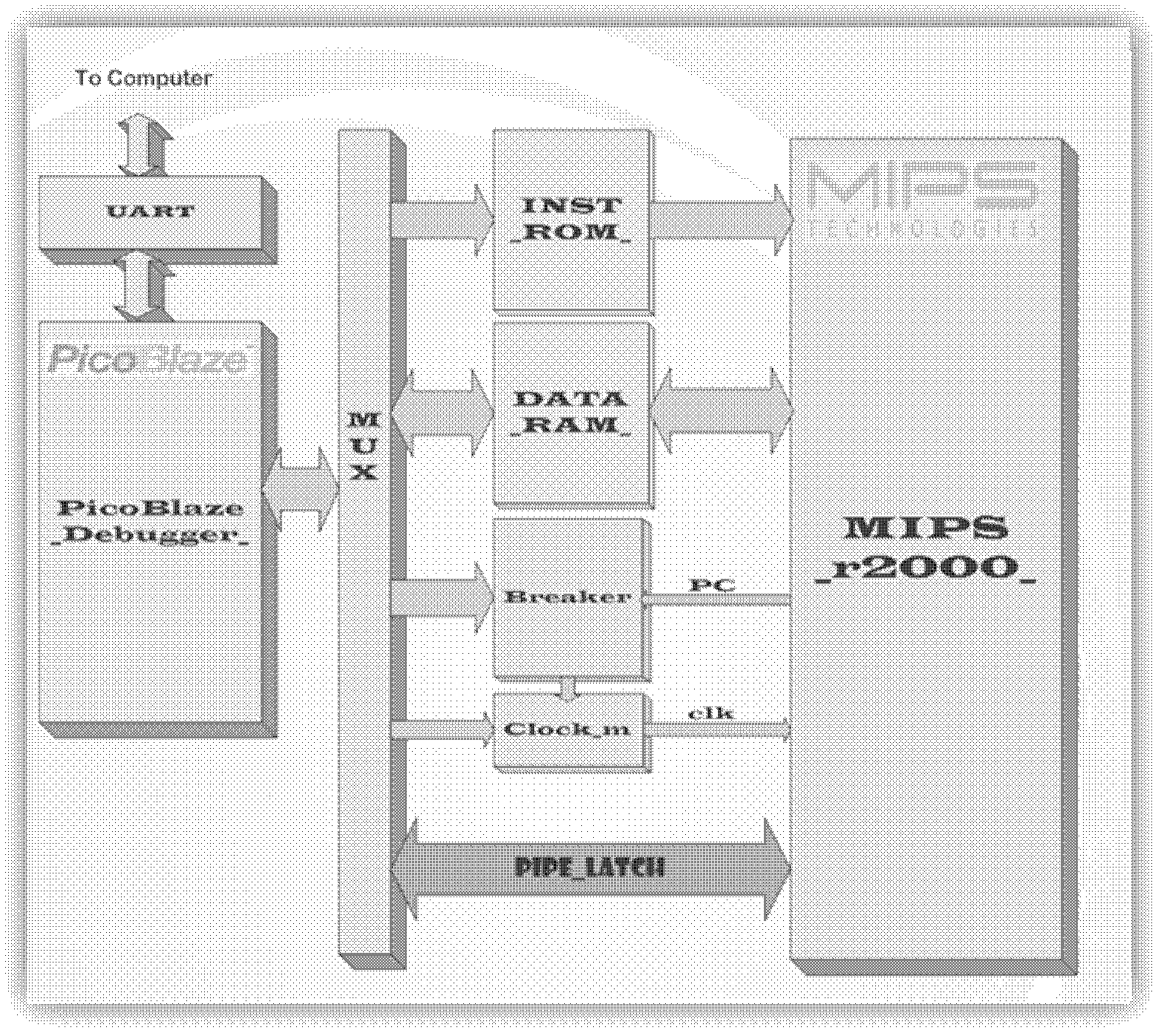

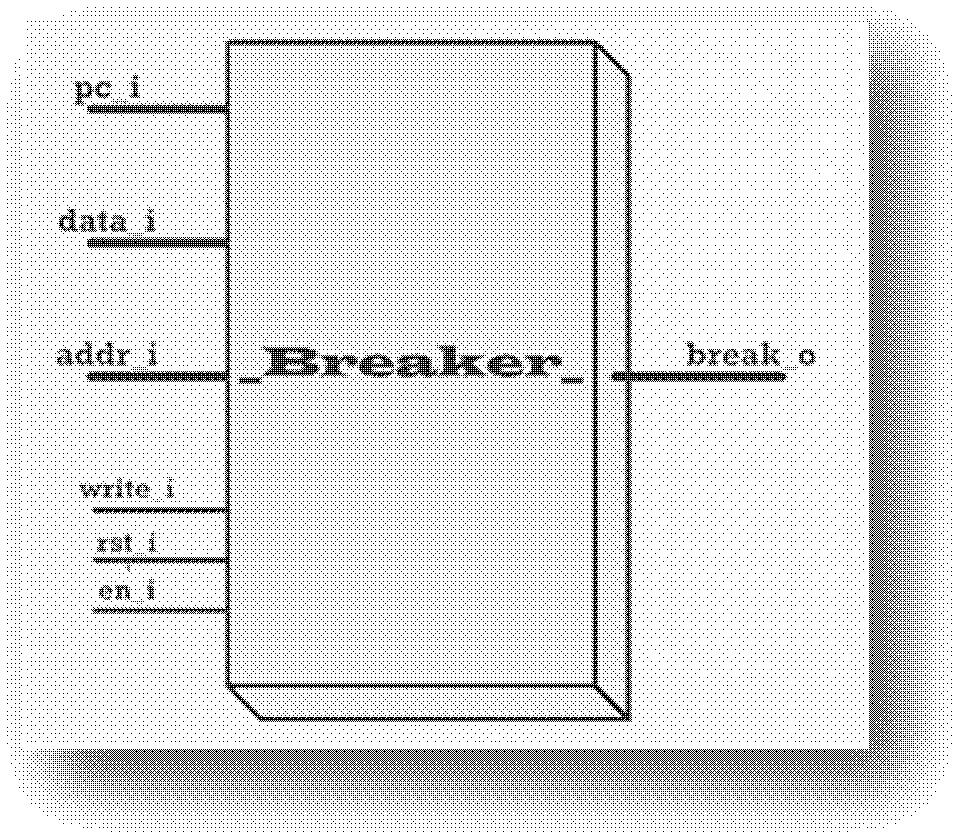

Field programmable gate array (FPGA) logic module debugging and data acquisition method based on PicoBlaze embedded soft core processor

The invention provides a field programmable gate array (FPGA) logic module debugging and data acquisition method based on a PicoBlaze embedded soft core processor. The PicoBlaze embedded soft core processor, a universal asynchronous receiver / transmitter (Uart) module, a clock control module and a double-port random access memory (RAM) module are arranged in engineering of a hardware system, and corresponding software is installed on a personal computer (PC); a set of dedicated communication protocol is made, defines a uniform data packet format, is used for standardizing data exchange between the PicoBlaze processor and the PC, has a 8-bit cyclic redundancy check (CRC) function, and ensures communication reliability; and the hardware system on an FPGA is comprehensively debugged and all internal data is acquired and analyzed by sending a command at a PC end.

Owner:NAT UNIV OF DEFENSE TECH

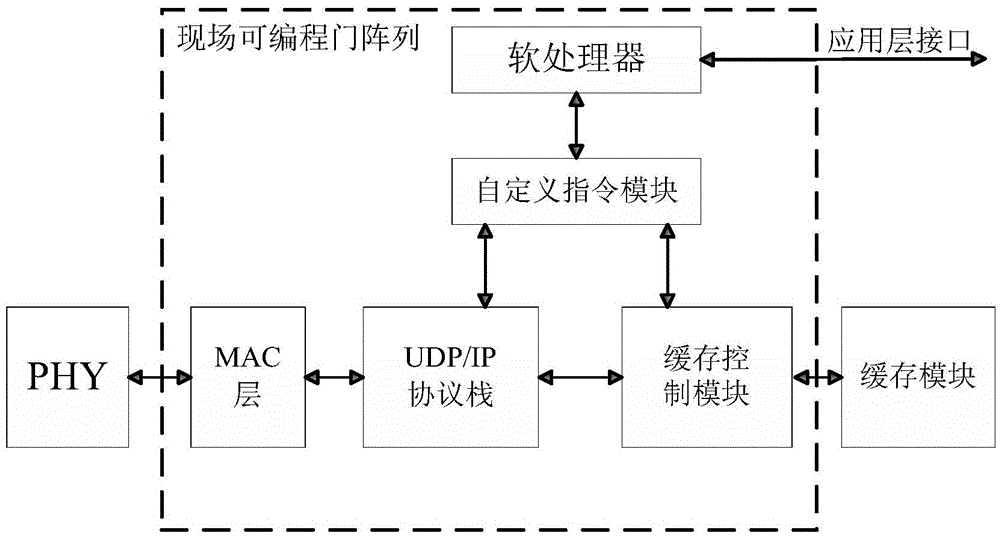

System and method for UDP high speed data transceiving

ActiveCN105471852AAvoid restrictionsImprove network throughputTransmissionComputer hardwarePhysical layer

Owner:WUHAN JINGCE ELECTRONICS GRP CO LTD

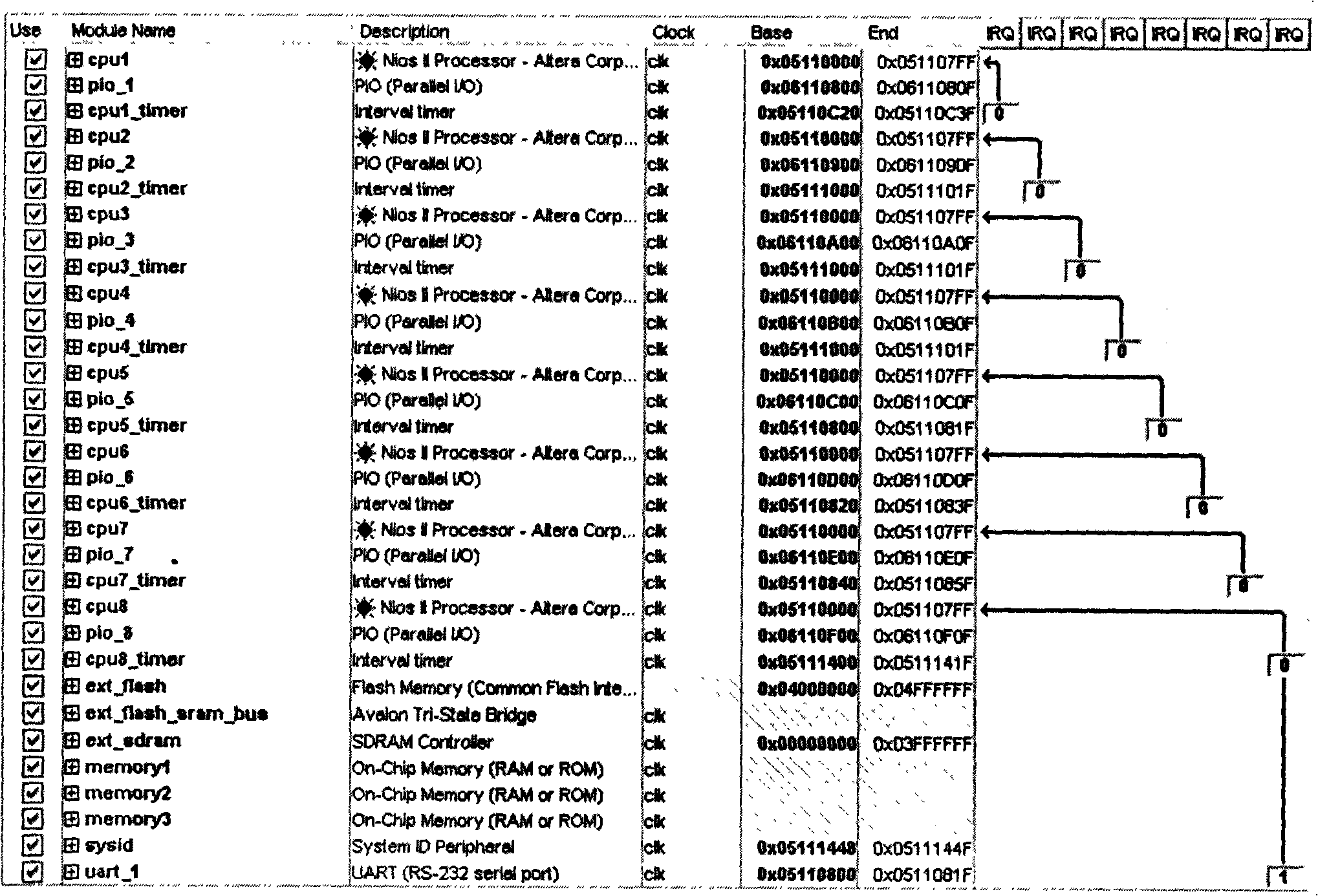

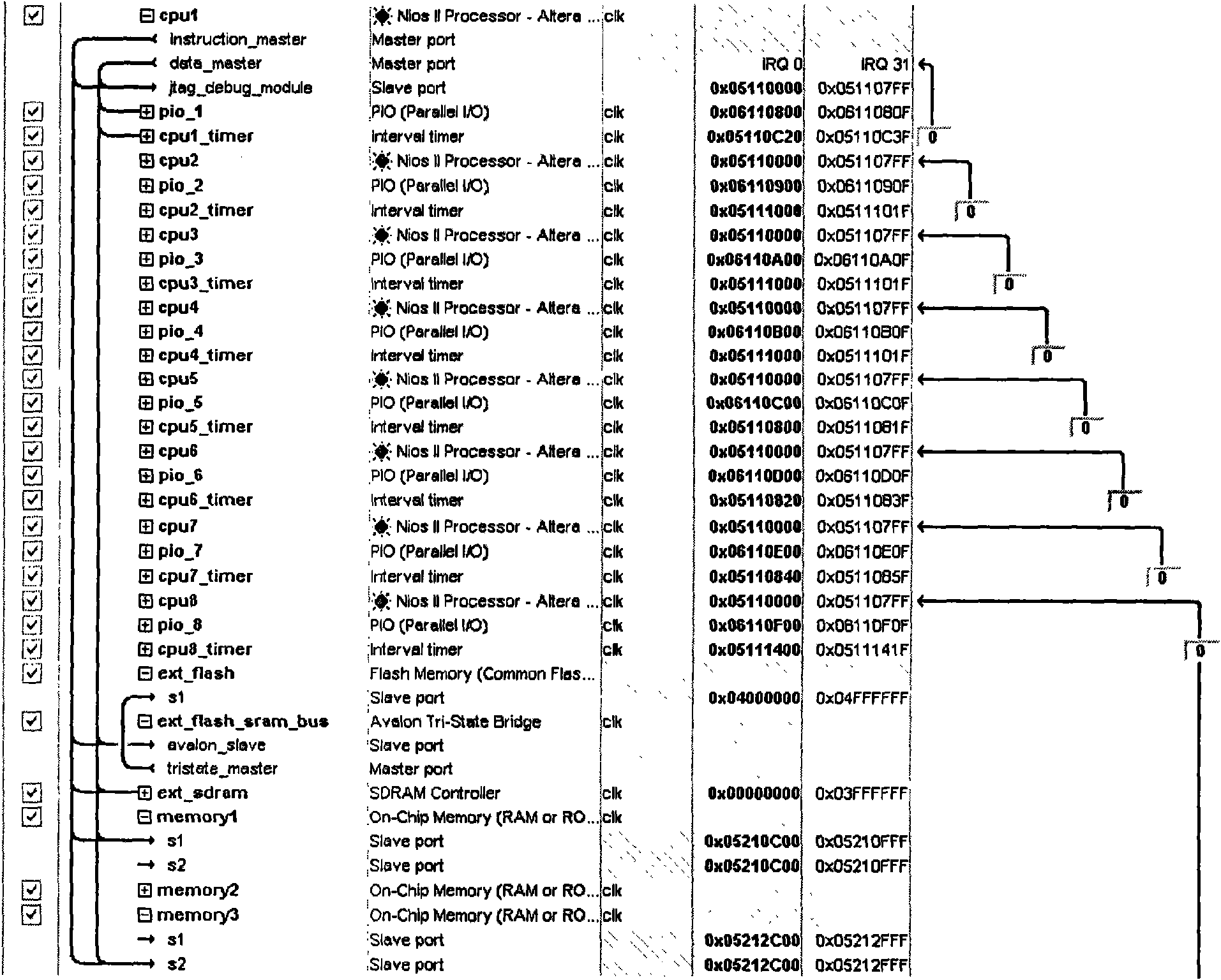

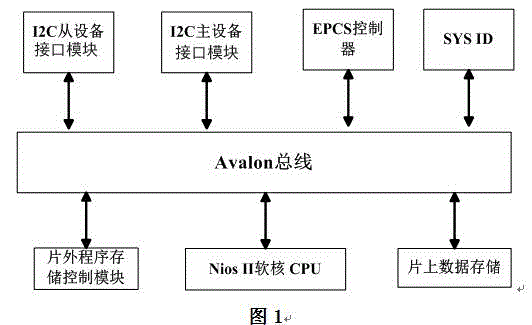

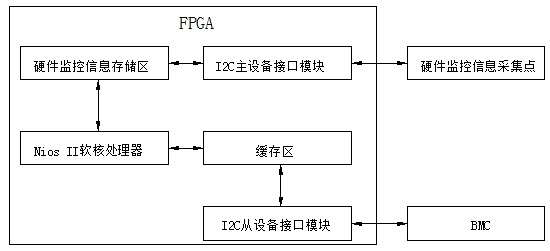

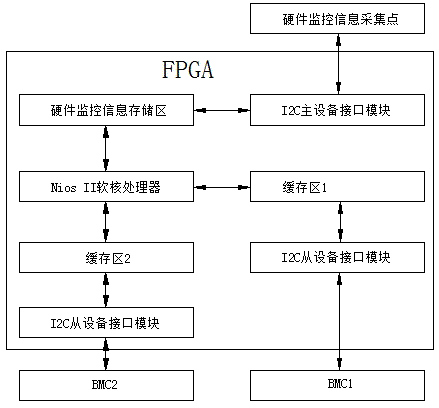

Method for acquiring monitoring information of computer system structure based on NUMA (Non Uniform Memory Access)

The invention discloses a method for acquiring monitoring information of a computer system structure based on NUMA (Non Uniform Memory Access). The method comprises the following steps: constructing an interface function module of a Nios II soft-core processor by utilizing FPGA programmable logic resources and an IP soft core; constructing a Nios II soft-core system by using Qsys in Quartus II software, and adding the Nios II soft-core processor, an I2C master equipment interface module, an I2C slave equipment interface module and other IP cores; acquiring the monitoring information through the I2C master equipment interface module, processing the monitoring information by virtue of the Nios II soft-core processor, and transmitting the processed information to the I2C slave equipment interface module; and accessing the I2C slave equipment interface module to acquire hardware monitoring information by using BMC. According to the method, the hardware monitoring information of the system is acquired in a unified mode by virtue of the FPGA, the integration level of the system is improved, and the design of an external hardware circuit is simplified; and moreover, the hardware information can be independently monitored without influence by the BMC under the multiple physical layer partitions in the system, and the stability and real-time property of the system are improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD