Bipolar organic field effect transistor

A bipolar, organic field technology, used in electrical components, electrical solid state devices, semiconductor/solid state device manufacturing, etc., can solve the problem of low carrier mobility, insufficient exciton dissociation, and hindering organic bipolar field effects. Management of commercial prospects and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

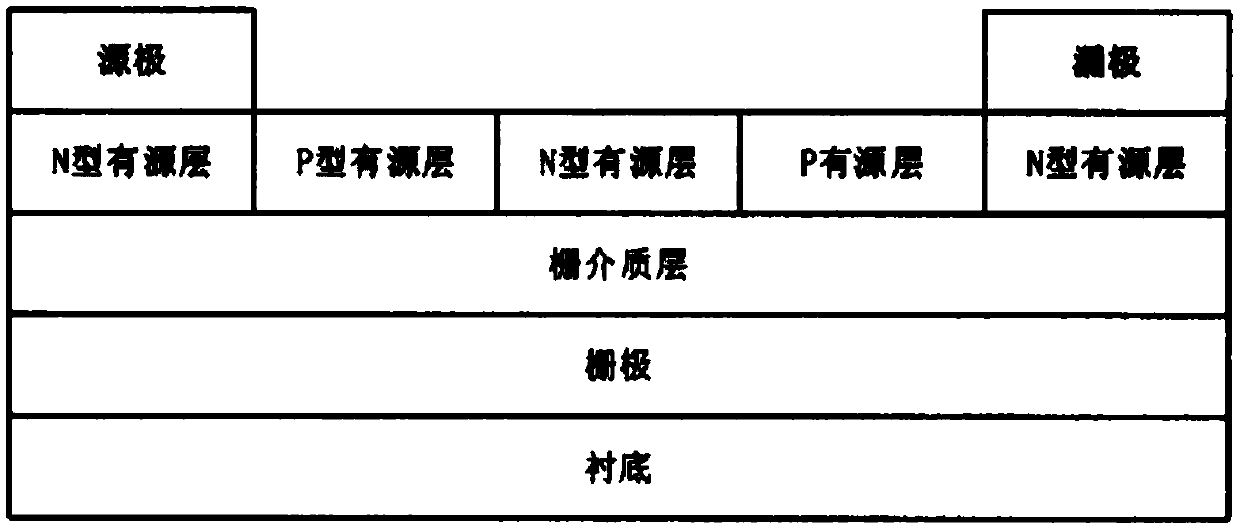

Embodiment 1

[0010] The present invention uses heavily doped n+-Si / SiO2 as the gate / gate dielectric layer and double as the substrate, C60 as the N-type active layer, pentacene as the P-type active layer, and adopts the bottom-gate bottom-contact structure The preparation process is as follows:

[0011] 1) Clean the n+-Si / SiO2 substrate with a standard process;

[0012] 2) Prepare 3 layers of C60 arranged at intervals on the n+-Si / SiO2 substrate by photolithography as the N-type active layer;

[0013] 3) Prepare two layers of pentacene in the gap between the three layers of N-type active layers by photolithography as the P-type active layer;

[0014] 4) Prepare a metal film (such as gold) on the N-type active layer and P-type active layer arranged side by side by vacuum evaporation as the source and drain electrodes, and the channel length and electrode area are limited by the mask;

[0015] 5) Packaging the manufactured device.

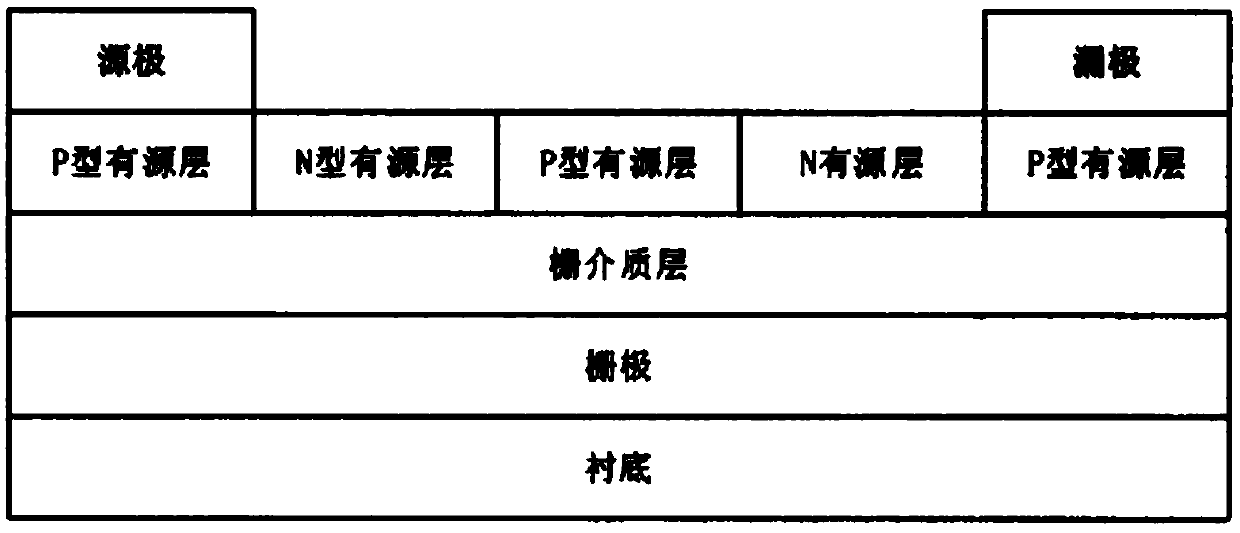

Embodiment 2

[0017] The present invention uses heavily doped n+-Si / SiO2 as the gate / gate dielectric layer and double as the substrate, C60 as the N-type active layer, pentacene as the P-type active layer, and adopts the bottom-gate bottom-contact structure The preparation process is as follows:

[0018] 1) Clean the n+-Si / SiO2 substrate with a standard process;

[0019] 2) Prepare 3-layer spaced pentacene on n+-Si / SiO2 substrate by photolithography as P-type active layer;

[0020] 3) Prepare 2 layers of C60 as the N-type active layer in the gap between the 3-layer P-type active layer by photolithography;

[0021] 4) Prepare a metal thin film (such as gold) on the P-type active layer and N-type active layer arranged side by side by vacuum evaporation as the source and drain electrodes, and the channel length and electrode area are limited by the mask;

[0022] 5) Packaging the manufactured device.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More