LDMOS device and manufacturing method thereof

A device manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as large impact of process fluctuations, and achieve the goals of avoiding process fluctuations, low on-resistance, and improving withstand voltage Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

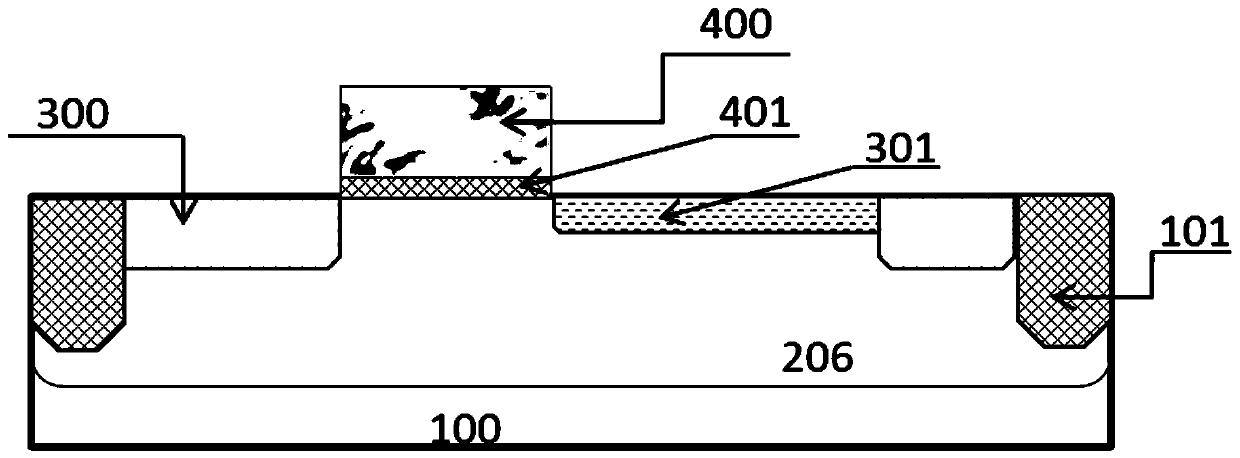

[0061] Such as Figure 4 As shown, the LDMOS device includes a first type well 206 formed on a silicon substrate 100;

[0062] A second type surface drift region 301, a drain terminal and a source terminal 300 are formed laterally of the first type well 206;

[0063] The surface drift region 301 is between the drain end and the source end 300, the surface drift region 301 is adjacent to the drain end, and is separated from the source end 300;

[0064] A silicon dioxide layer is formed above the surface drift region 301, and a silicon dioxide layer is formed above the interval between the homologous ends of the surface drift region 301;

[0065] The silicon dioxide layer directly above the surface drift region 301 is covered with an ONO film layer 402;

[0066] A polysilicon gate 400 is formed on the silicon dioxide layer above the interval between the ONO film layer 402 and the homologous end of the N-type surface drift region 301 .

[0067] Preferably, the depth of the sur...

Embodiment 2

[0074] The manufacturing method of the LDMOS device of embodiment one, comprises the following steps:

[0075] 1. Forming a pad silicon dioxide layer 403 on the silicon substrate 100;

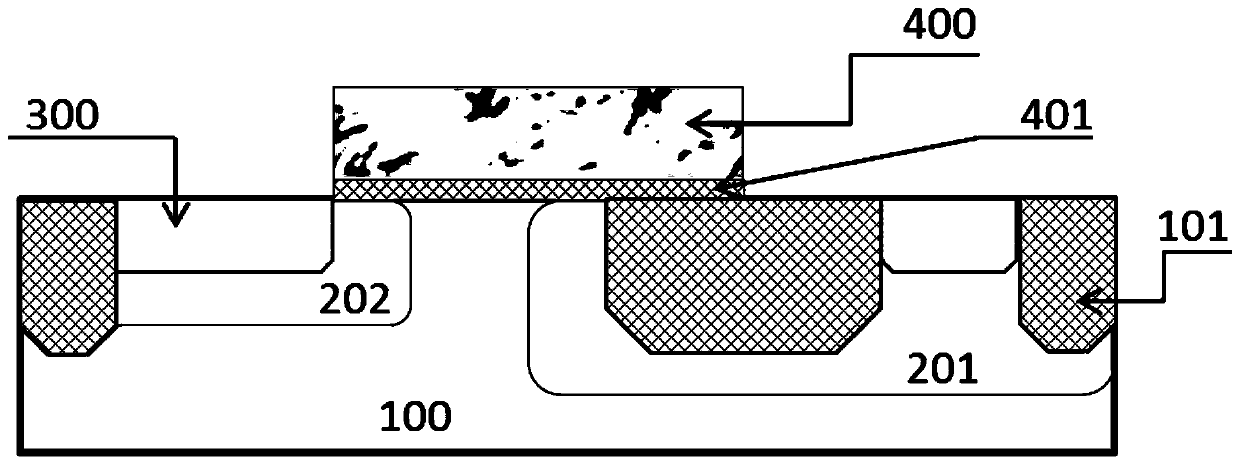

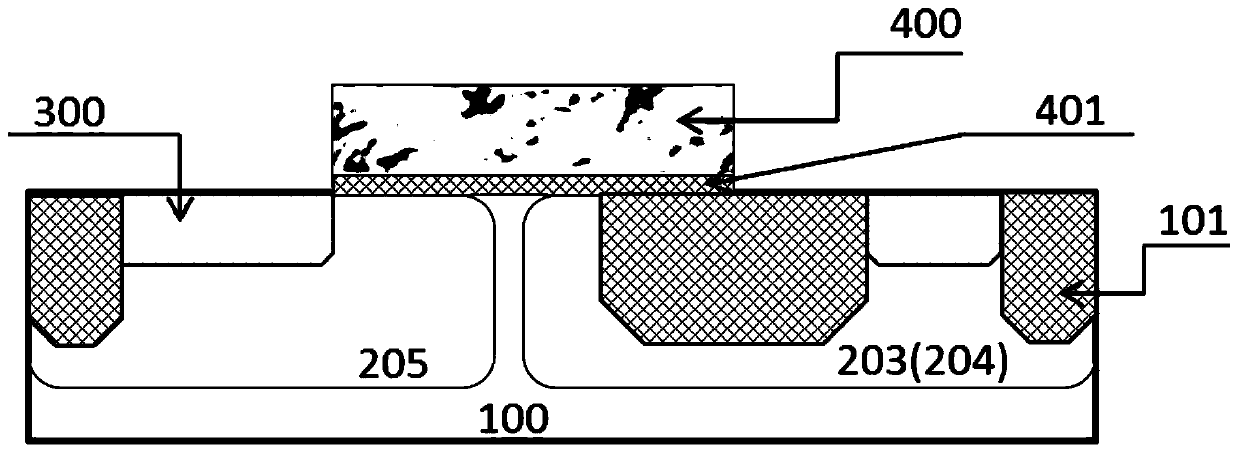

[0076] 2. On the silicon substrate 100, a shallow trench isolation region 101 is formed, such as Figure 5 shown;

[0077] 3. On the right part of the silicon substrate 100 adjacent to the two shallow trench isolation regions 101, the surface drift region 301 is formed by photolithography and ion implantation through the pad silicon dioxide layer 403, and the surface drift region 301 shallower than the shallow trench isolation region 101, such as Figure 6 shown;

[0078] 4. Forming a first type well 206 on the entire upper part of the silicon substrate between two adjacent shallow trench isolation regions 101, the depth of the first type well 206 is not less than the depth of the shallow trench isolation region 101;

[0079] Five. Form ONO (silicon dioxide / silicon nitride / silicon dioxide) ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More