A planar gate igbt device with deep trench electric field shielding structure

A technology of electric field shielding and planar gate, which is applied in the direction of electrical components, semiconductor devices, circuits, etc., can solve the problems of excessive gate drive charge, small short-circuit safe working area, and limited concentration of CSL layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

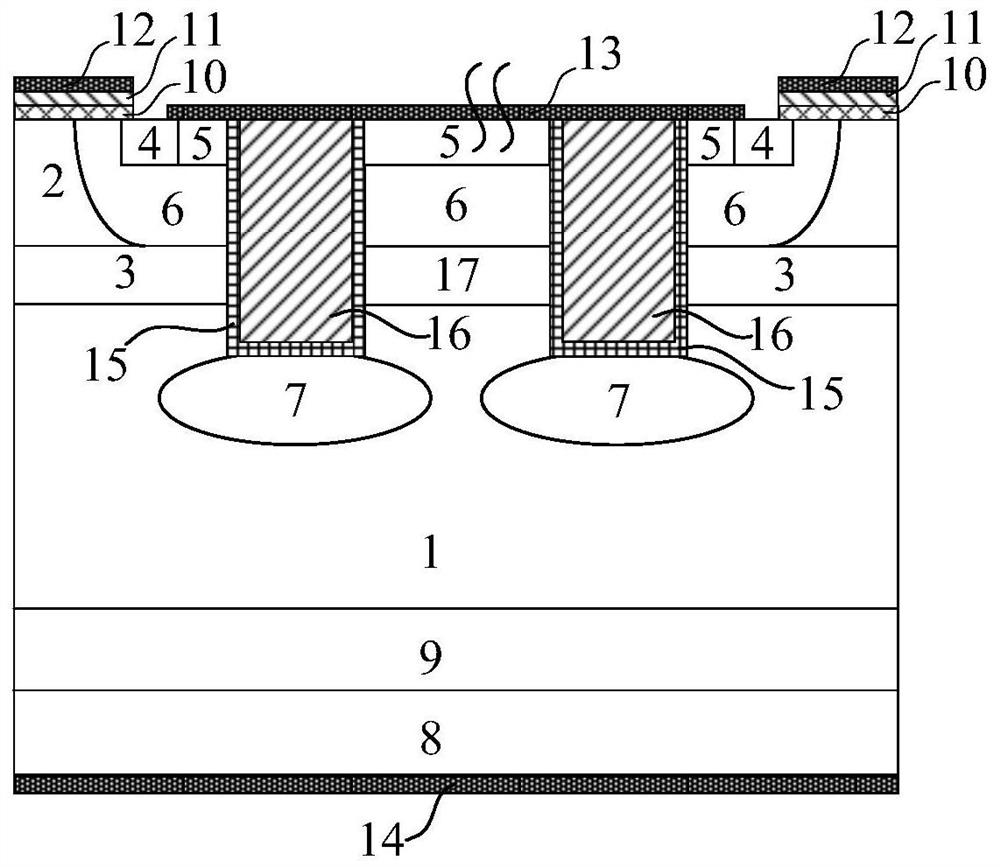

[0030] This embodiment provides a planar gate IGBT device with a carrier storage layer, the cell structure of which is as follows figure 1 as shown,

[0031] N-type lightly doped region 1 as a withstand voltage region;

[0032] An N-type carrier storage layer 3 disposed on the withstand voltage region 1;

[0033] The N-type JFET region 2 disposed on the N-type carrier storage layer 3 and the P-type base region 6 adjacent thereto;

[0034] N arranged in the base region 6 as the cathode source region + Type heavily doped region 4 and P as the body contact region + heavily doped region 5;

[0035] A plurality of deep grooves with the same structure deep into the voltage-resistant region 1 arranged on the upper surface of the semiconductor region, the deep grooves penetrate through the body contact region 5, the P-type base region 6 and the N-type carrier storage layer 3, and The N-type carrier storage layer 3 between the deep grooves is replaced by an N-type semiconductor r...

Embodiment 2

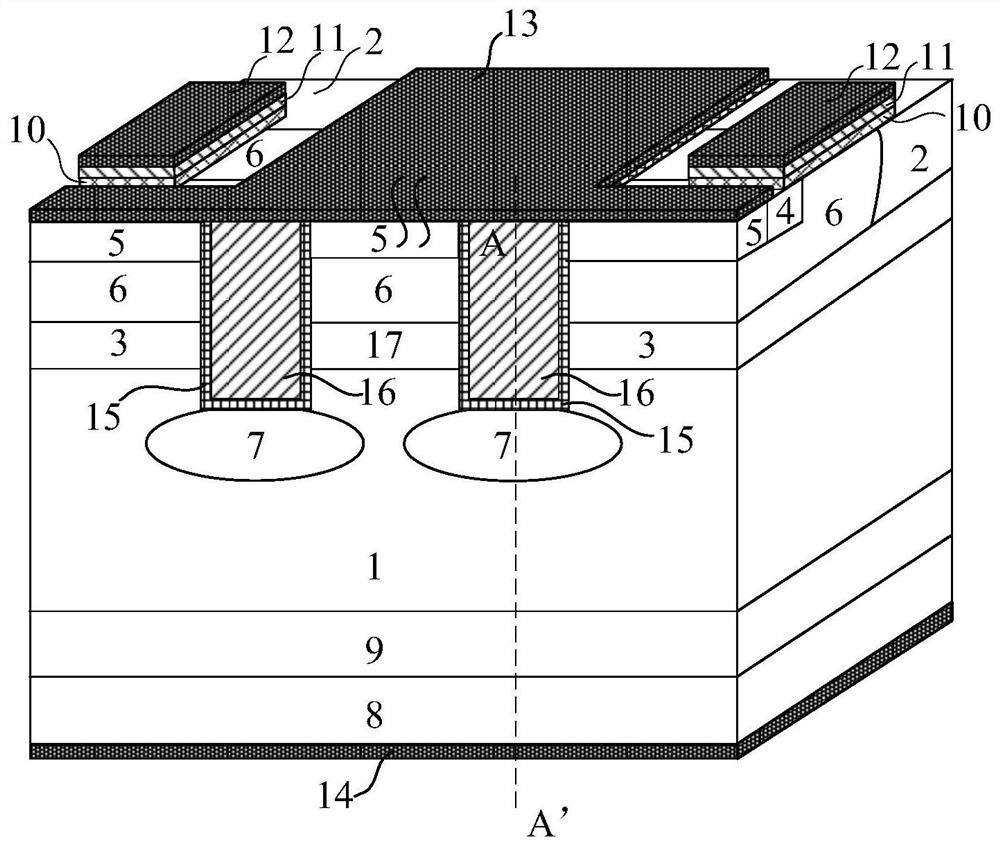

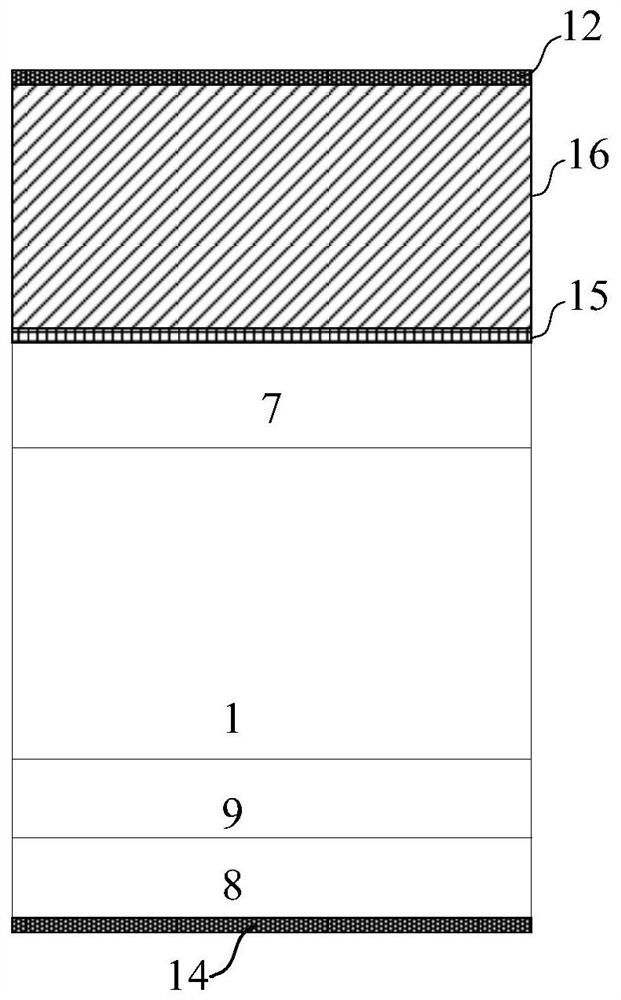

[0043] This embodiment provides a planar gate IGBT device with a carrier storage layer, the cell structure of which is as follows figure 2 As shown, the schematic diagram of the cut plane along AA' is as follows image 3 shown;

[0044] It differs from Embodiment 1 in that the direction of the channel current is parallel or approximately parallel to the sidewall of the deep trench.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More