A clock tree trunk topology generation method and system capable of perceiving integrated circuit layout information

A layout information, integrated circuit technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of low efficiency, affecting the progress of the whole chip clock tree design, etc., to achieve fast placement, coupling capacitance Low, the effect of ensuring the transmission quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention discloses a clock tree trunk topology generation method and system for perceiving integrated circuit layout information. In order to have a better understanding of the above and other aspects of the present invention, the specific implementation of the present invention will be further described below in combination with preferred embodiments. Detailed description.

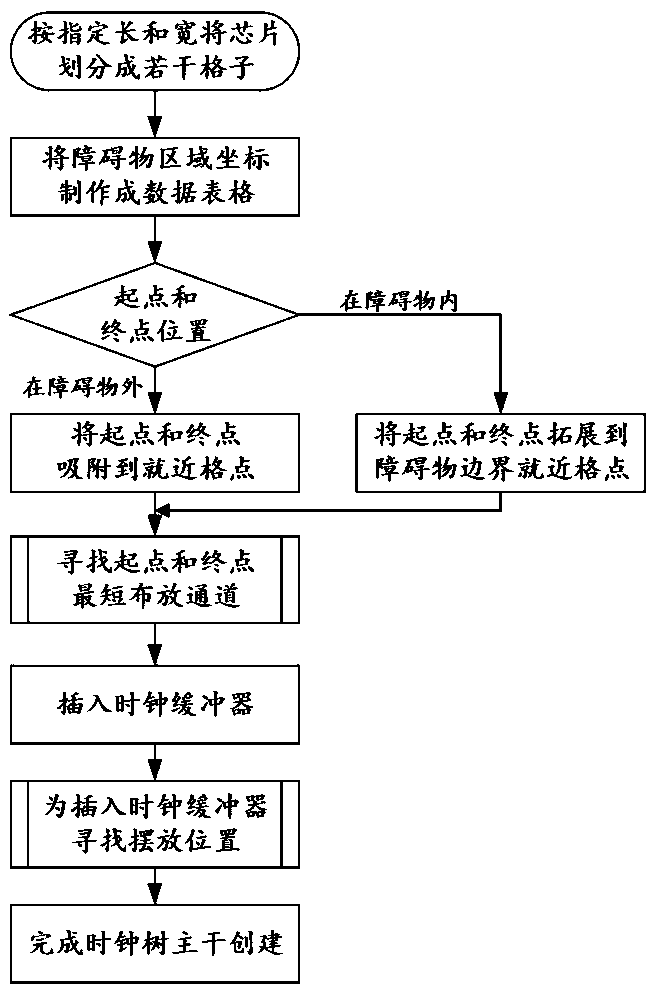

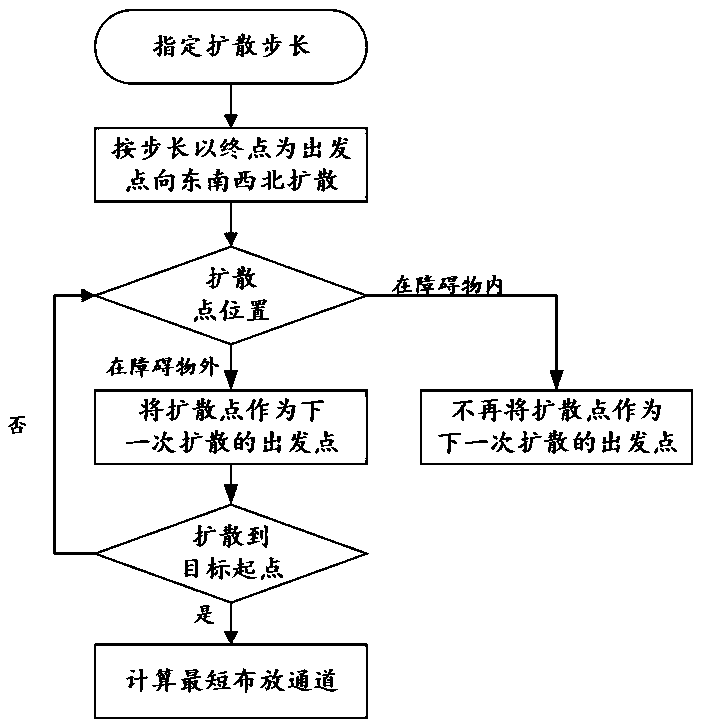

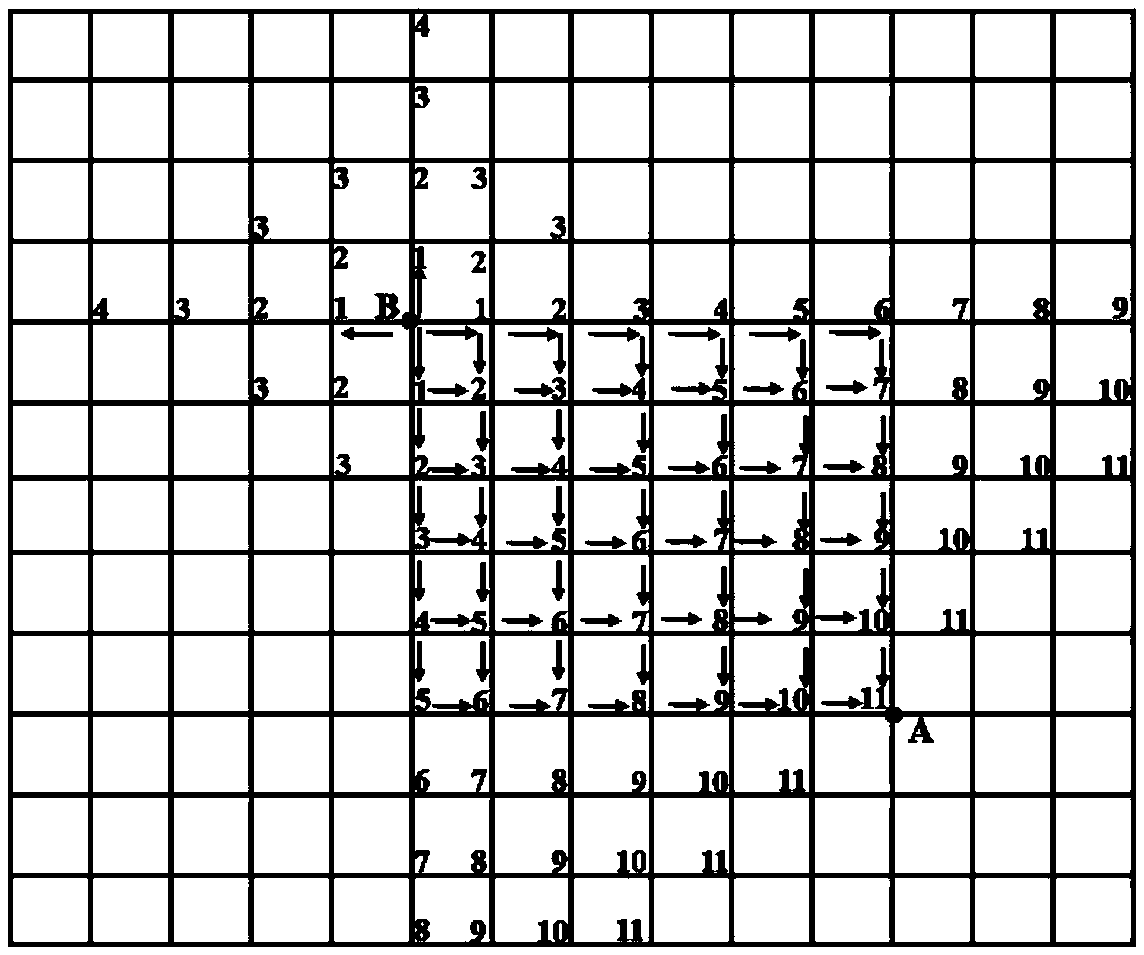

[0042] Such as figure 1 In this embodiment, the implementation steps of the clock tree trunk topology generation method perceiving integrated circuit layout information include:

[0043] 1) Divide the whole chip layout into several grids;

[0044] 2) Find out the obstacle location area in the whole chip (including forbidden area and block circuit);

[0045]3) Judging the positional relationship between the target point and the obstacle position area, if the target point is not in the obstacle position area, then the starting point and end point coordinates are adsorbed to the grid in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More