Method for simultaneously preparing enhanced and depletion gate devices and device

An enhanced and depleted technology, used in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., can solve the problems of poor electrical performance and high process cost, reduce metal evaporation, improve quality, avoid The effect of exposure and time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

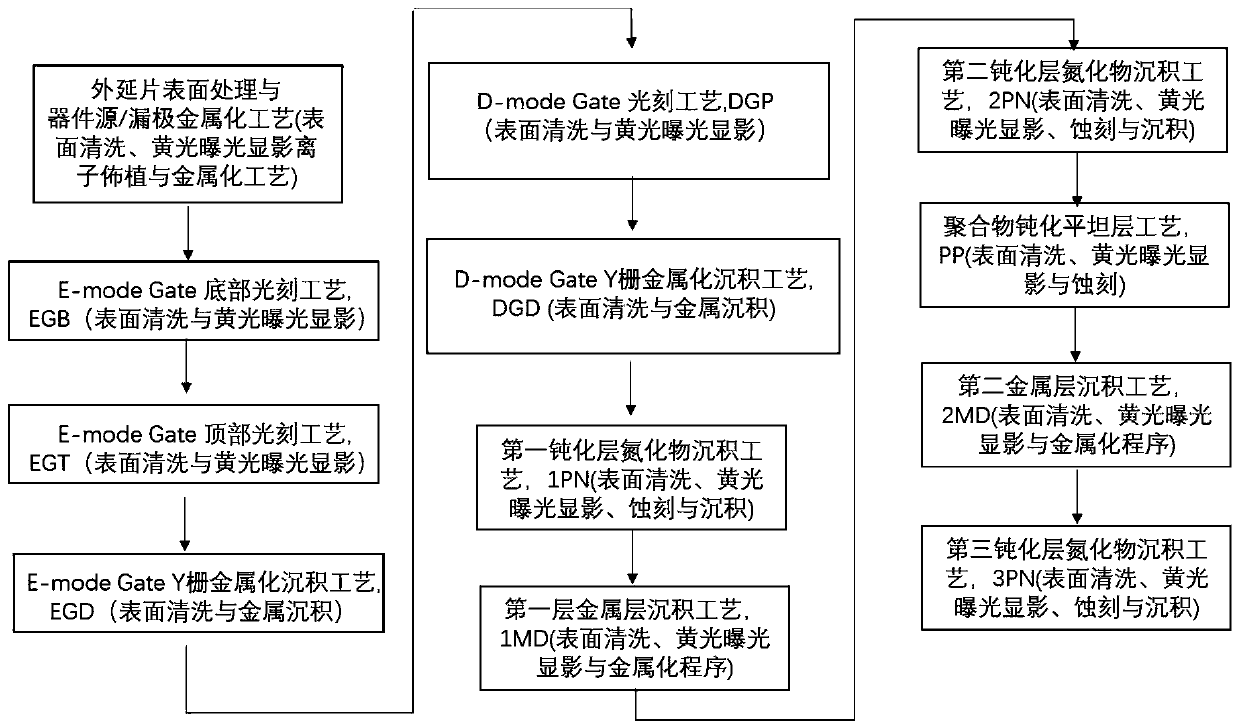

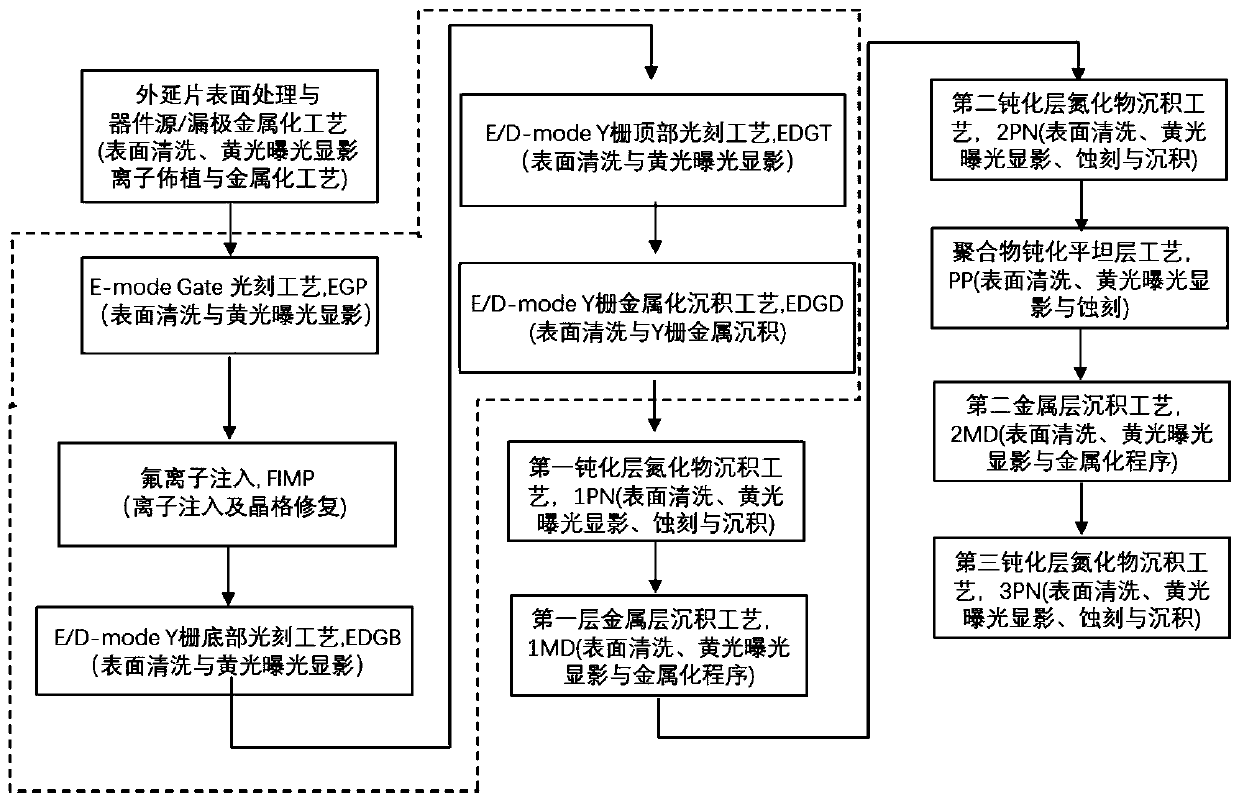

[0038] In order to explain in detail the technical content, structural features, achieved goals and effects of the technical solution, the following will be described in detail in conjunction with specific embodiments and accompanying drawings. The English abbreviations that may appear in the instructions and drawings of the instructions are first explained as follows:

[0039] 1. EGB: E-modeGate Bottom, enhanced device bottom photolithography process.

[0040] 2.EGT: E-modeGate Top, enhanced device top photolithography process.

[0041] 3.EGD: E-modeGate Deposition, enhanced device metallization deposition process.

[0042] 4.DGP: D-ModeGatePhoto, depletion device lithography process.

[0043] 5. DGD: D-modeGateDeposition, depletion device metallization deposition process.

[0044] 6.1PN: 1st Passivation Nitride, the first passivation layer nitride deposition process.

[0045] 7.1MD: 1st Metal Deposition, the first metal layer deposition process.

[0046] 8.2PN: 2nd Pass...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More