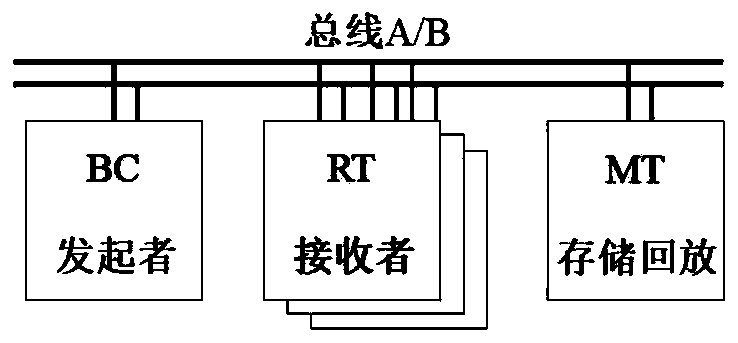

1553B bus IP core and monitoring system

A bus monitoring and bus technology, applied in the field of satellite electronics applications, can solve the problems of high power consumption, frequent CPU interaction, unfavorable equipment board transplantation, etc., and achieve the effect of low power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

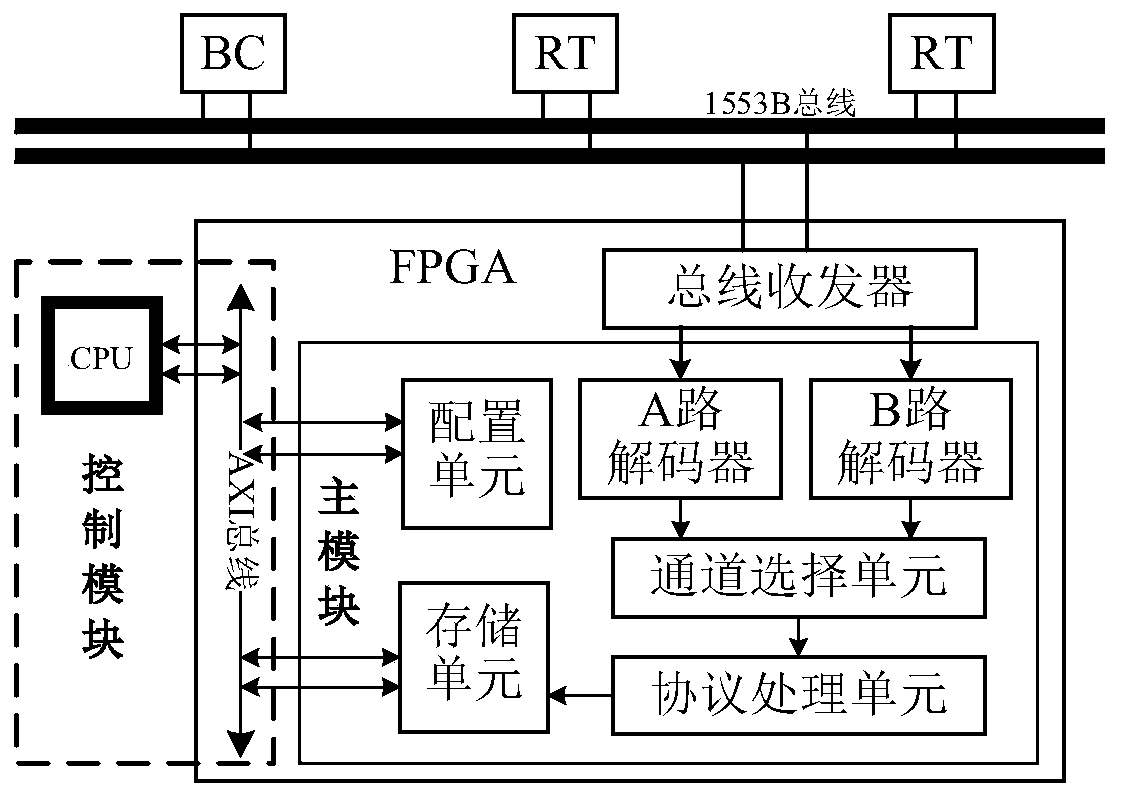

[0049] Implementation 1 of the present invention proposes a 1553B bus IP core, including a main module; the main module can work independently, and can flexibly be attached to multiple on-chip bus protocols. The present invention provides a design process for the AXI on-chip bus, which is convenient for final testing And other bus-controlled migration applications. The main module implements the function of 1553B filtering and monitoring, packs and stores the received information, and provides a message output interface and a message control interface.

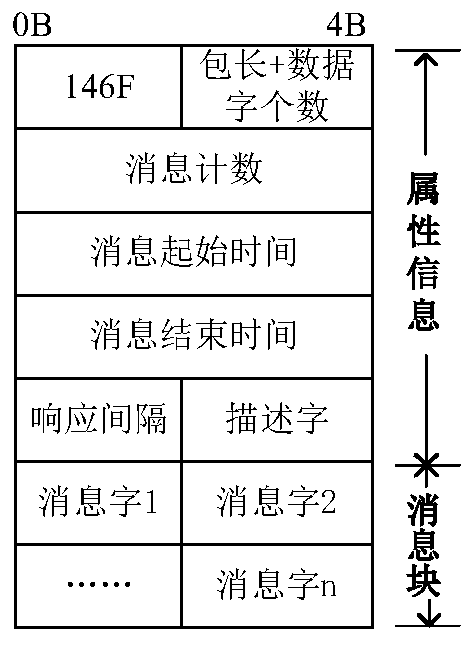

[0050] Such as figure 2 As shown, MT is the main module. MT receives bus messages through 1553B bus transceivers, adds attribute information to each message after processing, and packs and stores them in FIFO. The functions of each unit are as follows:

[0051] (1) Configuration unit: It includes the configuration of the AXI bus slave module, HPI-AXI bridge conversion, and provides interrupt feedback and read interface.

[...

Embodiment 2

[0085] Embodiment 2 of the present invention provides a kind of 1553B bus monitoring system that comprises above-mentioned IP core, and this system also includes the control module that runs on the host computer; Also includes on the described IP core: AXI bus transfer;

[0086] The AXI bus transfer on the FPGA is the communication connection module, which can read the messages in the FIFO and read back the stored data. The communication connection module adds functions such as system-on-chip protocol interface on the basis of the main module. The control module is used to control the start and end of the work of the main module, read the stored 1553B bus information, and complete the docking communication with the CPU.

[0087] In this communication interface design, the control signal sent by the upper computer is sent and received through the HPI interface, and the information is transferred through the HPI to AXI bridge to realize the control of the IP core. The upper comp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More