Carbon nanotube three-dimensional fin transistor and preparation method thereof

A fin transistor and carbon nanotube technology, applied in the field of carbon nanotube three-dimensional fin transistor and its preparation, can solve the difficulty of field effect transistors to continue Moore's law, the rise of off-state current of logic devices, the increase of sub-threshold swing, etc. problem, to achieve the effect of reducing short channel effect, ensuring driving energy, and increasing density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

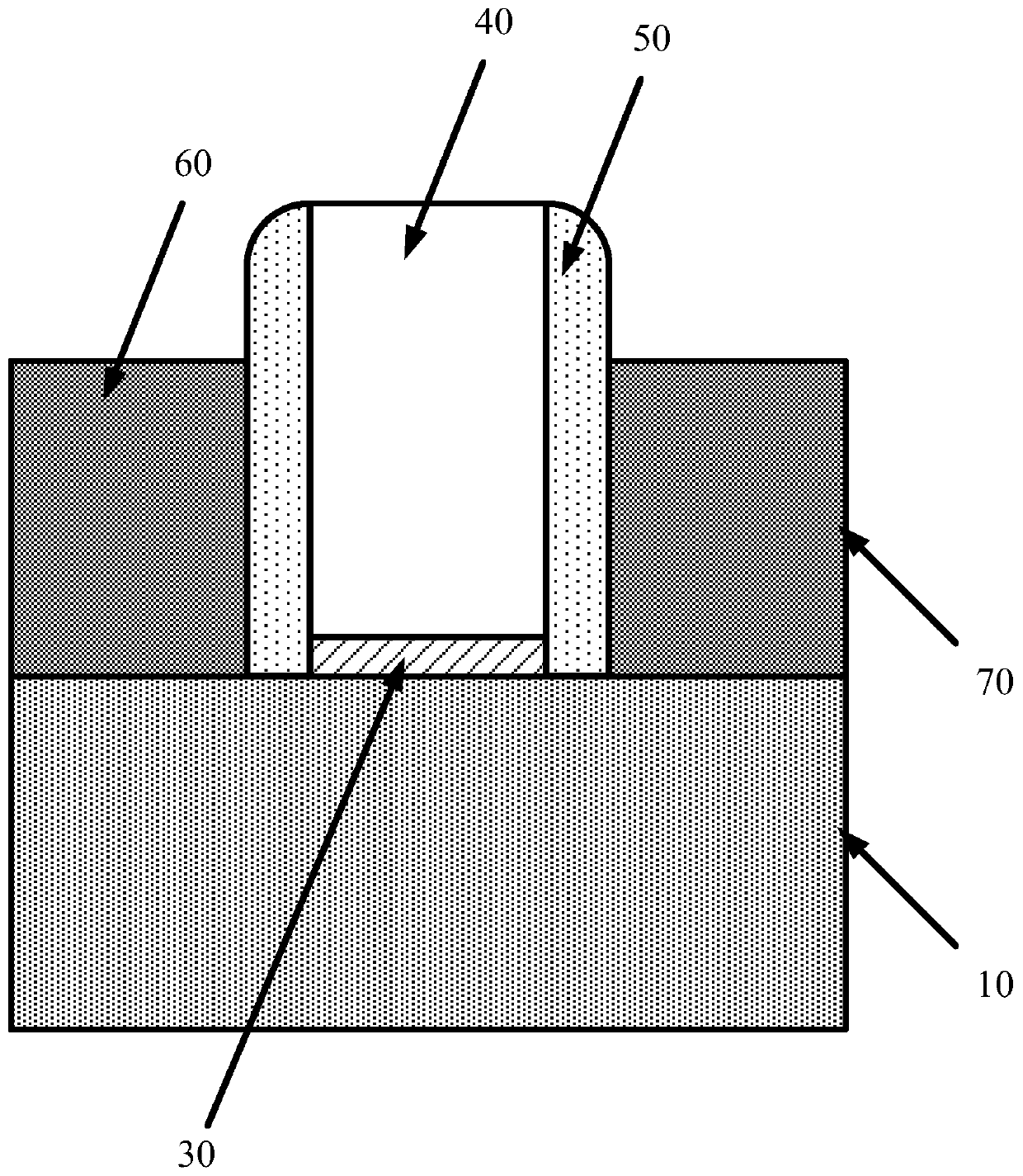

[0030] As described in the background technology, the traditional two-dimensional field effect transistor with two-dimensional structure has become more and more difficult to continue Moore's law. Therefore, the three-dimensional structure field effect transistor (Fin Field Effect Transistor (FinField -Effect Transistor, FinFET)) came into being, the channel of the three-dimensional field effect transistor is located in the protruding fin, this design can improve circuit control and reduce leakage current, and can shorten the gate length of the transistor, which is beneficial to Reduce transistor size.

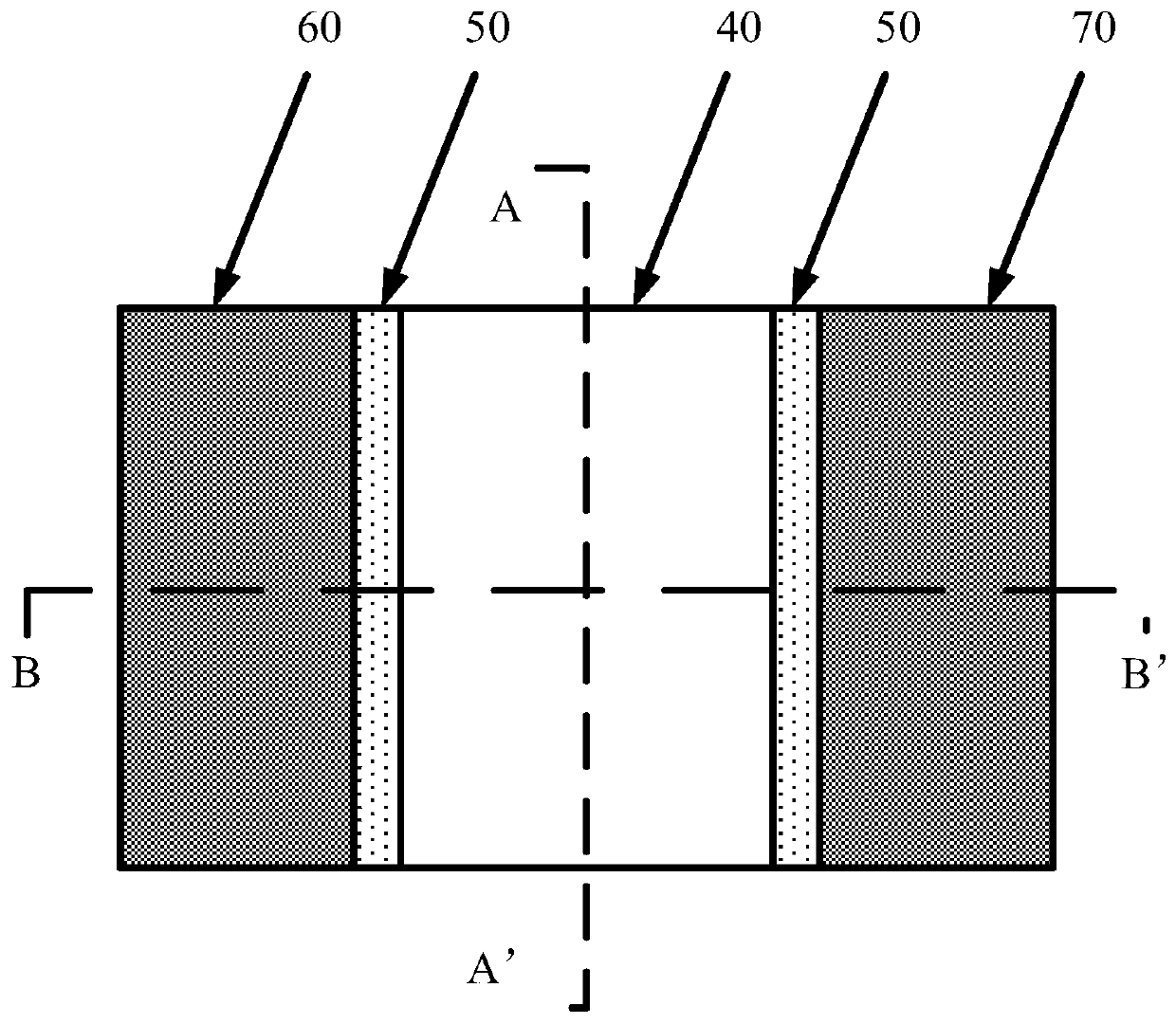

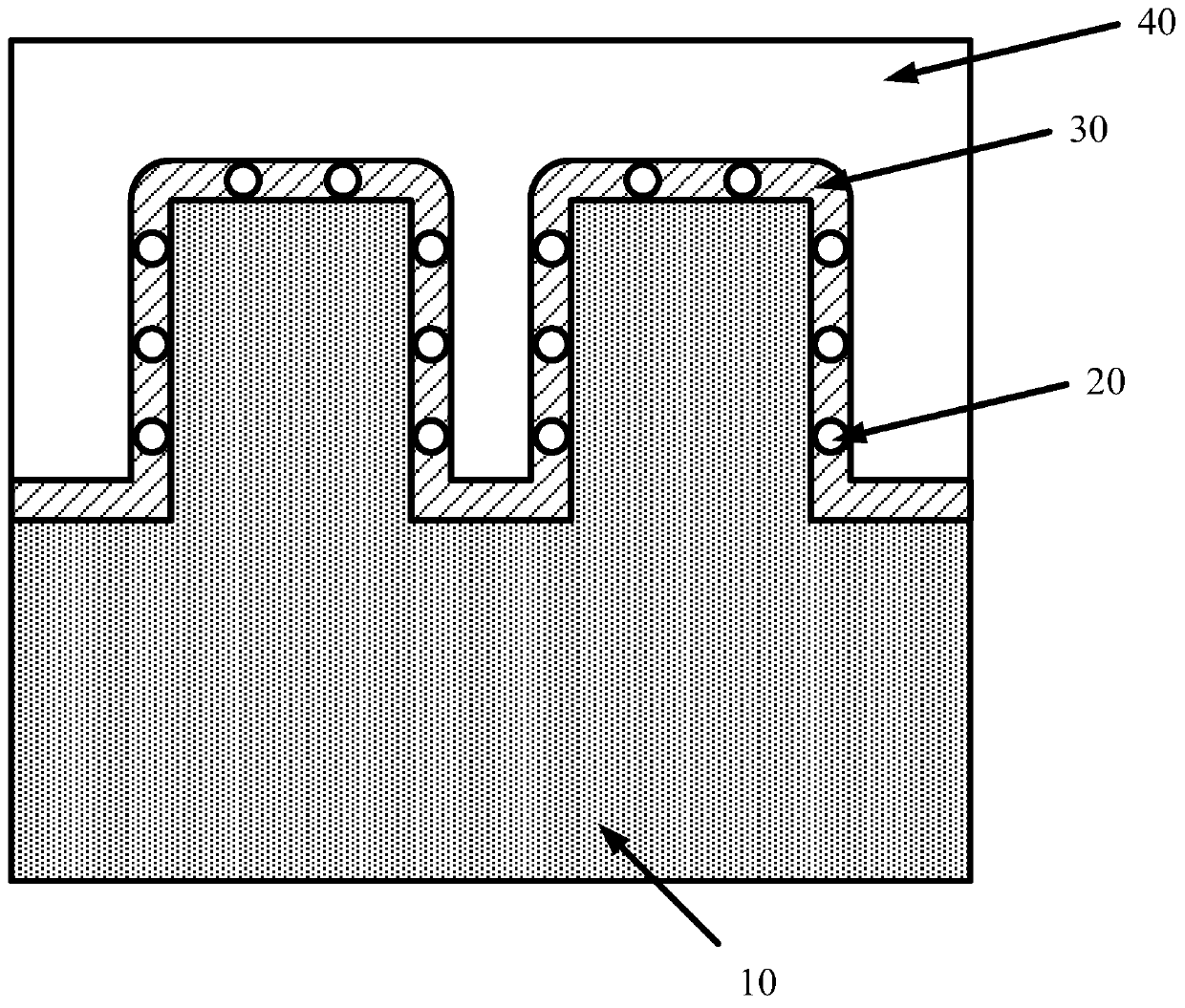

[0031] In order to further improve the gate efficiency and drive current of the field effect transistor channel, refer to Figure 1-3 , a carbon nanotube three-dimensional fin transistor with a three-dimensional structure and using carbon nanotubes (Carbon Nanotubes) as a channel came into being, Figure 1-Figure 3 shows the general structure of this carbon nanotube 3D fin tr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More