Integrated power semiconductor device and manufacturing method thereof

A semiconductor and success rate technology, applied in the field of integrated power semiconductor devices and their manufacturing, which can solve the problems of excessive chip leakage current and low manufacturing cost.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

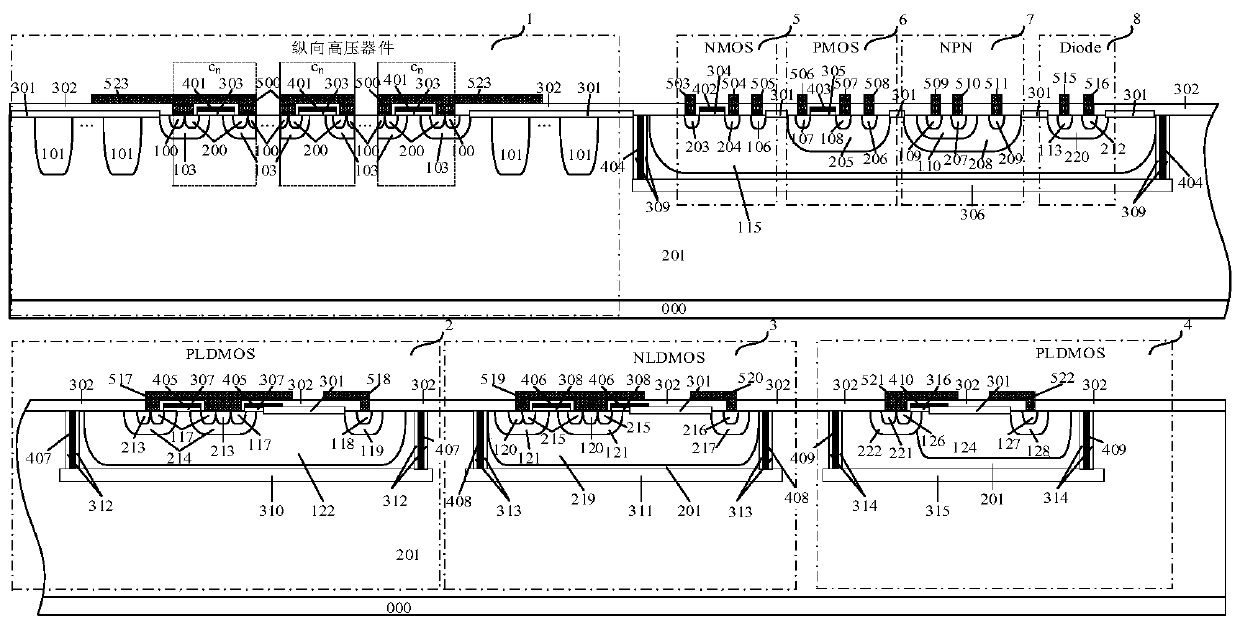

Embodiment 1

[0122] Such as figure 1 As shown, an integratable power semiconductor device includes a vertical high-voltage device 1, a first high-voltage pLDMOS device 2, a high-voltage nLDMOS device 3, a second high-voltage pLDMOS device 4, a low-voltage NMOS device 5, and a low-voltage PMOS device integrated on the same chip. 6. Low-voltage NPN device 7 and low-voltage Diode device 8, the first high-voltage pLDMOS device 2, high-voltage nLDMOS device 3, second high-voltage pLDMOS device 4, low-voltage NMOS device 5, low-voltage PMOS device 6, low-voltage NPN device 7 and low-voltage Diode Dielectric isolation is used between the devices 8 to realize complete isolation of high-voltage devices and low-voltage devices. The first high-voltage pLDMOS device 2 and the high-voltage nLDMOS device 3 adopt a multi-channel design, and the second high-voltage pLDMOS device 4 adopts a single-channel design;

[0123] The vertical high voltage device 1 includes a substrate 000, a second conductivity ty...

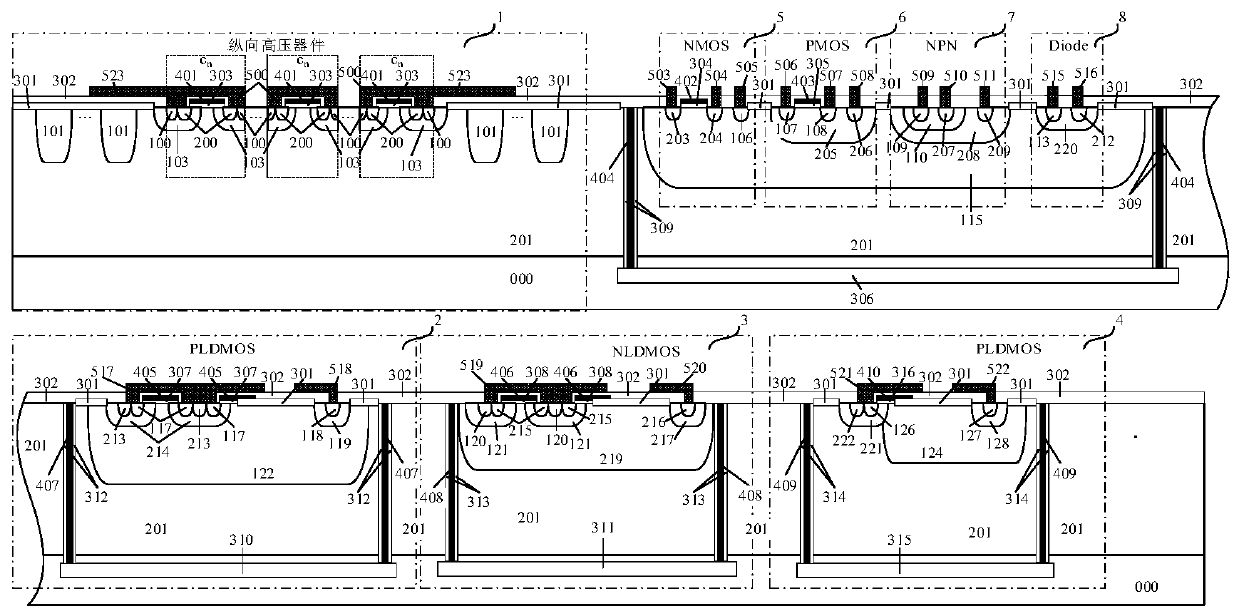

Embodiment 2

[0135] Such as figure 2 As shown, the difference between this embodiment and Embodiment 1 is that the first oxygen injection layer 306 , the second oxygen injection layer 310 , the third oxygen injection layer 311 and the fourth oxygen injection layer 315 are located inside the substrate 000 .

[0136] Such as Figure 17 As shown, the manufacturing method of the integrated power semiconductor device of this embodiment includes the following steps:

[0137] The first step is to use substrate 000;

[0138] In the second step, a certain amount of oxygen ions is implanted into the substrate 000 by photolithography and ion implantation;

[0139] The third step is annealing to form the first oxygen injection layer 306, the second oxygen injection layer 310, and the third oxygen injection layer 311;

[0140] The fourth step is to epitaxially form the epitaxial layer 201 of the second conductivity type;

[0141] The fifth step is to form a dielectric groove by using a deep groove...

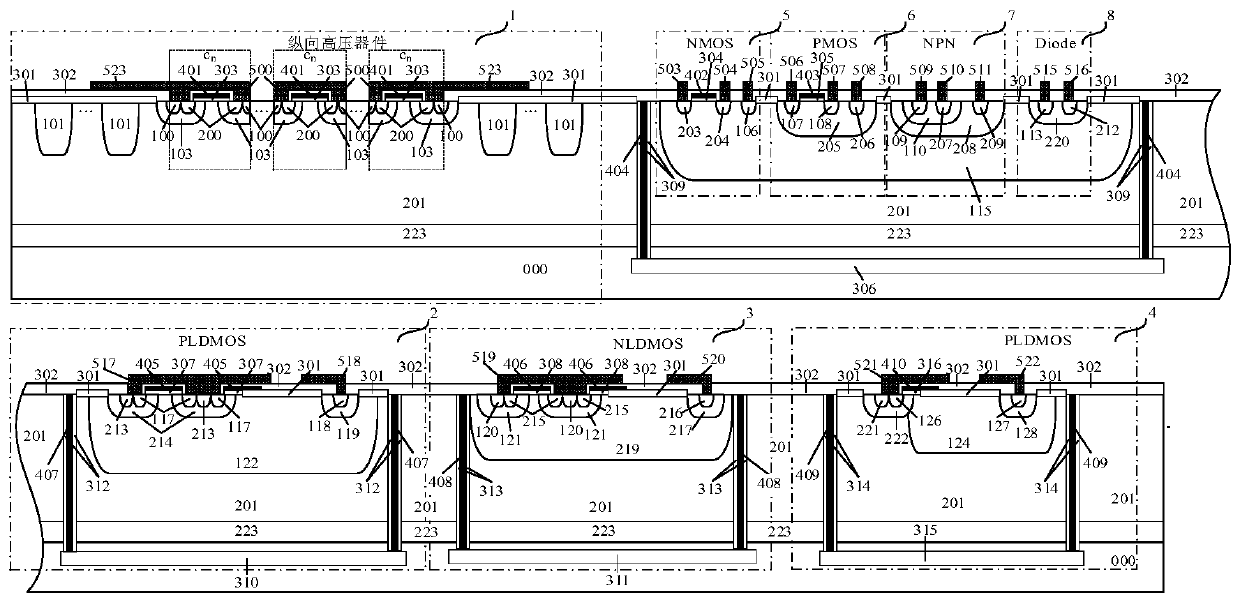

Embodiment 3

[0149] Such as image 3 As shown, the difference between this embodiment and Embodiment 2 is that: in the vertical high voltage device 1 , a field resistance layer 223 of the second conductivity type is inserted between the substrate 000 and the epitaxial layer 201 of the second conductivity type.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More