A stacking packaging process for semiconductor devices and semiconductor devices

A packaging process and semiconductor technology, applied in the direction of electrical components, impedance networks, etc., can solve problems such as complex wiring, sensitive injection molding pressure, and high cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] The application will be further described in detail below with reference to the drawings and embodiments. It can be understood that the specific embodiments described here are only used to explain the related invention, but not to limit the invention. In addition, it should be noted that, for ease of description, only the parts related to the relevant invention are shown in the drawings.

[0040] It should be noted that the embodiments in this application and the features in the embodiments can be combined with each other if there is no conflict. Hereinafter, the present application will be described in detail with reference to the drawings and in conjunction with embodiments.

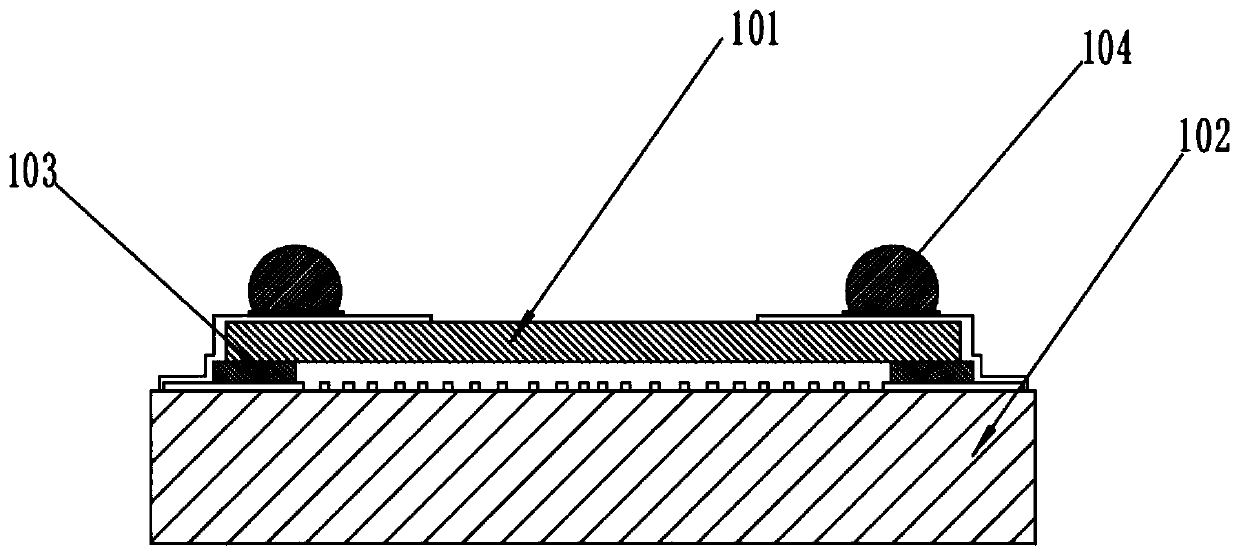

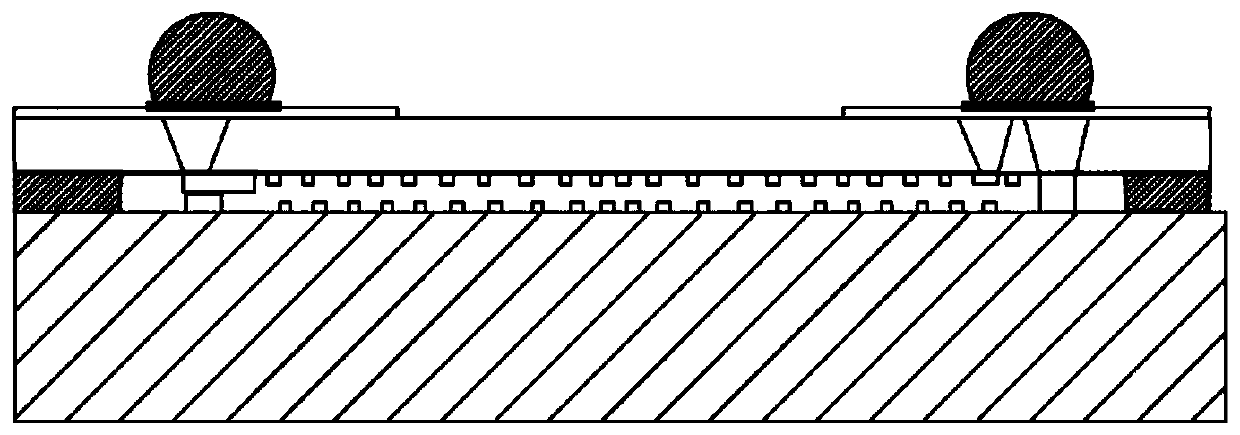

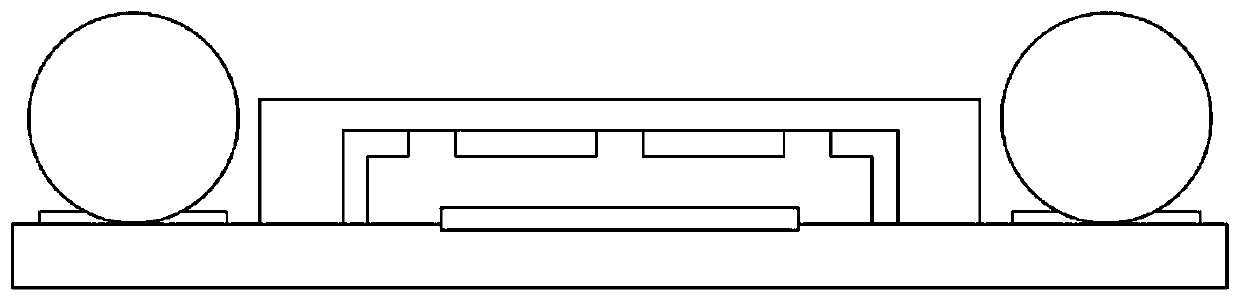

[0041] Figure 1a with Figure 1b It shows a schematic diagram of a WLP wafer-level packaging filter in the prior art using a wafer bonding packaging structure. There are two main structures and processing methods for filters using wafer bonding packages, such as Figure 1a The first structure shown ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More