Simulation method, device and related equipment of pcie initialization process

A simulation method and technology of a simulation device are applied in the simulation field of the PCIe initialization process, which can solve the problems of time-consuming, long time, or even several days, and achieve the effect of shortening the simulation time, ensuring the correctness, and avoiding the phenomenon of multiple iterations.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

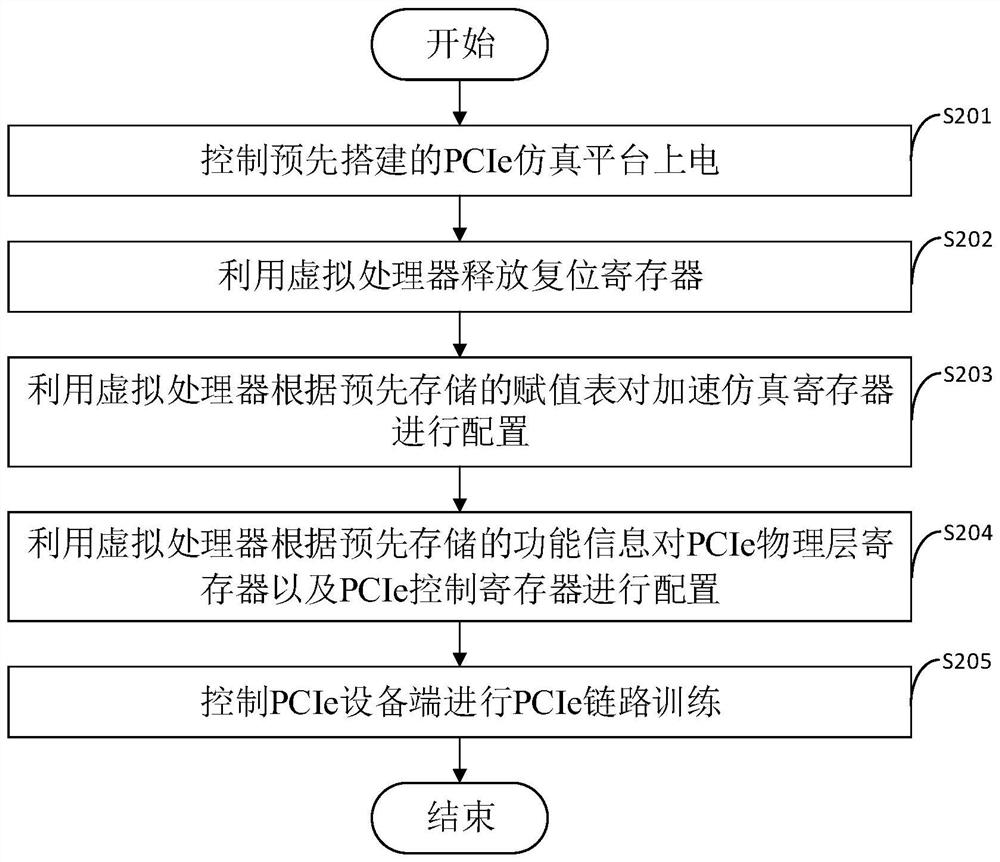

[0045] The present invention provides a method for simulating a PCIe initialization process, which is applied to the above-mentioned electronic device 100 for simulating the PCIe initialization process. see figure 2 , is a flow chart of the simulation method of the PCIe initialization process provided by the present invention. The simulation method of the PCIe initialization process includes:

[0046] S201, controlling the pre-built PCIe simulation platform to be powered on.

[0047] Understandably, EDA simulation software is pre-installed on the electronic device 100 . The simulation software may be modelsim. Developers can use EDA software for electronic circuit design, PCB design, and IC design. Generally, EDA simulation can perform pre-simulation and post-simulation according to the type of the design to be verified (Design Under Test, DUT). Among them, the pre-simulation is the simulation based on RTL, and the post-simulation is the simulation based on the netlist. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More